# The ATLAS Pixel Sensor — properties, characterization and quality control

Dissertation zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften im Fachbereich Physik der Universität Dortmund

vorgelegt von Dipl.-Phys. Jonas M. Klaiber-Lodewigs aus Tübingen

June 2005

## **Abstract**

The planning, construction and commissioning of multi-purpose physics detectors for the LHC proton-proton collider at CERN poses new challenges to the involved institutes regarding scientific, technological and organizational aspects of the process. In the case of the central vertex tracking systems, very complex assemblies have to be produced in large numbers and integrated into a device reliable enough to function for a planned experimental lifetime of at least ten years and in a radiation environment up to doses of several hundred kGy and fluences well above 10<sup>14</sup> (1 MeV neutron equivalents)/cm<sup>2</sup> for the innermost parts of the tracking system. A quality assurance plan has to be implemented to ensure high quality of all parts according to the necessary performance parameters. define technical specifications accordingly and provide a good understanding of particle-detector interaction and the physical properties of the detector to extrapolate detector behaviour during the experiment. This thesis gives a detailed overview of the motivation, physics and organizational aspects and results of the quality assurance program for the silicon sensor used in the pixel subdetector for the ATLAS multi-purpose experiment. The sensor design used is shown to be well suitable for assembly and long term operation within the ATLAS experiment, and the quality plan implemented for sensor production has proven highly indicative for monitoring crucial aspects of sensor quality. In addition, problems within sensor production could be pinpointed at an early stage and further insights into the physical properties of sensors and parameters of their operation could be gained.

# **Contents**

| Ab  | strac              | ct                                                                                                                                                                                                      | iii                                      |  |  |  |

|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--|--|--|

| Ta  | ble o              | of contents                                                                                                                                                                                             | v                                        |  |  |  |

| Lis | ist of figures vii |                                                                                                                                                                                                         |                                          |  |  |  |

| Lis | ist of tables ix   |                                                                                                                                                                                                         |                                          |  |  |  |

| 1   | Intro              | oduction                                                                                                                                                                                                | 1                                        |  |  |  |

| 2   | <b>ATL</b> 2.1 2.2 | ATLAS pixel subdetector  2.1.1 ATLAS experiment  2.1.2 ATLAS detector layout  2.1.3 Pixel detector concept  2.1.4 Pixel detector module  Pixel sensor design  2.2.1 Sensor concept  2.2.2 Pixel design  | 3<br>3<br>6<br>8<br>10<br>14<br>14<br>18 |  |  |  |

| 3   | Plan<br>3.1        | Quality plan concept                                                                                                                                                                                    | 21<br>22<br>23<br>27                     |  |  |  |

|     | 3.2                | Choosing sensor characteristics                                                                                                                                                                         | 29<br>33<br>36<br>40                     |  |  |  |

|     | 3.3<br>3.4         | Development of test structures  Testing procedures  3.4.1 Devices and set-ups  3.4.2 Measurement settings  3.4.3 Dust, humidity and temperature  3.4.4 Part identification  3.4.5 Shipping and handling | 46<br>52<br>52<br>54<br>56<br>59<br>60   |  |  |  |

| 4   |                    | ults of quality testing                                                                                                                                                                                 | 63                                       |  |  |  |

|     | 4.1 4.2            | Consideration of errors                                                                                                                                                                                 | 63<br>64<br>66<br>67<br>71               |  |  |  |

#### Contents

|    |              | 4.3.1   | Sensor tile current sweeps                              | . 75  |

|----|--------------|---------|---------------------------------------------------------|-------|

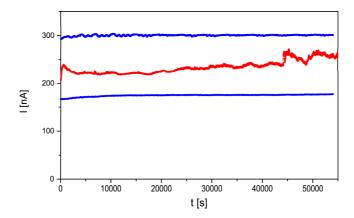

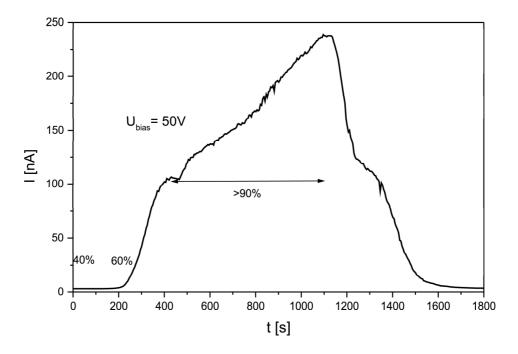

|    |              | 4.3.2   | Current stability in sensors                            | . 78  |

|    |              | 4.3.3   | Current sweeps on test devices                          | . 81  |

|    |              | 4.3.4   | Depletion behaviour                                     | . 86  |

|    | 4.4          | Interfa | ace characteristics                                     | . 91  |

|    |              | 4.4.1   | Oxide breakdowns and surface currents                   |       |

|    |              | 4.4.2   | Flat band capacitance and interface generation currents |       |

|    |              | 4.4.3   | P-spray dose in the MOSFET                              |       |

|    |              | 4.4.4   | P-spray behaviour in the bias dot                       |       |

|    |              | 4.4.5   | Other layer characteristics                             |       |

|    | 4.5          | Logist  | ics issues                                              |       |

|    |              | 4.5.1   | Transport and handling problems                         |       |

|    |              | 4.5.2   | Data management                                         | . 118 |

| 5  | Asse         | essmen  | t of relevance                                          | 121   |

| _  | 5.1          | Qualit  | y assurance                                             | . 121 |

|    | 5.2          |         | characteristics                                         |       |

|    | 5.3          |         | tion tolerance                                          |       |

|    |              |         |                                                         |       |

| 6  | Sum          | ımary   |                                                         | 125   |

| Α  | Арр          | endix A | A: Physical constants                                   | 127   |

| В  | Арр          | endix E | 3: Abbreviations                                        | 129   |

| Bi | Bibliography |         |                                                         | 131   |

| Th |              |         |                                                         |       |

# **List of Figures**

| 2.1  | Geographical layout of the LHC ring                                               | . 3  |

|------|-----------------------------------------------------------------------------------|------|

| 2.2  | The LHC tunnel excavation including caverns for experiments                       |      |

| 2.3  | Simulated event display of a decaying Higgs boson                                 |      |

| 2.4  | Simulated event display showing three hadronic jets                               | . 5  |

| 2.5  | Overall set-up of the ATLAS subdetector systems                                   | . 7  |

| 2.6  | Layout of the ATLAS inner detector subsystems                                     | . 7  |

| 2.7  | Cut-away view of the ATLAS Pixel subdetector                                      |      |

| 2.8  | Components and assembly structure of the ATLAS pixel module                       |      |

| 2.9  | Three-dimensional model of the ATLAS pixel module                                 |      |

| 2.10 | <del>-</del>                                                                      |      |

| 2.11 |                                                                                   |      |

|      | Signal clusters within a magnetic field for different incidence angles            |      |

|      | Cluster size dependency on incidence angle                                        |      |

|      | Parameterization of radiation damage and annealing effects                        |      |

|      | Comparison of effects of proton irradiation in standard and oxygenated silicon    |      |

|      | Comparison of annealing times in standard and oxygenated silicon                  |      |

|      | Effective charge densities in standard and oxygenated silicon after irradiation   |      |

|      | Change of voltage necessary for full depletion of sensors                         |      |

|      | Comparison of $p^+$ -in-n and $n^+$ -in-n pixel sensors                           |      |

|      | Comparison of inter pixel isolation technologies                                  |      |

| 3.1  | Illustration of the 'Rule of Tens' in industrial production                       | . 23 |

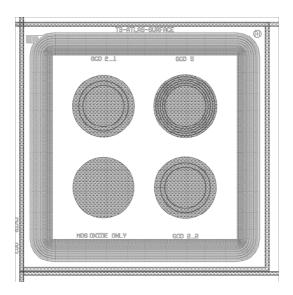

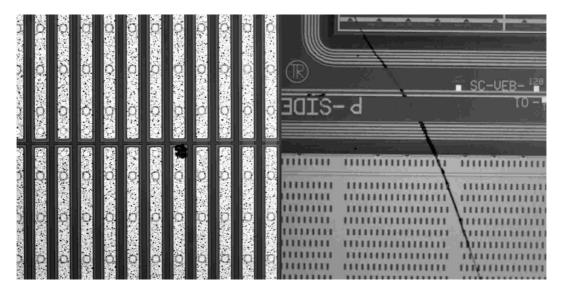

| 3.2  | Production wafer seen from the n-side and the p-side                              |      |

| 3.3  | Map of wafer p-side with numbered structures                                      | . 26 |

| 3.4  | Flow of quality testing                                                           |      |

| 3.5  | Information feedback for sensor quality optimization                              |      |

| 3.6  | Section showing planned orientation of barrel modules                             |      |

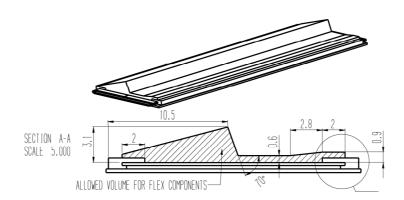

| 3.7  | Planned module envelope for the pixel sensor set-up                               |      |

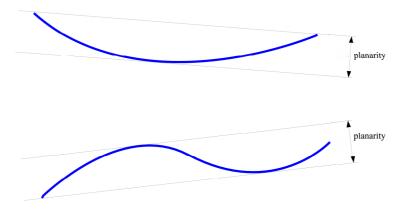

| 3.8  | Definition of planarity value simplified to two dimensions                        |      |

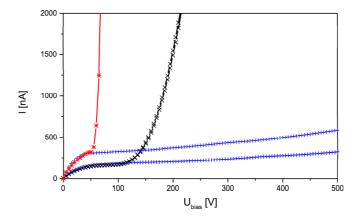

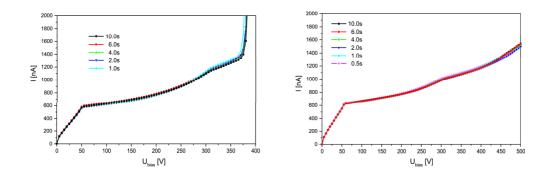

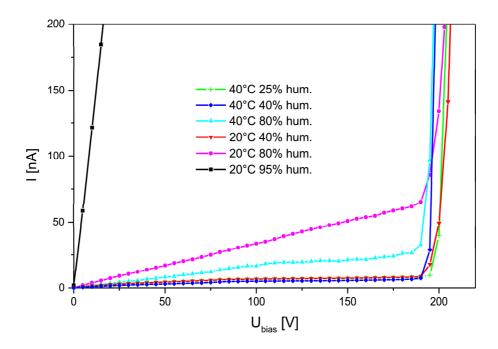

| 3.9  | Current vs. bias curves from various sensor tiles                                 |      |

| 3.10 |                                                                                   |      |

| 3.11 |                                                                                   |      |

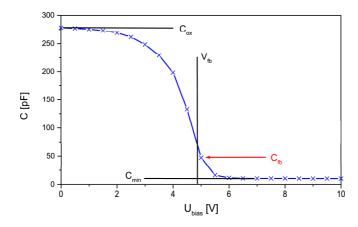

| 3.12 | Capacitance vs. bias curve on a MOS test device                                   |      |

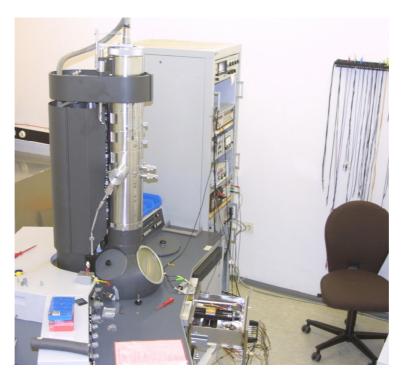

|      | The Dortmund electron irradiation facility DEBE                                   |      |

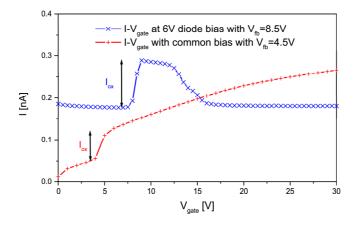

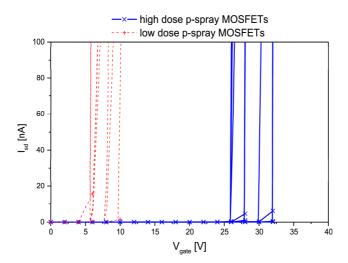

|      | Examples of current vs. $V_{aate}$ curves measured with different biasing set-ups |      |

|      | Measurements of source-drain currents of MOSFETs with different p-spray doses .   |      |

| 3.16 | Layout detail of the bias grid                                                    | . 46 |

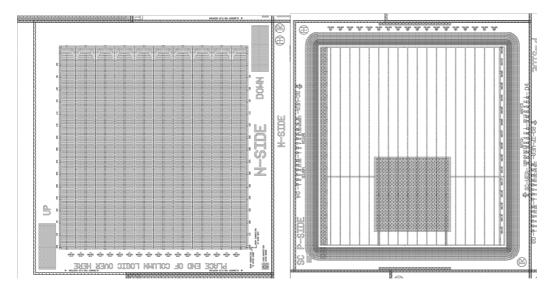

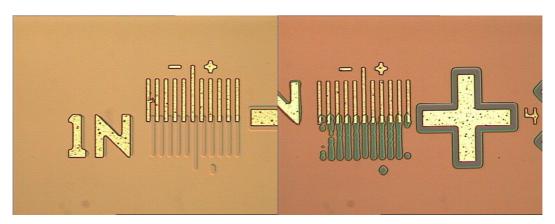

|      | n-side and p-side mask of a single chip sensor                                    |      |

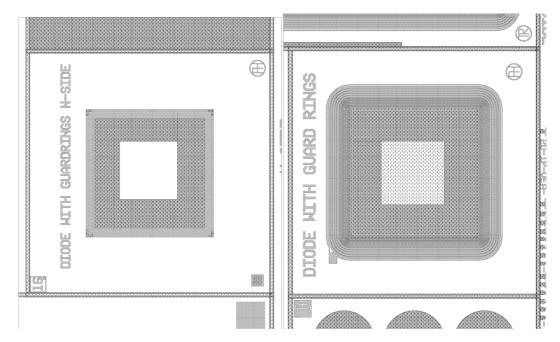

|      | n-side and p-side mask of a test diode with multi guard ring                      |      |

|      | Mask of a p-side oxide test field                                                 |      |

|      | Cut-away views of a MOS pad and a two ring GCD                                    |      |

|      | Punch through test device with 48 bias dot implantations                          |      |

|      | Cut-away view of a punch through test device                                      |      |

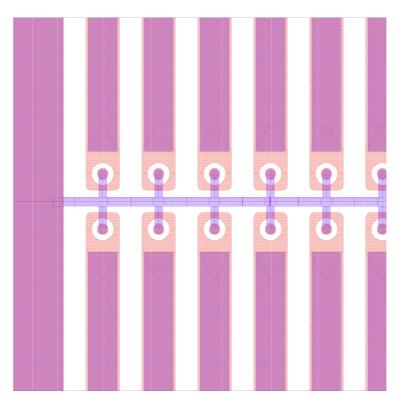

|      | Cut away view of a p-spray test MOSFET                                            |      |

## List of Figures

| $3.25 \\ 3.26 \\ 3.27$          | Custom built needle chuck and sketch of needle placement                                                                                                                                                      |   | 53<br>54<br>55<br>55       |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------------|

| 3.29<br>3.30                    | Climate chamber with set-up for wire bonded test devices                                                                                                                                                      |   | 57<br>58<br>58<br>60       |

| 4.1<br>4.2<br>4.3<br>4.4        | Particle and scratch on the wafer in the visual inspection                                                                                                                                                    |   | 64<br>65<br>66<br>67       |

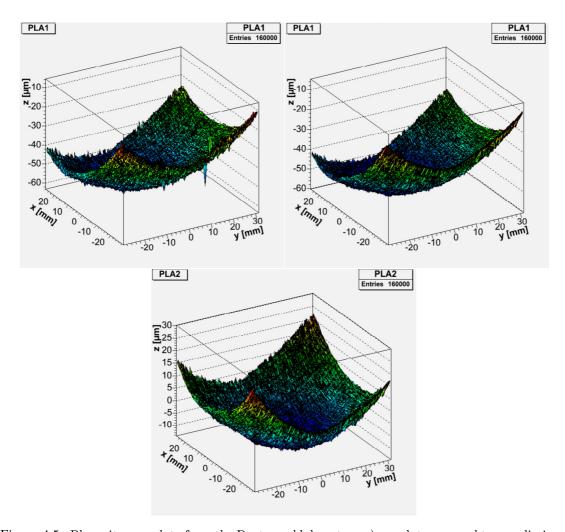

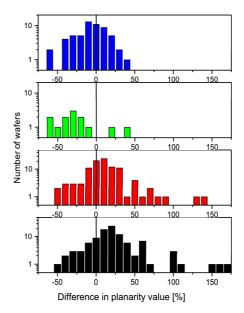

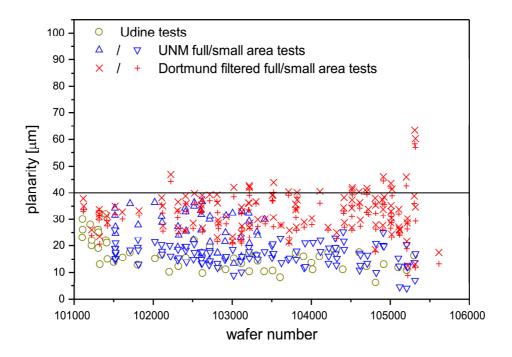

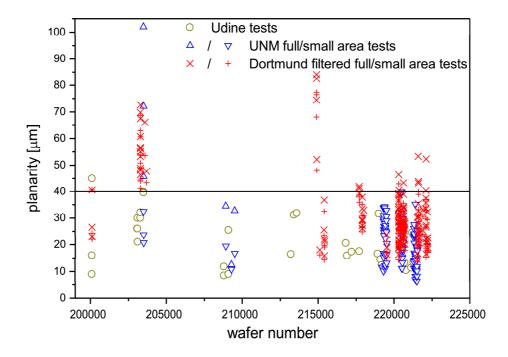

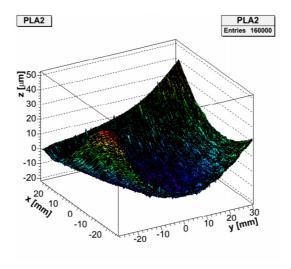

| 4.5<br>4.6<br>4.7<br>4.8<br>4.9 | Planarity scan data from the Dortmund laboratory                                                                                                                                                              |   | 69<br>70<br>71<br>72<br>73 |

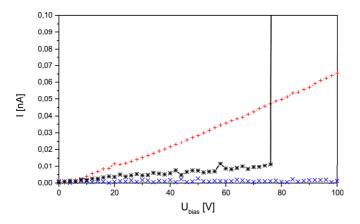

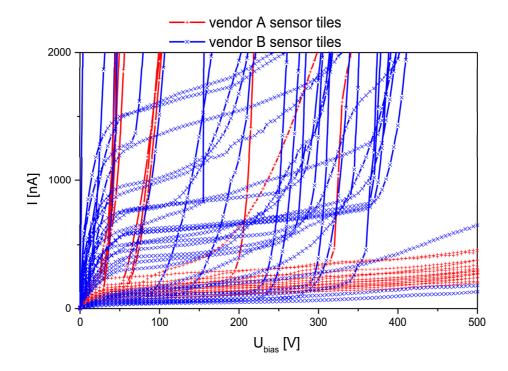

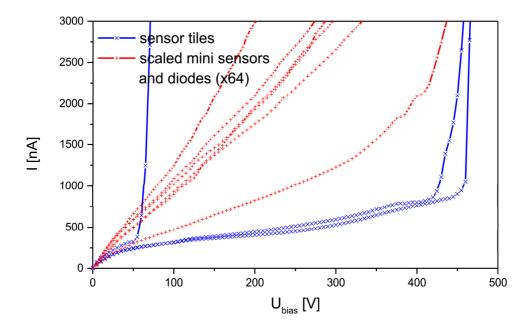

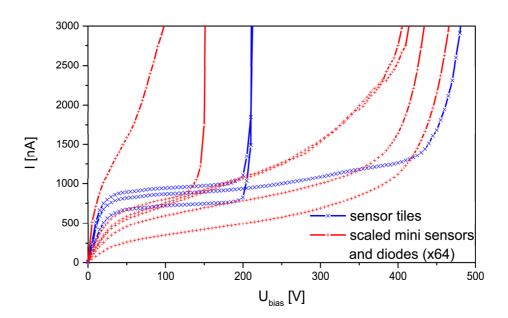

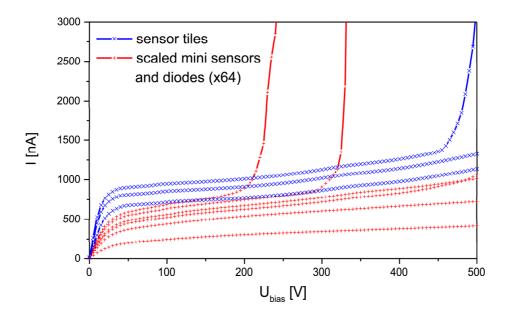

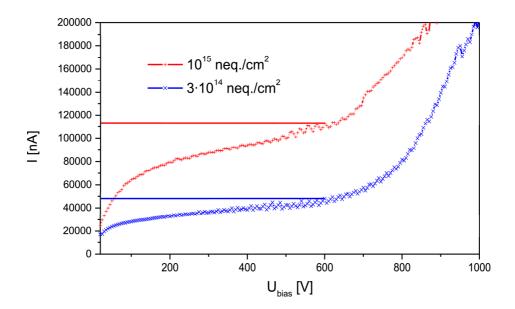

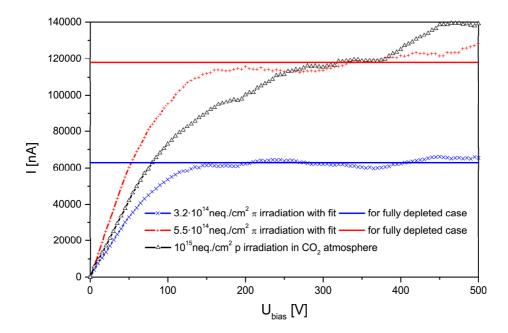

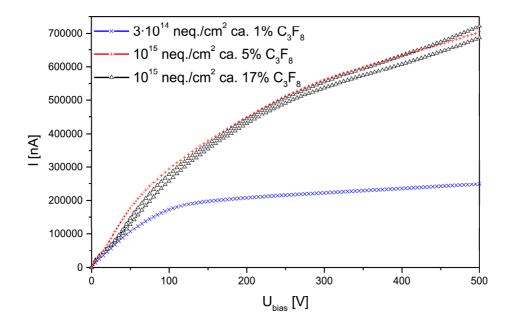

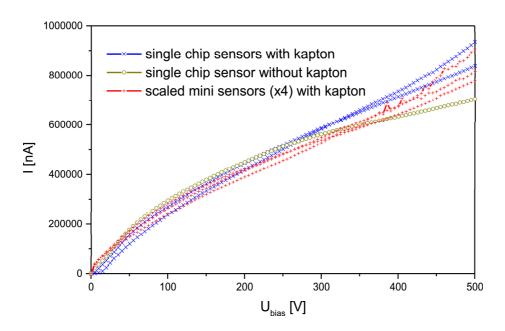

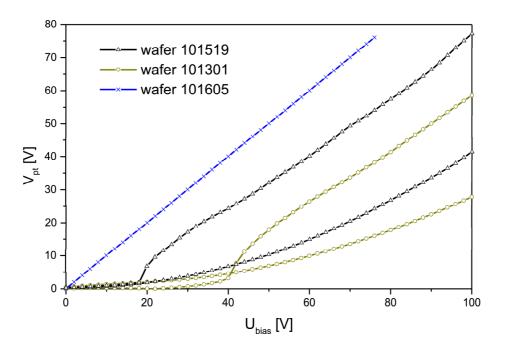

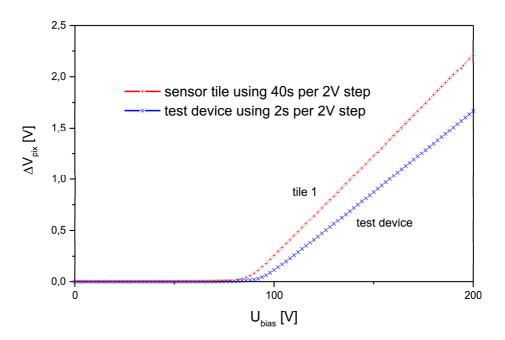

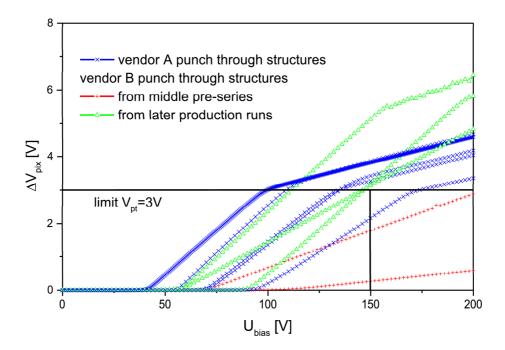

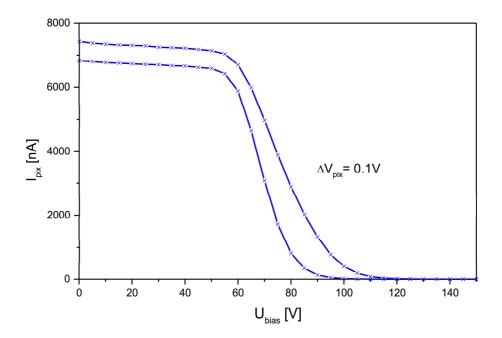

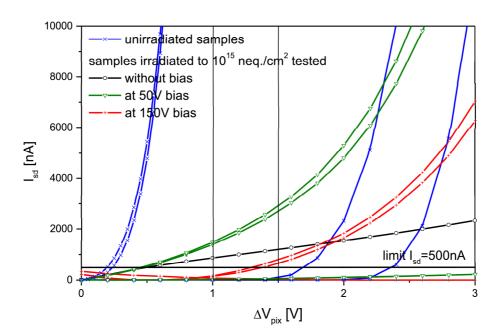

| 4.10<br>4.11<br>4.12<br>4.13    | Dark current vs. bias voltage curves on sensor tiles                                                                                                                                                          |   | 75<br>77<br>79<br>81       |

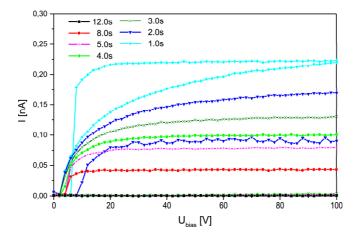

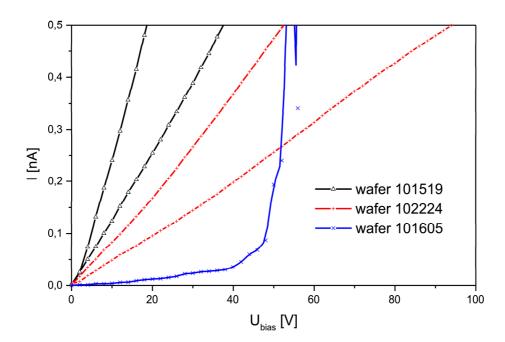

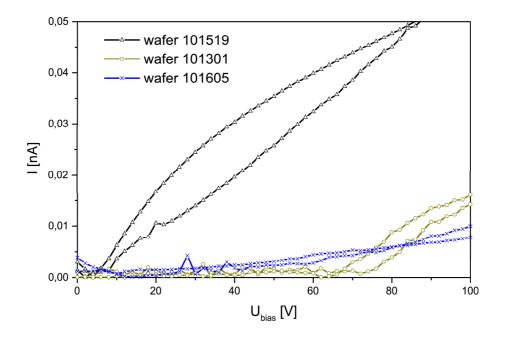

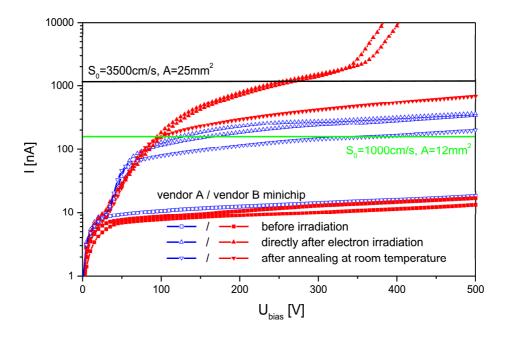

| $4.15 \\ 4.16 \\ 4.17$          | Ohmic behaviour in leakage current sweeps mini sensors                                                                                                                                                        |   | 82<br>83<br>84<br>85<br>87 |

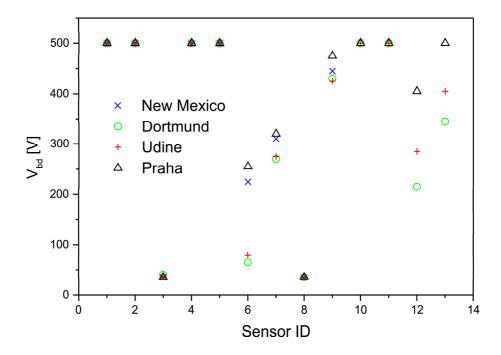

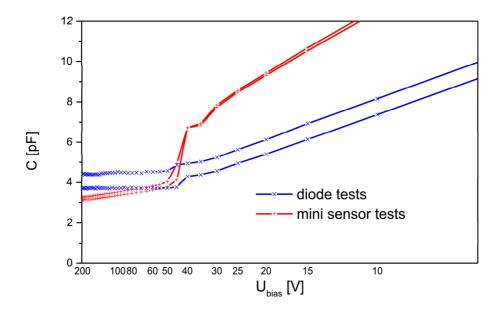

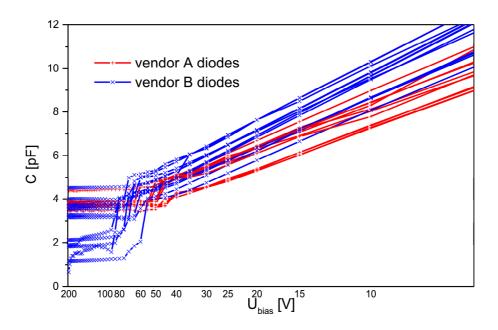

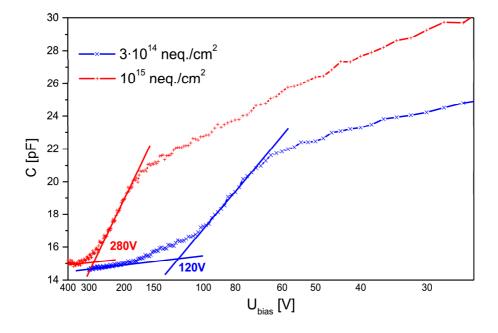

| $4.19 \\ 4.20 \\ 4.21 \\ 4.22$  | Capacitance sweeps on diodes and mini sensors                                                                                                                                                                 |   | 88<br>89<br>89<br>91       |

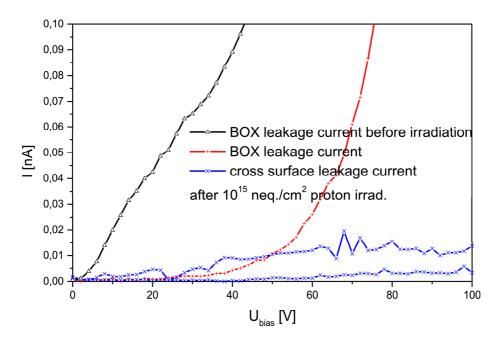

| $4.24 \\ 4.25 \\ 4.26$          | Additional tests to detect surface currents                                                                                                                                                                   |   | 92<br>93<br>96<br>97       |

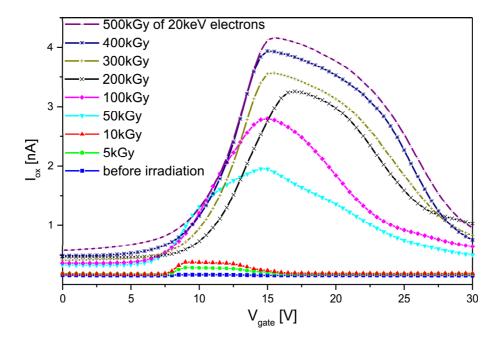

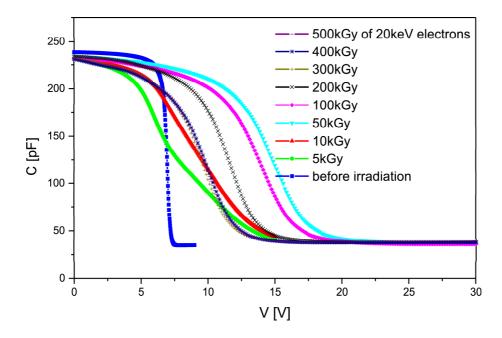

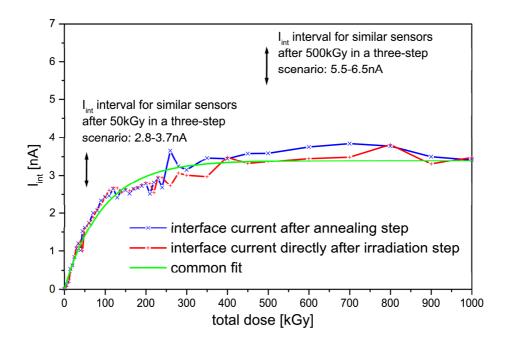

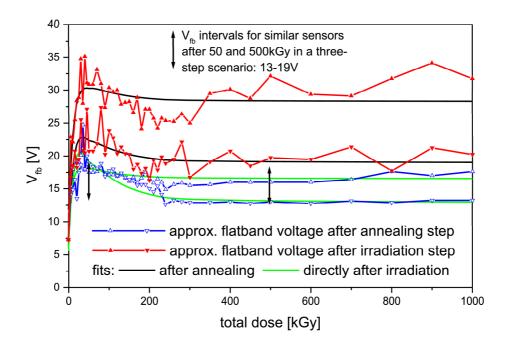

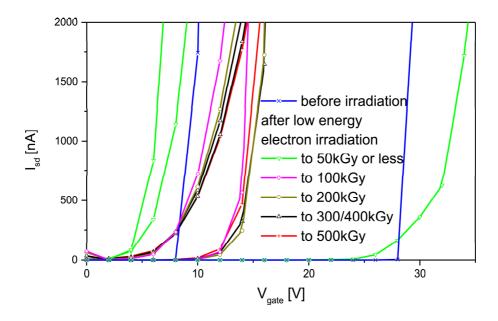

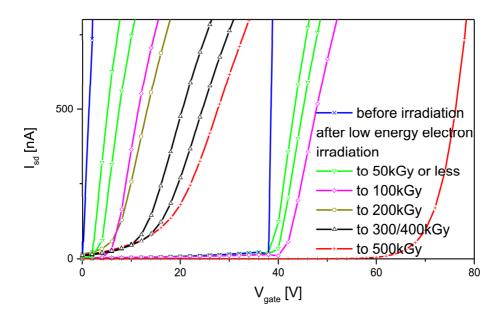

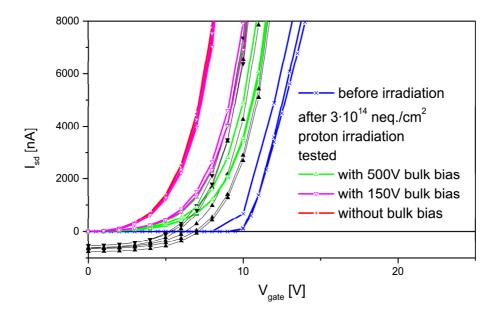

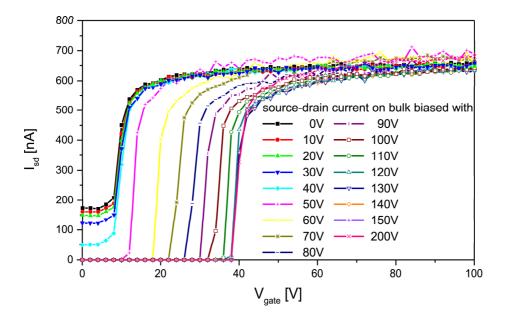

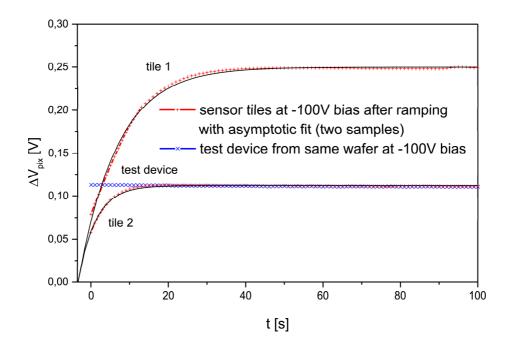

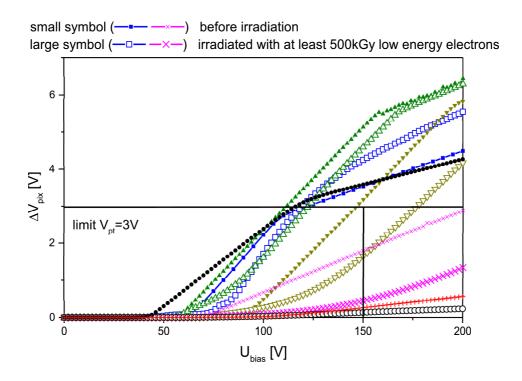

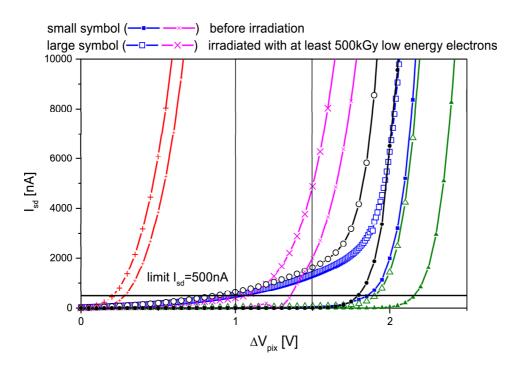

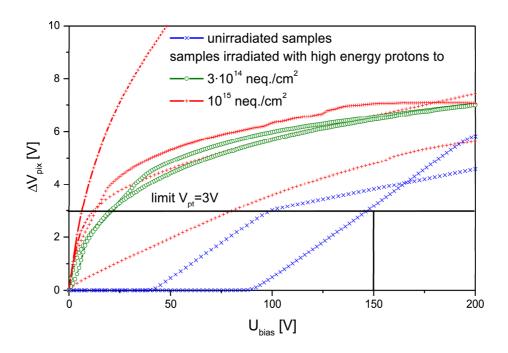

| 4.28 $4.29$ $4.30$              | Development of test field characteristics during incremental electron irradiation Source-drain current tests on electron irradiated MOSFET structures Source-drain current tests on proton irradiated MOSFETs | • | 105                        |

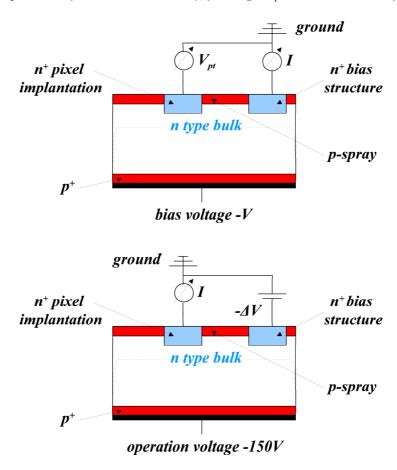

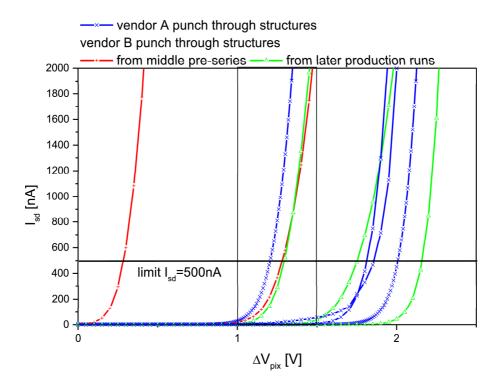

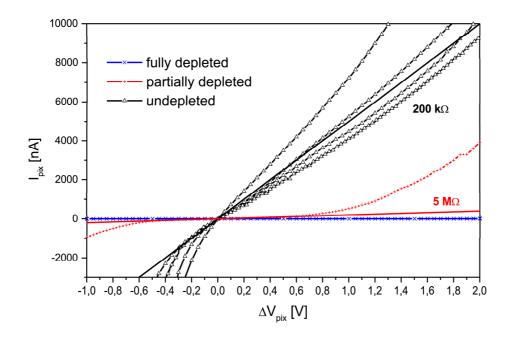

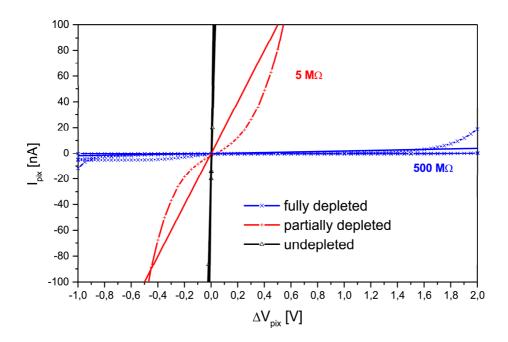

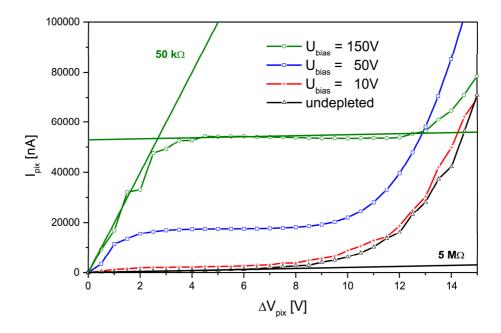

| 4.32 $4.33$ $4.34$              | Sweeps of voltage drop between bias grid and implantations vs. bias voltage Measurement set-ups for different tests on punch through devices                                                                  |   | 107<br>108<br>109          |

| $4.36 \\ 4.37 \\ 4.38$          | Tests on punch through structures before and after electron irradiation Tests on punch through structures before and after proton irradiation Inter pixel current sweeps between unirradiated double pixels   |   | 111<br>113<br>115          |

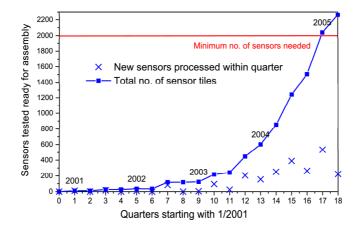

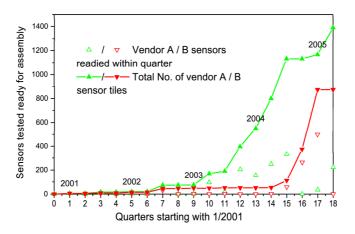

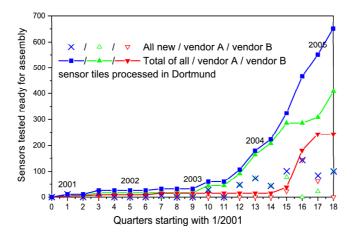

| 5.1                             | Sensor tile output statistics in sum and per quarter                                                                                                                                                          | • | 122                        |

| T.1                             | Less serious achievements during the work on this thesis                                                                                                                                                      |   | 136                        |

# **List of Tables**

| 3.1 | List of sensor qualities tested for        | 33  |

|-----|--------------------------------------------|-----|

| A.1 | Physical constants used within this thesis | 127 |

| В.1 | Abbreviations used within this thesis      | 130 |

List of Tables

# 1 Introduction

During the second half of the twentieth century experimental particle physics has seen an astonishing development, yielding insights into the properties of subatomic particles on increasingly smaller distances and higher energy scales, and has helped to find and confirm the so-called standard model of particle physics explaining the electromagnetic and weak nuclear interaction (formulated as a common electroweak interaction) and the strong nuclear interaction and all their constituents within a framework consistent with relativistic dynamics. The experimental breakthroughs have been made possible by a series of developments concerning accelerator and detector physics, as well as the increase in easily affordable computing power and significant organizational changes in the international physics community.

Two of these defining trends in experimental particle physics are central to this thesis, the development of micro vertex detectors for particle collider experiments, designed to allow for the reconstruction of particle tracks back to possible secondary vertices and the improved indirect identification of low lifetime primary particles, and the formation of increasingly larger collaborations, able to construct and maintain increasingly bigger and more complex detector systems, incorporating a large amount of high quality parts. These developments have led to the construction of intricate tracking systems to be installed very close to the experimental interaction point, now mostly consisting of layered semiconductor tiles, finely segmented to optimize spatial resolution. Some efforts are necessary to construct a complex and accurate subdetector to be put in a location close to the interaction point of the experiment and thus subject to high radiation levels and hardly accessible for later maintenance. Among these are the projection of behaviour throughout the lifetime of the experiment and the exact monitoring of the detector production to assure the full long-term functionality of the tracking system. This has to be based on a good knowledge of the characteristics of all detector parts when assembled and of changes in behaviour caused by irradiation. This is the basic description of the aim of a quality assurance plan for a particle physics detector or subdetector, in this case for the sensor tiles of the ATLAS pixel detector.

The aim of the work presented in this thesis has been the formulation and implementation of a quality plan specifically for the silicon sensors of the pixel detector. From a scientific point of view this includes choosing sensor parameters and tests representative of sensor functionality in operation, verifying the adequacy of the chosen sensor concept and manufacturers as well as demonstrating the relevance of the measured data regarding the task of quality control at hand as well as the aspects of device physics involved. To achieve this, the role of the pixel sensor within the ATLAS experiment had to be considered as well as the specific properties of the sensor design (chapter 2). Regarding the possibilities of quality assurance strategies and knowledge about the intended sensor properties, test devices have been chosen and procedures have been defined for measurements and assessment of results (chapter 3). The test data has been gathered and analyzed, often together with additional tests to clarify aspects of sensor behaviour or systematic influence of the used test set-up (chapter 4). These results are finally assessed in the context of sensor quality as well as additional information of sensor behaviour before and after irradiation, to gauge the success of the quality plan regarding its scientific aims (chapter 5).

#### 1 Introduction

# 2 ATLAS Pixel sensor

## 2.1 ATLAS pixel subdetector

#### 2.1.1 ATLAS experiment

The ATLAS experiment is one of two multi-purpose detectors planned and assembled for use at the LHC (Large Hadron Collider) proton-proton collider ring at the CERN (Centre/Conseil Européen pour la Recherche Nucléaire) site, Geneva (see figure 2.1). The main purpose of the new ring collider, constructed for proton-proton collisions up to a maximum center of mass energy of  $\sqrt{s} = 14 \, \text{TeV}$ , is the continuing research on new physics phenomena at an energy scale beyond the limit set by experiments at the electron-positron collider LEP at CERN and the proton-antiproton collider Tevatron at Fermilab, especially the verification of the existence and properties of bosons associated with the mass generating Higgs process postulated by the standard model and the test of the supersymmetric theories on the unification of the electroweak theory and quantum chromodynamics.

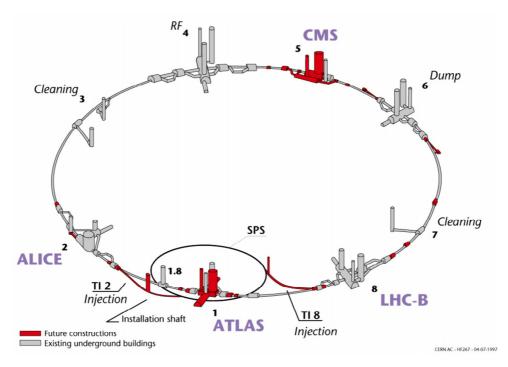

Figure 2.1: Geographical layout of the LHC ring [ATL04]

Among the four experiments to be constructed at the LHC ring, (see figure 2.2) are two specialized detector systems, ALICE for heavy ion collisions up to  $\sqrt{s} = A \cdot 2.76 \,\text{TeV}$  and LHCb for tests on CP violation in bb-systems. The remaining two experiments, ATLAS and CMS, consist of multipurpose detectors, designed to detect and resolve a wide variety of possibly interesting physics events and generate a comprehensive data set for new physics searches as well as precision analyses of known quantities.

The high design luminosity of the LHC beam focus  $(10^{34} \,\mathrm{s^{-1} \cdot cm^{-2}})$  and the bunch crossing rate of 40 MHz [LHC93] [LHC95] (one crossing per 25 ns in each general purpose experiment generating on average 23 inelastic interactions [ATL97a]) lead to the production of a vast amount of detector signal data of which the biggest portion comes from minimum bias events. These events only generate a very small transversal momentum in the particles generated by the colliding protons, producing mostly low energy pion jets, and are not of special interest for probing physical processes at high energies. This creates the opportunity to reduce the amount of event data drastically

Figure 2.2: The LHC tunnel excavation including caverns for experiments [ATL04]

without losing a comparably large portion of the information relevant for later analyses. To exploit this possibility, it is necessary to implement a trigger system capable of doing a very fast preliminary event reconstruction to effectively suppress irrelevant events and artifacts.

The main topics of the ATLAS physics program, for which detector concept and trigger performance had to be optimized are [ATL99b]:

- Searches for predicted bosons of the Higgs field, favouring coupling to heavy particles like

third generation quarks and massive bosons. In supersymmetric extensions of the standard

model more than one kind of Higgs boson is expected.

- Searches for supersymmetric partner particles of known particles.

- Searches for unknown massive gauge bosons outside the Higgs sector.

- Searches for evidence for compositeness of elementary particles, especially quarks.

- Precision measurements of masses of heavy quarks and bosons, gauge boson coupling, violation of CP symmetry, and the Cabibbo-Kobayashi-Maskawa unitarity.

The decay channels expected for events generating Higgs bosons that could be seen as resonance in the energy spectra of decay products favour states of relatively high mass particles, as the mass producing process of the Higgs mechanism should lead to a scaling of interaction probabilities with the mass of particles coupling to the Higgs boson, whether real or virtual. For Higgs boson masses  $m_H$  with  $120 \,\mathrm{MeV} \leq m_H < 2 \cdot m_Z$  this leads to a high expected incidence of ZZ production with one virtual boson (called ZZ\* or off-shell production) or for  $m_H \geq m_Z$  with two real bosons. This combination can lead to two-lepton/antilepton pair endstates (see figure 2.3), among them a very distinctive, although not highly favoured double muon-antimuon states without missing energy, whose tracks can be detected and whose energy can be reconstructed by using a dedicated muon detector enclosing a significant volume around the interaction point containing a high and well characterized magnetic field.

The favoured expected hadronic decay channel of the Higgs boson is the production of a bbquark-antiquark pair, as this is the heaviest quark carrying less mass than half the expected  $m_H$ .

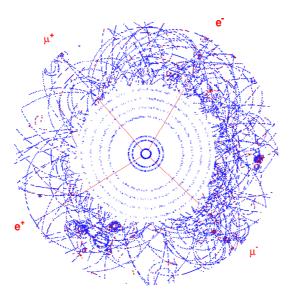

# ATLAS Barrel Inner Detector $H \rightarrow ZZ^{'} \rightarrow \mu^{+}\mu^{-}e^{+}e^{-}$ ( $m_{H}$ = 130 GeV )

Figure 2.3: Simulated event display of a Higgs boson decaying into two lepton/antilepton pairs [ATL97a]

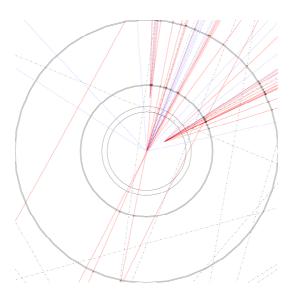

Figure 2.4: Simulated event display showing three hadronic jets, one originating at the primary vertex, two on secondary vertices usable for flavour tagging [BAT00]

To extract these telltale bb productions from the background of other hadronic jets abundant in the end states of strong interaction processes, dominating the pp cross section, it is crucial to differentiate the isolated decay of b quarks and antiquarks at secondary vertex points from similar processes involving second family quarks and from jets produced from stable first generation quarks, lacking secondary weak interaction vertices. This can be achieved by comparing the distances of the secondary vertices of hadronic jets (see figure 2.4) from the primary interaction point, as the mixing of b-quarks in the Cabbibo-Kobayashi-Maskava matrix with the lighter quark families is relatively weak, allowing for significantly longer life times of b-quarks compared to c- and s-quarks.

This heavy flavour identification or b-tagging is a crucial feature not only for Higgs searches, but also for searches for supersymmetric particles and precision measurements involving heavy flavoured quarks (known as b-physics) [ATL97a] [ATL99b]. The possible quality and significance of b-tags is one of the most important benchmarks of the ATLAS experiment, as is hermeticity of the detector and the possibility to perform precise measurements of transversal momentum  $p_T$  and missing transversal energy  $E_T^{miss}$ .

To have the option of a comparison of distances between primary and secondary vertices a fine grained resolution of particle tracks close to the interaction point is necessary, calling for a set-up incorporating a micro vertex detector providing more than three correct space coordinates for every particle track and a good resolution of tracks even within a hadronic jet.

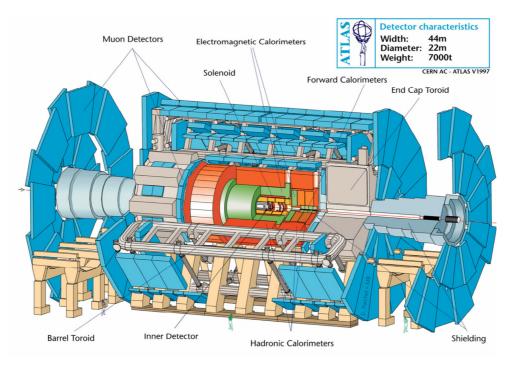

#### 2.1.2 ATLAS detector layout

Similar to the detectors used in the electron-positron collision experiments at LEP as well as many other high energy physics experiments over the last decades designed for experiments exhibiting identical inertial systems for the detector and the center of mass of the collision, the ATLAS detector uses a cylinder symmetric layered detector concept consisting of subdetectors, each specialized in providing certain event information (see figure 2.5). The detector components are specialized for the needs of the ATLAS physics program and thus breaks new ground both in scale and in the characteristics and technologies of its components and subdetectors [ATL99b]. The most distinctive features of the ATLAS concept are a high resolution muon spectrometer with dedicated trigger system, a toroidal outer magnetic system realized with a minimum of added absorbing mass (superconducting air toroids), and a calorimetric system optimized for spatial resolution.

The detector is designed to cover a pseudorapidity range  $\eta$  from -3.2 to 3.2 (-4.9 to 4.9 including the forward detector). The inner parts of the detector are enclosed in a solenoidal magnetic system standard for many earlier particle physics experiments, in this case producing a nearly homogeneous field of 2 T, while the outer part is provided with a magnetic field ranging up to a peak field of (4.2-4.4) T by superconducting toroidal air coils. The latter greatly reduce the amount of nonsensitive material present within the detector compared to traditional coil and yoke set-ups [ATL94]. The subdetector farthest from the interaction point is the muon spectrometer array, defining the outer envelope of 46 m length and 24 m diameter of the whole detector set-up. Like all subdetector systems, it consists of multiple barrel-shaped detector layers centered on the interaction point, and several end-cap layers closing the forward and backward ends of the barrels. The muon system's spectrometric precision of better than  $50 \, \mu \mathrm{m}$  spatial resolution for reconstruction of muon tracks is provided by monitored drift tube (MDT) chambers and, in the extreme forward and backward region, by cathode strip chambers (CSCs) of high granularity. Both are triggered by a dedicated system of resistive plate chambers (RPCs) and thin gap chambers (TGCs) [ATL97b]. The next layer inwards is a hadronic calorimeter for measuring the energies of hadronic jets realized as a combination of a tiled set-up of plastic scintillators with a calorimeter using liquid Ar as an active medium and Cu absorbers followed by an electromagnetic calorimeter, realized as a liquid Ar system with Pb absorbers, all sufficiently granulated to yield a space resolution of  $0.1 \cdot 0.1$  or better in  $\eta$ and  $\phi$  [ATL96a] [ATL96b].

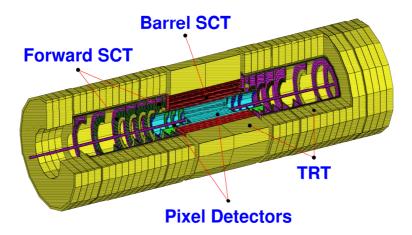

The ATLAS inner detector within the central solenoid (see figure 2.6) is enveloped by the transition radiation tracker (TRT). It consists of an array of Xe filled straws, oriented axially along a central detector barrel and radially within end-cap wheels. The modularly packed straws exhibit a spatial resolution of  $170 \,\mu\text{m}$  perpendicular to the straw orientation. Still closer to the interac-

Figure 2.5: Overall set-up of the ATLAS subdetector systems [ATL99b]

Figure 2.6: Layout of the ATLAS inner detector subsystems [ATL97a]

tion point are the silicon tracker layers, similar to the TRT consisting of central barrel layers as well as wheels for the forward and backward directions. The outer layers are built from single and double sided silicon strip detector modules called SCT (SemiConductor Tracker), while the innermost layers, installed next to or in the case of the so called B-layer barrel on the beam pipe around the interaction point, and again exhibiting disc layers in forward and backward direction, are constructed from tiled hybrid pixel silicon detector modules [ATL97a].

#### 2.1.3 Pixel detector concept

The innermost subdetector for an experiment like ATLAS for several reasons demands the implementation of a silicon pixel system. As is the case with microstrips, a high granularity can be achieved because of the significant progress in silicon processing, providing robust vertex detector components at a low probability of particle absorption or multiple scattering. For a use within the central tracker layers for vertex reconstruction, strips have the drawback of either forgoing spatial resolution in one dimension (in the case of single-sided modules) or, when using double-sided detectors or modules with pairs of single-sided ones set up at a stereo angle, producing ambiguous location reconstruction data for more than one simultaneous particle hit per module. As the expected mean number of visible particle tracks for a bunch crossing producing at least one potentially relevant physics event is above 1000 [ATL97a], and all resulting hadronic jets will produce tracks bundled within a relatively small solid angle the latter effect would be highly detrimental to the detector performance. This problem can be solved by choosing a silicon detector gaining two-dimensional spatial information via one surface segmented into individual pixels. The high bunch crossing rate of the LHC (40MHz) is optimized for producing a massive amount of physically interesting collisions and thus allows for only a minimal detector dead time (significantly below the minimal bunch crossing interval of 25ns). This excludes the use of CCD pixel detectors because of their relatively time consuming serial read-out, leaving a hybrid pixel concept as the only suitable type of semiconductor detector fit for reliable production in sufficient quantities, as monolithic pixel detectors (see [KEM87] and [DEP00]) are only now beginning to be produced in small series suitable for assembly of vertex detectors [WIE04] or at an even earlier development stage [RIC03a] and thus not available when production for the ATLAS pixel detector had to start.

Additionally, as will be discussed later, the detector set-up as a hybrid silicon pixel detector lends itself excellently to applications calling for high tolerance regarding charged hadron radiation.

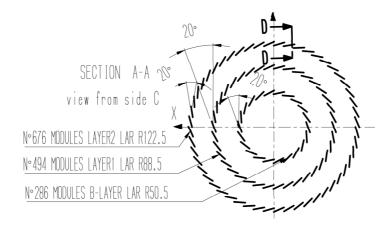

To achieve the high resolution and fast readout times necessary for the ATLAS tracking system a hybrid pixel detector is being implemented for the innermost tracking layers. The layout of the detector system consists of three concentric barrel layers and two sets of disks, one each in forward and backward direction. The number of discs in each end-cap set has varied historically from five in earlier specifications [ATL98] to the current value of three (see figure 2.7). On each of these mechanical carrier structures detector modules are inclined in an overlapping tile pattern to cover the whole pseudorapidity range of the pixel detector without significant gaps in any single detector layer. Additionally this inclination can be used to optimize spatial resolution (discussed below).

The support structures called staves for the barrel layers and disc sectors for the ring shaped discs provide a mechanical framework and thermal contact to an evaporative cooling system using  $C_3F_8$  as a coolant. The materials used are aluminium and carbon compounds, to minimize scattering and absorption of particle tracks within non-sensitive material. Along the carrier structures each module is supplied with electrical ground, high voltage for sensor depletion and operation voltages for electronics operation, and is controlled and read out via an optical glass fiber connection [ATL98].

Figure 2.7: Cut-away view of the ATLAS Pixel subdetector [LBL04]  $\,$

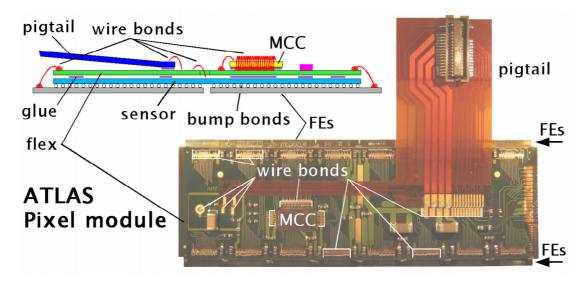

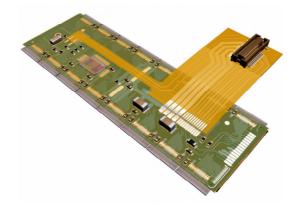

#### 2.1.4 Pixel detector module

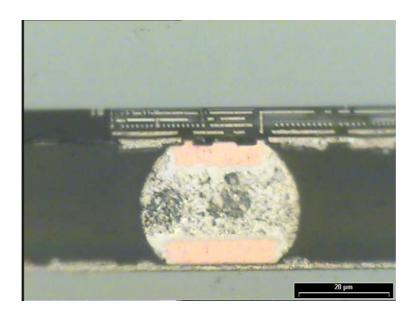

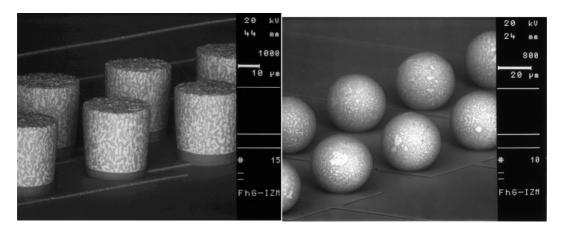

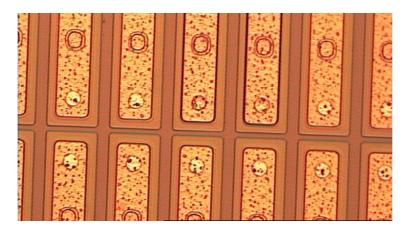

As a hybrid pixel detector, each detector module consists of a sensor tile and sixteen front-end electronic chips glued to a flexible kapton carrier acting as a circuit board (see figures 2.8 and 2.9). The nominal dimensions of each pixel cell are  $400\,\mu\mathrm{m}$  length oriented along the barrel length or the disk radius and a  $50\,\mu\mathrm{m}$  pitch in direction around the barrel circumference or perpendicular to the disk radius. The readout connections between sensor and electronics are realized as bump bond contacts between contact pads of each sensor pixel cell and the corresponding front-end pixel (see figures 2.10 and 2.11a & b). To produce these small pitch micro integration bumps, two distinct technologies will be used, indium bumps remaining malleable at room temperature being set under considerable pressure with an alignment precision well below their dimension of  $20\,\mu\mathrm{m}$  diameter [GEM00], while solder bumps are molten in a re-flow step and are self-aligned within the margin of bump dimension during the following cooling down step by surface tension. (For an overview of the use of these technologies in an earlier project, see [CAC01].)

Figure 2.8: Components and assembly structure of the ATLAS pixel module [DOB04]

Figure 2.9: Three-dimensional model of the ATLAS pixel module [DOB05]

The so called bare module is glued onto the flexible kapton carrier, and the vias on the carrier are connected to the sensor tile metallization via conductive glue to supply high voltage to the sensor and via aluminium wire bonds (25  $\mu$ m diameter) to the voltage supply and signal pads of the frontend chips, not only providing operation voltages for the front-end electronics as well as a connection

Figure 2.10: Cross section of a solder bump connecting pixel sensor to front-end electronics [IZM04]

Figure 2.11: Solder bumps a) after photolithographic deposition (left) and b) after re-flow (right) on a carrier surface [IZM04]

#### 2 ATLAS Pixel sensor

for triggers and data read-out, but indirectly grounding the silicon sensor via the DC coupled preamplifier transistors and guard connections to analogue ground. The further components of the module (see figures 2.8 and 2.9) besides passive capacitors and resistors are the module control chip (MCC) and a connection to the so-called opto-package located away from the module itself on the nearest patch panel for supply and signal lines. The former is a single electronic chip per module. wire bonded onto the kapton carrier for managing all signals to and from the front-end, setting fast control operation parameters, receiving requests for data of a specific bunch crossing according to level one trigger decisions for the whole ATLAS system, retrieving all relevant data from the frontend buffers and sending them out as zero suppressed event information on module level useable for further event building. The opto-package is an elaborate part of the cable connection of the module to the rest of the world, encompassing several chips and diodes connected to optical signal lines. It is connected to the module via a connector on the kapton pig-tail glued and wire bonded to the flex carrier and containing all signal and voltage supply lines. Within the package, the event information from the MCC is translated into optical signals in a VCSEL (Vertical Cavity Surface Emitting Laser), controlled by the VCSEL driver chip (VDC), and fed into an optofibre connection to the read-out electronics outside the ATLAS detector. Incoming operation commands and test signals to the MCC are in turn received via the fibre connection by a photo sensitive diode read out by a biphase decoding chip (DORIC). The voltage supply lines are running from the pig-tail as individual micro cables parallel to the optical signal lines via several patch panels.

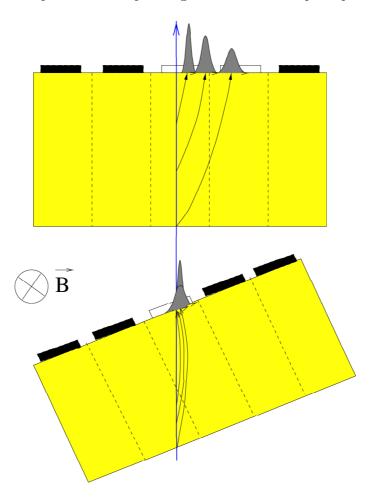

Figure 2.12: Signal clusters within a magnetic field for different incidence angles [GOR01]

The module components having the biggest influence on sensor operation, aside from the sensor

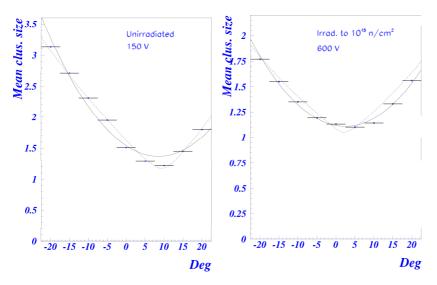

Figure 2.13: Cluster size dependency on incidence angle for modules a) before (left) and b) after (right) proton irradiation [GOR01]

itself, are the front-end electronics chips and the bump connections between them and the sensor. As already mentioned, the sensor pixel cells are set via a DC connector to the input voltage of the pixel cell pre-amplifier, around (1-1.5) V more positive than analogue ground connected to the sensor guard structures. This voltage difference adds to the negative bias voltage applied to the sensor p-side and shapes the potential within the sensor for charge collection in the pixel cells. The induced charge fed into the front-end pixel cell is amplified in the pre-amplifier and shaped as a sharp rise in voltage proportional to the collected charge followed by a linear drop induced by a feedback current. This allows for two trigger signals per registered charge, one for the rising and one for the falling flank, with a time over threshold interval proportional to the signal height above threshold voltage respectively above the threshold equivalent charge. The time over threshold as well as the hit time are stored in a designated latch for each pixel cell, to clear the amplifier and sampler for the next hit and are read out into buffers on the end of each pixel double column, where they are either retrieved by a level one trigger request or discarded after being identified as not belonging to a triggered event. Individual pixel thresholds as well as the feedback current can be tuned to minimize threshold dispersion, and produce a time over threshold scenario yielding both a sensible charge resolution and a clearing time of the amplifier comparable to the 25 ns bunch crossing interval.

To improve the spatial resolution of the pixel sensor beyond the limits of the pixel dimensions, double or triple hits of the same particle track in pixels of one module can be used to weigh the shared charge and determine where exactly the track in question has crossed which depth within the active sensor volume. This will only be possible for a significant portion of measured tracks, if the thresholds can be set low enough to measure charges smaller than (0.3-0.5) of the total charge deposited by a typical particle track, and the modules are inclined away from the ideal track incidence angle (Lorentz angle) for the inner detector's magnetic field (see figure 2.12), producing a longer, diagonal particle track through the sensitive volume and thus a higher proportion of multiple pixel tracks, and away from a perpendicular track incidence angle, producing a higher typical total charge deposited per track. As the ideal Lorentz angle and thus the cluster size dependency changes for sensors having received bulk damage from irradiation (figures 2.13a & b), this inclination can be optimized for fast charge collection within the sensor and small cluster sizes after full irradiation, leading to minimized charge loss by charge carrier trapping and increased signal height per pixel, by placing sensors at an optimal Lorentz angle for the magnetic field within the inner detector. (For further discussion see [ALE00] [LAR01] [GOR02] [GOR01].)

## 2.2 Pixel sensor design

The ATLAS Pixel sensor has not only to meet considerable geometrical constraints concerning its thickness and granularity as well as a high charge collection efficiency within the sensitive volume, most of all it has to remain fully functional for as long as possible, while sustaining a massive amount of both ionizing and non-ionizing particle damage throughout its projected ten year lifetime. To arrive at a sensor concept coping with these requirements, a two-way approach has been taken. On the one hand a selection process for a substrate material readily available and exhibiting the optimal radiation tolerance under the damage scenario expected for ATLAS operation was started in collaboration with people from other high energy physics experiments as well as from physics groups concerned with characterizing semiconductor material and studying effects of radiation damage on semiconductors. This collaborative effort was mostly done under the roof of the CERN ROSE collaboration (a.k.a. RD48).

The other line of development has been concerned with the design process of the pixel structure itself, to make use of the radiation tolerance of the chosen bulk material and add to it with a radiation tolerant surface process as well as to meet the design parameters set for integration and electrical properties before irradiation. This aspect has been a collaborative effort within the ATLAS pixel collaboration, especially benefiting from the technological and experimental knowledge of the semiconductor laboratory (MPI-HLL, Munich) of the Max-Planck-Institutes for physics and for extraterrestrial physics in Munich. In this case the collaboration has been effected on a much narrower scope toward the specific characteristics sought for the ATLAS Pixel detector, as these will inevitably vary significantly from those suited for other experiments run under different conditions and pursuing different scientific goals. These two lines of development have been combined to provide a state-of-the-art device exhibiting the best possible radiation tolerance, fully complying to all ATLAS requirements in the set-up described above.

#### 2.2.1 Sensor concept

As part of a state-of-the-art hybrid pixel detector, the ATLAS pixel sensor (see [HÜG01] for overview of planning and prototyping) is planned to be in principle an array of bipolar diodes created on a high resistivity bulk close to intrinsic charge concentration (n dose around  $10^{12} \, \mathrm{cm}^{-3}$ ) by implanting high positive or negative dose regions (n<sup>+</sup> and p<sup>+</sup>) on one wafer surface each. Given a bias connection and a high enough voltage tolerance of the diode array, the asymmetric depletion region on the p<sup>+</sup>-n junction can be operated in reverse bias and extended over the whole sensor bulk volume, able to collect and thus detect all charges produced within the volume by ionizing particles. For the kind of functionality needed for the ATLAS experiment this very basic design has of course to be elaborated on to guarantee inter pixel isolation, minimize leakage current and make the sensor testable as well as tolerant to radiation damage and suitable for assembly as a hybrid detector.

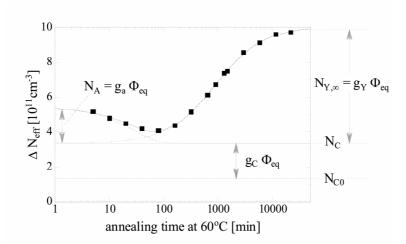

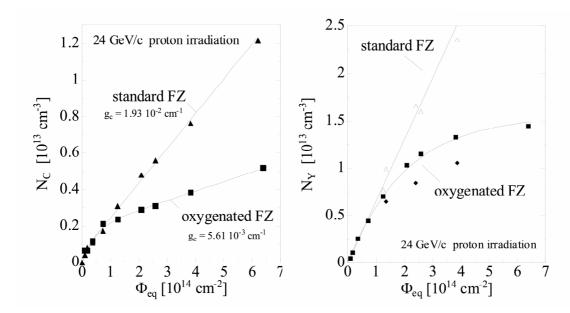

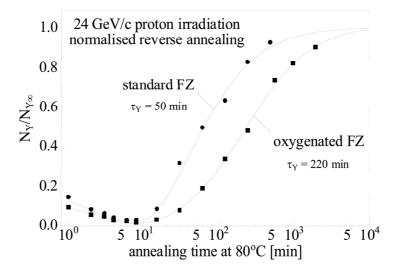

The results of the ROSE collaboration on controlled damage engineering [LEM99] as well as follow-up research (e.g. within the RD50 collaboration [CAM03]) provide striking evidence for the high tolerance of silicon with a slightly increased amount of oxygen impurities against bulk damage caused by charged hadrons (an opposite effect has been reported in the presence of a higher carbon concentration). These improvements do not alter the leakage current characteristics, which seem to be adequately described by the NIEL (Non-Ionizing Energy Loss) approach to particle damage. The main difference can be seen in the development of depletion depth after irradiation and annealing. In the parameterization of the Hamburg model (see figure 2.14, [MOL99] and [LEM99]) for an oxygenated sample the constant damage induced charge density is somewhat below the density for samples with average oxygen concentration for fluences  $\geq 10^{14} \, (1 \, \text{MeV neutron equivalents})/\text{cm}^2$ (figure 2.15a). While the beneficial effect of annealing is not significantly influenced, a rather dramatic effect has been reported and confirmed concerning additional effective charge production by long term annealing, so-called reverse annealing. The reverse annealing effects are not only slowed considerably (figure 2.16), producing a lower overall effective charge density in similarly irradiated samples after identical annealing scenarios, there is also a marked saturation of effective charge density for high irradiation fluences absent in standard silicon samples (figure 2.15b). This effect

Figure 2.14: Parameterization of radiation damage and annealing effects in the Hamburg model [LEM99]

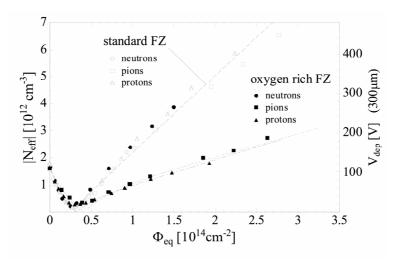

leads to a much lower effective charge density in oxygenated silicon after high dose irradiation with mainly charged hadrons in long term experiments not constantly cooled below room temperature (see figure 2.17). Sensors built from such material are expected to exhibit deeper depletion zones at the same bias voltage respectively full depletion at a lower bias voltage compared to sensors processed from standard high resistivity silicon.

Figure 2.15: Comparison of a) constant effects (left) and b) reverse annealing effects (right) of proton irradiation in standard and oxygenated silicon [LEM99]

These results have been used within the ATLAS pixel collaboration to decide on using an oxygenated high resistivity substrate for the pixel sensor, as most irradiation damage close to the interaction point is expected to come from charged pions from hadronic jets produced in minimum bias events as given in radiation profiles in [KRA04a]. This would be different in regions of the radiation field farther from the interaction point, where the impact of non-ionizing particles (mainly neutral hadrons, especially neutrons) is proportionally big enough compared to charged hadron damage, to make the expected beneficial effect of oxygenation small compared to the overall depletion development.

Figure 2.16: Comparison of annealing times of proton irradiation in standard and oxygenated silicon [LEM99]

Figure 2.17: Effective charge densities in standard and oxygenated silicon after irradiation with neutrons or protons and controlled annealing steps [LEM99]

High resistivity silicon has been chosen from the start to minimize effects of uncontrolled bulk defects. Only detector grade silicon with low overall charge carrier concentration exhibits the necessary control of unwanted contamination with other trace material, of which some like carbon could be disastrous for long term radiation hardness and which would in any case render controlled damage engineering very difficult. High resistivity provides the sensor with easy to handle low bulk leakage current before irradiation. Together with the decision for n-type bulk material it allows for the technological design choices presented in the following section. The substrate type also postpones the rise of the effective doping concentration by the time needed for the radiation damage to convert the material to effective p-type.

Figure 2.18: Change of voltage necessary for full depletion of sensors according to irradiation and annealing effects expected under the Hamburg model for the two inner pixel detector layers in a standard (solid) and elevated (dashed) radiation scenario [KRA04a]

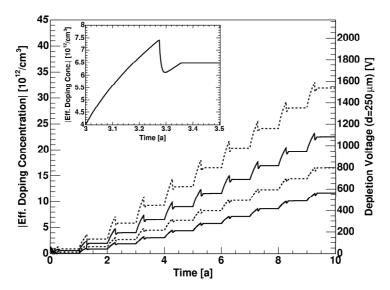

The price to be paid for choosing a high resistivity substrate can be seen when contrasted with the depletion strategy of strip detectors at LHC experiments, where n-type substrates with higher depletion voltages are chosen. Their absolute effective charge concentration, due to the overall lower radiation exposure compared to the pixel detector, ends up after the full projected operation time at less then twice the starting value, having inverted to effective p-type between  $(1-5) \cdot 10^{13}$  (1 MeV neutron equivalents)/cm<sup>2</sup> [DEM02] [DIE03]. This allows for a constant bias voltage for the whole operation run. In the ATLAS pixel sensors at the other hand an early inversion of bulk type is expected, as the effective charge concentration starts out at around  $8 \cdot 10^{11}$  cm<sup>-3</sup> and for a wafer thickness of  $250 \,\mu\text{m}$  will invert to effective p-type at only around  $(2-3) \cdot 10^{13}$  (1 MeV neutron equivalents)/cm<sup>2</sup> depending on annealing [LEM99] [KRA04a]. Therefore operation in converted bulk type is to be taken into account as normal operation mode and a steady increase of necessary bias voltage from this point on, far beyond the specified voltage for unirradiated sensors, has to be assumed to keep operating at maximum depletion (see figure 2.18).

#### 2.2.2 Pixel design

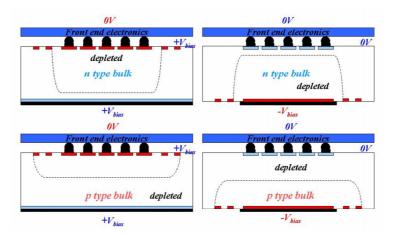

Within the conceptual process of which production process and sensor material to choose, one decision taken directly concerning pixel design is the doping type of substrate and structured implantations used for sensor processing. Taking into account advantages regarding process technology and radiation tolerance of using high resistivity n-type substrate, there are two possibilities to create both the pixel structure and the bipolar doping type junction necessary for depletion. The technological less demanding way to do this would be using a structured positive doped implantation (p<sup>+</sup>) including pixel cells and a guard ring structure to minimize surface leakage currents. The opposite wafer side would then only need a planar high dose negative (n<sup>+</sup>) implantation, calling for photolithographic mask processes performed only on one side of the wafer. There are two less than optimal aspects in this approach (see left half of figure 2.19). Firstly the bump bonds between sensor and electronics would be attached on the same side and very close to the guard ring structure. As the effective resistivity across the bulk edge is much lower than that of a guard ring structure, the biggest voltage drop on the surface of a biased sensor will occur on the latter, thus putting the surface area outside the guard ring to the sensor backside potential. The analogue ground of the front end electronics — and in a good approximation the slightly different pre-amplifier potential of the pixel contacts, too — exhibits a potential difference to the outside area equal to the full bias voltage of the sensor. The danger of shorts across the guard ring to the bump metallization or across the sensor-electronics gap would be quite high, especially if there was any condensing moisture within the detector volume.

Figure 2.19: Comparison of  $p^+$ -in-n (left) and  $n^+$ -in-n (right) pixel sensors before (top) and after (bottom) type inversion

Another possible problem comes with changes of electric characteristics induced in the silicon bulk by irradiation. Above a certain deposited energy dependent on particle type [WUN92], irradiation damage in the silicon crystal will generate vacancies and interstitials raising the effective positive doping of the bulk material, an effect amplified by ongoing crystal change during reverse annealing. This switches most of the bulk silicon to effective p-type and alters the way the sensor depletes when bias voltage is applied. After type inversion the depletion zone does no longer grow mainly from the structured p<sup>+</sup> implants but can be approximated, while neglecting double junction effects, as growing from the backside n<sup>+</sup> implant (see right half of figure 2.19). If the effective doping concentration of the bulk material has increased beyond a certain point and full depletion is no longer possible with a given maximum bias voltage, the undepleted bulk zone will be situated around the pixel cells. In a configuration like this, charge collection would be deteriorated, as according to Ramo's theorem [RAM39] in small pixels most charge is induced by charge carrier motion close to the pixel contact (small pixel effect [KLA99] [KRA04a]), and even more problematic an undepleted current channel between the individual pixel cells would form, leading to high cross talk within the pixel array.

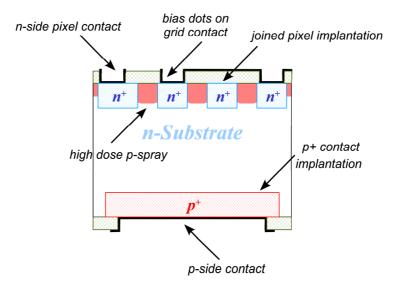

To avoid these problems a different design approach has been chosen for the ATLAS pixel sensor. The positive and the negative implanted wafer sides are both structured by mask processes for implantation, metallization and deposition of silicon oxide and nitride. This double sided processing creates the need for much more intricate and precise mask steps, especially incorporating front-to-back mask alignment in the order of few  $\mu$ m. But paying this price allows for a segmented n<sup>+</sup> implantation used for definition of pixel cells and a guard ring structure on the p<sup>+</sup> implanted wafer side, locating the main voltage drop on the sensor surface opposite to the bump connections, covered by a layer of high resistivity kapton foil. As the pixels are now realized as n<sup>+</sup>-in-n implantations, the sensor has to be fully depleted before type inversion to achieve full functionality, as the depletion zone will grow from the p<sup>+</sup> implanted backside. This can easily be achieved, as for a few hundred  $\mu$ m thick sensors processed on high resistivity silicon bulk  $((2-3) k\Omega/cm)$ , full depletion occurs below or around 100 V, a bias voltage unproblematic for most sensors in terms of breakdown. After type inversion, the depletion zone now grows primarily from the segmented n<sup>+</sup> implantations into the bulk now converted to p-type, placing the pixel cell not only into the depleted volume, but into the region of the highest electric field, no matter how much of the bulk can be biased.

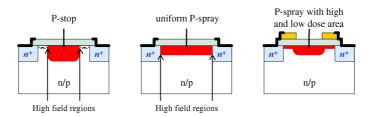

Figure 2.20: Comparison of inter pixel isolation technologies

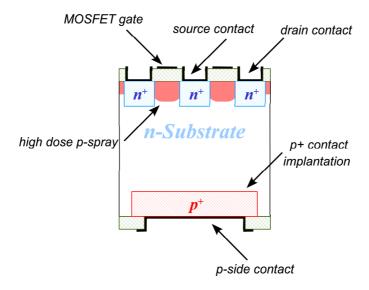

When using a segmented n<sup>+</sup> pixel implantation in n-type bulk, another aspect of sensor technology has to be taken into consideration. Due to positive charges within the oxide layer, electrons in the neighbouring bulk region are drawn towards the interface, forming a layer of mobile charges functioning as a possible current channel even after full depletion. This situation prevents full electric isolation between the pixel cells and becomes considerably more pronounced after irradiation with ionizing particles creating more charge carriers within the oxide layer. To prevent these effects, an additional p-type implantation has to be added in between the pixel cells to interrupt the current channel formed by the electron layer. This can be done by adding a grid of p<sup>+</sup> implantations in the center of the inter pixel gaps (p-stop) or by implanting a low dose p-type layer over the whole sensor surface (see figure 2.20). But this technology would still have left a large part of the oxide interface in direct contact with the p-type bulk, leading to the forming of aforementioned electron layer. This layer of negative charge creates high electric fields where it touches the p-stop implantation, increasing with a growing electron density after ionizing irradiation of the oxide. This would lead to an increased likelihood of early sensor breakdown after irradiation [HÜG01], a tendency not viable for sensors to be used in a high radiation environment, including a high percentage of charged pions.

The covering of the whole n-side surface with a low dose p-implantation layer does prevent the forming of an electron layer at the interface, but brings the p-spray in direct contact to the n<sup>+</sup> implantation, again creating a high field region bound to increase the tendency of a sensor for electric breakdown. Fortunately, in this case the highest electric fields will occur in sensors with minimal ionizing radiation damage to the oxide interface, as the electron accumulation caused by interface charges lowers the effective p-spray dose [WÜS01]. So every sensor showing no early breakdown before irradiation can be expected to remain functional and even to improve in quality by raising the voltage of electric breakdown with increasing irradiation. This provides an excellent opportunity for quality assurance, making it possible to test produced sensors for electrical breakdown in their worst case state before irradiation. Processing p-spray sensors avoids an additional mask step necessary for p-stop implantation and lowers production cost.

The pixel isolation method finally chosen for the ATLAS pixel sensor uses the advantages of

#### 2 ATLAS Pixel sensor

p-spray technology while minimizing the resulting production yield issues. In a moderated p-spray process developed at the Semiconductor Laboratory of the Max-Planck Institutes for physics and for extraterrestrial physics (MPI-HLL) [LUT97], the p-spray dose is regulated in an additional mask step, creating a slightly deeper high dose p-spray region in the center of the inter pixel gap and a slightly shallower low dose layer everywhere else. This method considerably lowers the electric field at the junction between p-spray and pixel implantation without lowering the effectiveness of the inter pixel isolation and has already been demonstrated to be intrinsically radiation hard [WÜS01] [HÜG01] [RIC02a].

The possibility to test sensors before assembly and irradiation for electrical characteristics in a state of operation, when the electrical field at the implantations is expected to be highest i.e. most prone to break down early, is of additional benefit in this design. Not only does sensor breakdown behaviour improve during bulk damaging irradiation, the design also allows for the implementation of a bias grid based on potential punch through to be used before assembly for current tests on the complete pixel array, thus providing a quality assurance tool to confidently declare a sensor functional from the very start.

# 3 Planning of quality assurance

## 3.1 Quality plan concept

The basic aim of quality assurance, no matter whether in physics experiments or in industrial production, is to assess the necessity of certain quality control measures in a given context and implement them into a context of planning and administration. While not always easy to differentiate in real life and not necessarily well-defined in literature, there are different important levels of quality assurance. To create an organizational framework helpful for achieving high quality output is usually described as quality management. Quality control in the strict sense are tests performed to gauge quality after the fact. But additionally, quality assurance can cover many aspects of planning and preparation to avoid possible problems or make them less likely to cause much harm. To optimize the effectiveness of quality control and incorporate it with advance planning within an organized production or operation, a quality plan has to be drawn up, defining the characteristics to be tested for and to analyze the effort needed and adequate to provide a representative picture of the production quality.

A way to systematize and quantify these processes used in commercial quality management is the FMEA (Failure Mode and Effect Analysis) [MAS94] [PFE01], a systematic, if not mathematically exact assessment yielding a quantitative index called risk priority number (RPN). This analysis derives a relative measure of importance for quality control by multiplying three key factors rated between 1 and 10 for the necessity and feasibility of testing.

The first factor and possibly the hardest one to define is one measuring the likelihood of occurrence O of a specific problem, roughly reflecting probabilities of certain production failures or material flaws ranging from close to 0 (O=1) to close to 1 (O=10). The difficulty arising here stems from incomplete knowledge of all the possibilities of malfunction, especially estimating correct probabilities in advance, when a new production step begins or a new production run of a manufacturer starts, with former prototyping or earlier runs, not representative of the new results, being the only available source of information. Thus, important possible sources of failure could be overlooked, if there have not been any pertinent earlier problems or if those causes were not easily extrapolated from theory and prior experience.

The second factor is a measure of the potential severity of a given problem with regard to the final functionality and security of a product — in this case the usability of the pixel sensor for module assembly and operation in the ATLAS detector. This is, while still not possible to exactly quantify, considerably easier to estimate than the likelihood of occurrence of the problem, as potential consequences of many production mishaps are well understood or at least documented in literature. In cases of largely undocumented problems, impact on later functionality can be assessed as soon as a new problem is first detected, as long as adequate means of testing are available. The numeric values for the impact factor I are rated between the extremes 'effects hardly noticeable in operation' yielding a 1 and 'complete breakdown of system function virtually guaranteed' yielding a 10 (a more elaborate, commonly used table of values can be found in [MAS94]).

Finally, a factor representing the inverse relative likelihood of early discovery D of the problem has to be determined — yielding D=1 for a detection probability close to 1 and D=10 for one close to 0. As the overall risk inherent in a production problem is eliminated by the discovery of faulty parts the canonical approach to this factor is just to quantify the likelihood of discovery. In the context of an elaborate and long running experiment in which most malfunctions will finally be discovered, but often late enough to cause considerable repair efforts or data loss, a rating prominently including the integration step during which the malfunctioning component can be identified can be justified.

The overall RPN computed as RPN =  $O \cdot I \cdot D$  and ranging from 1 to 1000 is usually compared to a defined threshold value (125 being typical) to decide whether a specific problem has to be

confronted by changing production parameters or quality tests or can be left unchallenged. This threshold value is set arbitrarily and as — in addition to ambiguities caused by insufficient data — it is not clearly defined in the literature (e.g. [MAS94]) whether one step in the probability values O and D represents an equivalent increase on a linear or logarithmic scale of likelihood or something else entirely, RPNs themselves are relatively rough estimates. Within the unavoidable limits of comparability, reliable data do require experience over a long production period with a lot of the possible mishaps actually happening and containment plans to avert said problems being at least drawn up and practically projected, if not carried out.

Considering this, the relative quantification of the importance of quality assurance measures and the effectiveness of steps taken to control and optimize production quality as an RPN cannot be taken as an exact gauge for critical systems. But it can be used as a heuristic exercise to sum up possible problems theoretically known and procedures to avoid them and as an estimate of the urgency and feasibility of such measures. If nothing was known beforehand about the main trouble sources lowering production or assembly yield, further prototyping and engineering runs would be called for. If yield was generally high and the extent of possible complications caused by faulty parts was small compared to the effort of checking and fixing or replacing them, systematic quality control could be minimized in number and effort within a quality plan.

#### 3.1.1 Necessity of quality assurance

In big physics experiments in general and especially in the ATLAS pixel detector this last conclusion cannot be made due to the two central aspects of complexity and accessibility of the system. In the case of sensors discussed here, a faulty sensor tile recognized after module assembly will render the whole module non-functional without a possibility of reworking, not only wasting electronic chips and module material, but also cost and time of the actual assembly process, and putting a strain on the project schedule and budget as additional, not planned for material has to be used and an increased workload has to be coped with. If a similar flaw was detected after incorporation in the mechanical detector superstructure, reworking of the assembly would probably be possible, but painstaking disassembly and re-alignment would be necessary to replace the faulty module. After the commissioning of the whole pixel sub-detector any further repair on a detector part will be prohibitively constrained. The central position of the sub-detector alone does not allow access without dismantling most of the other detector components — in the current baseline design this means opening the calorimeter and muon detector end-cap and removing the whole pixel detector including the part of the beam pipe around the interaction point. Even under the best of circumstances this would take a major effort and a prolonged pause in collider activity and data acquisition [ATL99a] [ATL97a]. In a typical case, after an integrated luminosity equaling a month or more of design luminosity operation, the material — especially the heavy metal absorbers in the calorimeters around the inner detector — will have been activated to a degree requiring a beam shut down followed by a cooling down period of no less than a day before a strictly controlled and limited access to the inner detector can be granted at all without severely endangering the health of those involved [ATL94].

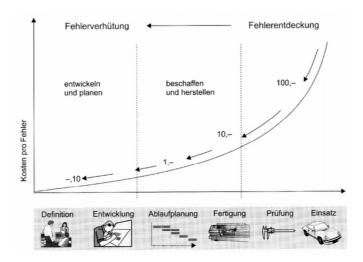

Generally speaking all this is no more than an application of the economic rule of thumb for all large and complex industrial projects (given as a 'Rule of Tens' in [MAS94] and [PFE01] as in figure 3.1): the later in the design or production process a change has to be implemented the bigger the involved effort and the higher the cost in time and money. This increase is quantified at approximately one power of ten per production step a critical malfunction goes unnoticed, starting at a few cents during initial informal planning and going up to the full costs of the entire production after assembly and commissioning. In the special case of a the ATLAS pixel detector and in the light of the distinct needs mentioned above, this general rule is hard evidence for the economic and scientific necessity to make sure that every part used for detector assembly can be confidently assumed to be fully functional and to stay that way as long as possible during operation.

In commercial projects as well as in many scientific ones, much of the responsibility of providing functional parts can be outsourced to contractors by demanding in-house testing and prompt replacement or a contractual fine for the delivery of non-functional parts. For two reasons this

Figure 3.1: Illustration of the 'Rule of Tens' in industrial production from [PFE01]

strategy is only of limited help for the task at hand. On the one hand several of the used parts are of very radical design both in connection density and in radiation hardness, so that a contractual guarantee of functionality beyond some very precisely defined tests is unlikely to be available from any manufacturer. On the other hand, if a crucial part was to prove defective after assembly or even during operation, a fine or replacement could only alleviate the immediate monetary consequences. The loss of time, effort and most of all crucial physics data could never be replaced.

This puts the responsibility to investigate the most likely and gravest dangers to functionality on the physics collaboration, a task necessary because of the novelty of the used devices, which additionally offers opportunity for further insights in device physics and detector behaviour. From this information one can extrapolate test procedures which should be adhered to by the manufacturer or better still which can be used for in-house testing by the institutes involved. The latter possibility does not only provide confidence in the overall behaviour of the tested part concerning known process and assembly risks but allows for adequate reaction to until then unknown difficulties. Existing data sets can be compared for evidence pointing towards behaviour so far not included into quality considerations and testing activity can be stepped up or amended by new or improved procedures looking for new kinds of information likely to exclude faulty parts from further use in a detector assembly.

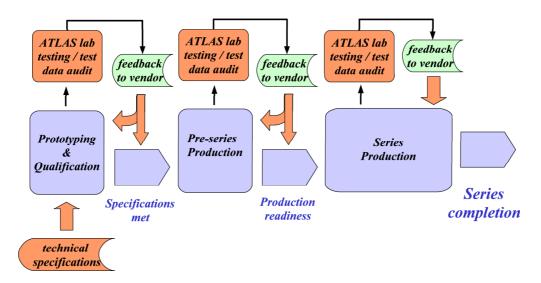

#### 3.1.2 Aims of the quality plan

In the case of the silicon sensor tiles for the ATLAS pixel detector, planning for systematic quality assurance started already during the period of design development and extensive prototyping [HÜG01] from 1997-2000. Results of prototyping as well as testing procedures described in earlier publications ([HÜG97], [WÜS97], [ROH99], [WÜS01] and [BOR01]) have been used to formulate the technical specifications for tendering sensor production and implement the first systematic testing protocols with the start of pre-production in 2001. These have been continuously updated and amended since then, both to conform to the necessities of detector production and to reflect our increasing knowledge on the actual sensor manufacture and detector assembly processes.

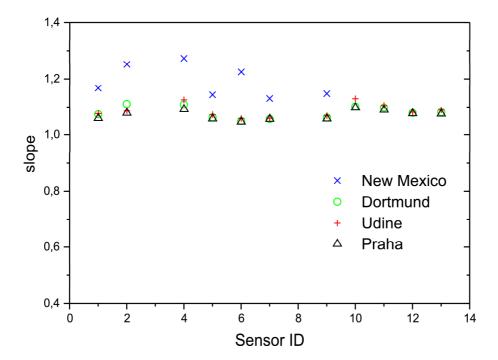

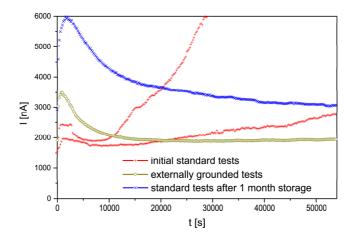

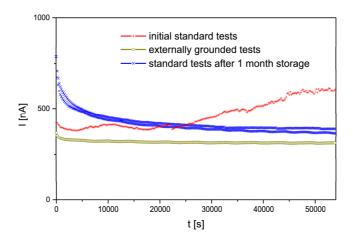

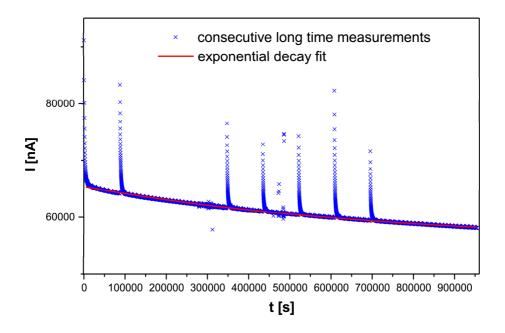

From the start the procedures called for tests to be performed by both the four testing institutes within the ATLAS pixel collaboration. This has proven to provide an effective way for continuously monitoring and crosschecking the quality of the sensors, the correct application of the test procedures and the full functionality and comparability of the used test set-ups.

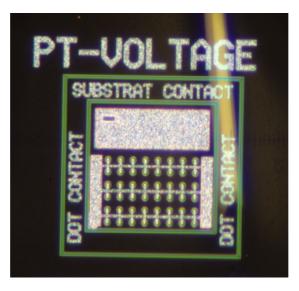

One specific aim of the quality plan defined early on has been the gathering of data relevant for sensor operation, if possible before any assembly steps are taken and in any case before a module bearing the sensor in question gets eligible for further integration. The main strategy used for this has already been implemented in the design of the pixel wafers. It is important to test the individual sensor tiles early, directly gathering data on their behaviour before any other step of assembly but without mechanically probing the pixelated n-side surface, as it is prone to damage leading to an early electrical breakdown or problems with the metal deposition process for bump bonding. This has been made possible by the integration of a bias grid in the overall pixel design. The bias grid structure allows for simultaneous grounding of all pixel cells to a potential close to an external ground applied to a common n-side contact or even a p-side contact outside the sensor area guard ring.

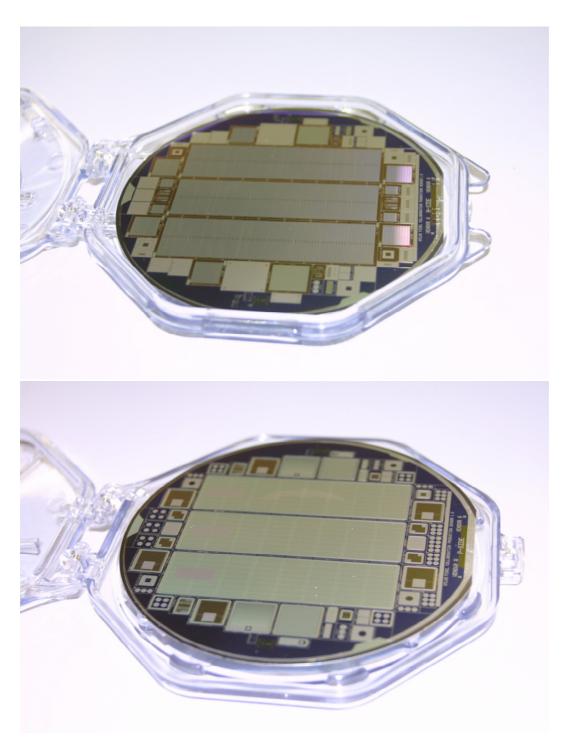

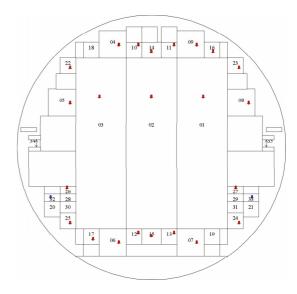

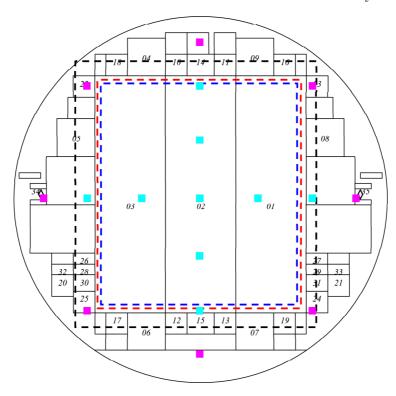

Another central approach to keeping the potential damage to the pixel cells at a minimum has been the use of dedicated test devices custom designed for specific diagnostic tests. As the rectangular tiles are set side by side in the center of the production wafer, there is enough room for an array of test devices individually designed for quality control placed along the wafer edges (see figures 3.2a & b and 3.3), and can be accessed either on the complete wafer or after dicing and removing the sensor tiles on individual test sectors. These allow for easy monitoring of general parameters dependent on bulk material and process quality without any necessity to probe the sensors themselves. Only direct functionality tests are to be performed on the sensors themselves, using the sensors' bias grid and thus not having to probe the sensor pixel cells themselves.

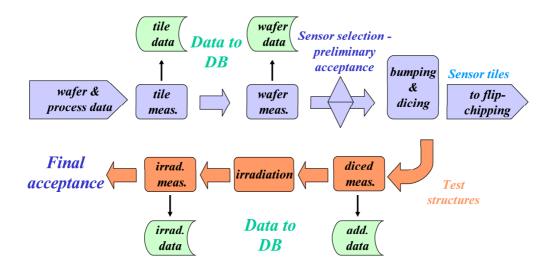

The whole testing cycle is thus broken down in steps sorted by the time of testing as well as the nature of test devices illustrated in figure 3.4.

The first category represents tests performed directly on the central tile area of the wafer. These are intended to be performed before dicing, as they are to be used as the main selection criteria which tiles on which wafers should be diced and used for further assembly.

The second category encompasses all tests performed to check characteristics of a sensor wafer or production batch of wafers on the dedicated test structures of the outer wafer sectors before dicing. Together with the direct tile area tests these diagnostic tests should provide sufficient data to decide on the conformity of the delivered wafers with the design specifications and the functionality of the sensors. If these questions are decided positively, the sensors are considered preliminarily approved.

After bump deposition on the approved sensors and wafer dicing, additional diagnostic tests can be performed on the diced test sectors. These will include ones not deemed crucially important for judging functionality and conformity, but interesting concerning process monitoring as well as repeated tests to establish the effects of metal deposition and dicing and new testing routines additionally established later on.

A special case among after-dicing tests are measurements on irradiated structures, as these cannot be easily performed on whole sensor wafers, or at least render the tiles on the wafer in question useless for detector assembly. On diced test devices, including diodes and small sensors exhibiting a pixel design identical to the sensor tiles, wafers can be tested for behaviour after massive radiation damage without sacrificing any functional sensor tile so early in the production chain. Depending on the diagnostic quality intended to be checked for, irradiation is performed with middle to high energy protons for studies on bulk characteristics and low energy electrons for dedicated studies on interface damage.

There is a fifth category of possible tests not included within the original quality plan concept, but easily incorporated in practice. While the responsibility of the testing laboratories and the quality assurance coordinator originally ended with sending preliminarily approved wafers to the bump vendors and declare them finally approved after all additional testing on diced test sectors had been done, a more active role of collaboration with the bump vendors themselves has proved to be helpful. This has not been done with the same regularity as the standard sensor quality tests or production diagnostics. Only when deterioration of sensor quality was suspected, additional tests were initiated. Those have been thorough enough to draw systematic information on the impact of metallization and wafer dicing.

To make the information gained during assembly of the ATLAS pixel subdetector easily accessible to all involved, a data base for production sensor tests has been created based on and incorporated in a similar program created for the ATLAS semiconductor tracker (SCT).

The overall organization of measurements has been put in the hands of one person each at the collaboration ATLAS pixel laboratories. These people are charged with organizing the quality

Figure 3.2: Production wafer seen from a) the n-side (top) and b) the p-side (bottom)

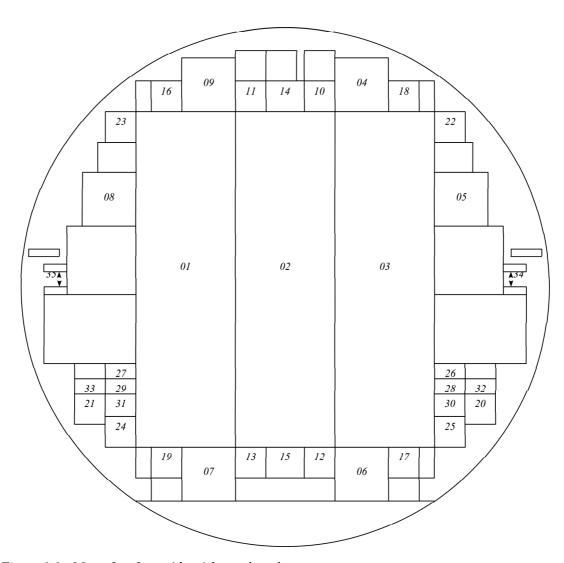

Figure 3.3: Map of wafer p-side with numbered structures:

01-03: sensor tiles 04-09: single chip sensors

10-13: mini chip sensors 14-15: inter pixel test structures

16-17: diodes with guard ring 18-21: ROSE type diodes

22-25: oxide test fields 26-27: n-side test structures

28-29: p-side test structures 30-31: breakdown monitors

32-33:p-side MOS arrays 34-35: mask alignment structures

Figure 3.4: Flow of quality testing

tests, keeping track of them, archiving the measurement data and uploading them to the data base. In case of non-conformities of the delivered wafers or discrepancies with the data provided by the manufacturer, the responsible person documents the existing problems and informs the other collaborators and the contact person for the manufacturer. The quality assurance controllers from each laboratory give regular reports to the ATLAS pixel collaboration on problems, non-conformities or ambiguities having arisen during testing.