## VLSI Design Concepts for Iterative Algorithms

Von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität Dortmund genehmigte

#### Dissertation

zur Erlangung des akademischen Grades Doktor der Ingenieurwissenschaften eingereicht von

Chi-Chia Sun

Tag der mündlichen Prüfung: 11.04.2011

Hauptreferent: Univ.-Prof. Dr.-Ing. Jürgen Götze Korreferent: Univ.-Prof. Dr.-Ing. Rüdiger Kays

Arbeitsgebiet Datentechnik, Technische Universität Dortmund

### **Abstract**

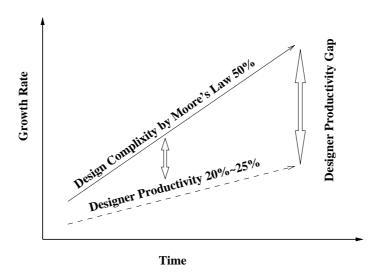

Circuit design becomes more and more complicated, especially when the Very Large Scale Integration (VLSI) manufacturing technology node keeps shrinking down to nanoscale level. New challenges come up such as an increasing gap between the design productivity and the Moore's Law. Leakage power becomes a major factor of the power consumption and traditional shared bus transmission is the critical bottleneck in the billion transistors Multi-Processor System—on—Chip (MPSoC) designs. These issues lead us to discuss the impact on the design of iterative algorithms.

This thesis presents several strategies that satisfy various design constraints, which can be used to explore superior solutions for the circuit design of iterative algorithms. Four selected examples of iterative algorithms are elaborated in this respect: hardware implementation of COordinate Rotation DIgital Computer (CORDIC) processor for signal processing, configurable DCT and integer transformations based CORDIC algorithm for image/video compression, parallel Jacobi Eigenvalue Decomposition (EVD) method with arbitrary iterations for communication, and acceleration of parallel Sparse Matrix–Vector Multiplication (SMVM) operations based Network–on–Chip (NoC) for solving systems of linear equations. These four applications of iterative methods have been chosen since they cover a wide area of current signal processing tasks.

Each method has its own unique design criteria when it comes to the direct implementation on the circuit level. Therefore, a balanced solution between various design tradeoffs is elaborated for each method. These tradeoffs are between throughput and power consumption, computational complexity and transformation accuracy, the number of inner/outer iterations and energy consumption, data structure and network topology. It is shown that all of these algorithms can be implemented on FPGA devices or as ASICs efficiently.

## **Acknowledgements**

This thesis was written while I was working as a research assistant at the Information Processing Laboratory of the Dortmund University of Technology. I would like to thank Professor Dr.-Ing. Jürgen Götze, the head of the laboratory, for all the interesting discussions that contributed essentially to this thesis, for creating an open and relaxed atmosphere, and for providing excellent working conditions.

Furthermore, I am very pleased to thank Professor Dr.-Ing. Rüdiger Kays (TU Dortmund) for his interest in my works, his comments on my thesis and his reviews for my DAAD scholarship, and his time.

I would also like to thank Professor Shanq-Jang Ruan (Low-Power System Lab, National Taiwan University of Science and Technology) for his guidance during my Master study in Taipei. I am especially grateful to my present and former colleagues for providing such a stimulating atmosphere at the laboratory. It was a pleasure to share so much time with you. Special thanks goes to many students for their contributions to this work too.

To my parents and my sister for their support and encouragements during the long years of my education.

Dortmund Germany, April 2011

## **Contents**

| 1 | Intr | oduction                                              | 1  |

|---|------|-------------------------------------------------------|----|

| 2 | Intr | oduction to VLSI Design                               | 9  |

|   | 2.1  | Modern Digital Circuit Design                         | 9  |

|   | 2.2  | Moore's Law                                           | 11 |

|   | 2.3  | Circuit Design Issues: Modular Design                 | 12 |

|   | 2.4  | Circuit Design Issues: Low Power                      | 16 |

|   | 2.5  | Circuit Design Issues: Synthesis for Power Efficiency | 17 |

|   | 2.6  | Circuit Design Issues: Source of Power Dissipation    | 19 |

|   |      | 2.6.1 Dynamic Power Dissipation                       | 20 |

|   |      | 2.6.2 Short Circuit Power Dissipation                 | 21 |

|   |      | 2.6.3 Static Leakage Power Dissipation                | 21 |

|   | 2.7  | Design Consideration for Iterative Algorithms         | 23 |

|   | 2.8  | Summary                                               | 24 |

| 3 | COI  | RDIC Algorithm                                        | 25 |

|   | 3.1  | Generic CORDIC Algorithm                              | 25 |

|   | 3.2  | Extension to Linear and Hyperbolic functions          | 30 |

|   | 3.3  | CORDIC in Hardware                                    | 32 |

|   | 3.4  | Hardware Performance Analysis                         | 35 |

|   | 3.5  | Summary                                               | 36 |

| 4 | Disc | crete Cosine Integer Transform (DCIT)                 | 37 |

|   | 4.1  | Introduction of DCIT                                  | 37 |

|   | 4.2  |                                                       | 39 |

|   |      | 4.2.1 The DCT Background                              | 39 |

|   |      | 4.2.2 The CORDIC based Loeffler DCT                   |    |

|   |      | $4.2.3$ $4\times4$ Integer Transform                  | 42 |

|   |      | 4.2.4 8×8 Integer Transform                           | 43 |

|   | 4.3  | Discrete Cosine and Integer Transform                 | 46 |

|   |      | 4.3.1 Forward DCIT                                    | 46 |

|   |      | 4.3.2 Inverse DCIT                                    | 48 |

|   | 4.4  | The p    | proposed 2–D QDCIT framework                   | 51  |

|---|------|----------|------------------------------------------------|-----|

|   |      | 4.4.1    | The 2–D QDCIT                                  | 51  |

|   |      | 4.4.2    | The CORDIC based Scaler                        |     |

|   |      | 4.4.3    | The CORDIC-Scaler Configurator and the LUT     |     |

|   |      |          | Read Module                                    | 57  |

|   |      | 4.4.4    | The Post-Quantizer                             | 61  |

|   | 4.5  | Exper    | rimental Results                               |     |

|   |      | 4.5.1    | Variable Iteration Steps of CORDIC             |     |

|   |      | 4.5.2    | ASIC Implementation                            |     |

|   |      | 4.5.3    | •                                              |     |

|   | 4.6  | Summ     | nary                                           |     |

| 5 | Para | allel Ja | cobi Algorithm                                 | 77  |

|   | 5.1  | Parall   | lel Eigenvalue Decomposition                   | 78  |

|   |      | 5.1.1    | Jacobi Method                                  | 78  |

|   |      | 5.1.2    | Jacobi EVD Array                               | 79  |

|   | 5.2  | Archit   | tecture Consideration                          | 81  |

|   |      | 5.2.1    | Conventional CORDIC Solution                   | 81  |

|   |      | 5.2.2    | Simplified $\mu$ -rotation CORDIC              | 83  |

|   |      | 5.2.3    | Adaptive $\mu$ -CORDIC iterations              | 85  |

|   |      | 5.2.4    | Exchanging inner and outer iterations          |     |

|   | 5.3  | Exper    | rimental Results                               |     |

|   |      | 5.3.1    | Matlab Simulation                              |     |

|   |      | 5.3.2    | Using threshold methods                        |     |

|   |      | 5.3.3    | Configurable Jacobi EVD Array                  |     |

|   |      | 5.3.4    | Circuit Implementation                         |     |

|   | 5.4  | Summ     | nary                                           | 98  |

| 6 | •    |          | trix-Vector Multiplication on Network-on-Chip  |     |

|   | 6.1  |          | duction of Sparse Matrix–Vector Multiplication |     |

|   | 6.2  |          | M on Network-on-Chip                           |     |

|   |      | 6.2.1    | Sparse Matrix-Vector Multiplication            |     |

|   |      | 6.2.2    | Conjugate Gradient Solver                      | 105 |

|   |      | 6.2.3    | Basic Idea                                     |     |

|   | 6.3  | Imple    | mentation                                      |     |

|   |      | 6.3.1    | Packet Format                                  | 108 |

|   |      | 6.3.2    | Switch Architecture                            |     |

|   |      | 6.3.3    | Pipelined Switch Architecture                  | 111 |

|   |      | 6.3.4    | Routing Algorithm                              |     |

|   |      | 6.3.5    | Processing Element                             | 113 |

|   |      |          |                                                |     |

|    |                    | 6.3.6              | Data Mapping                |  | 113 |

|----|--------------------|--------------------|-----------------------------|--|-----|

|    | 6.4                | Exper              | imental Result              |  | 115 |

|    |                    | 6.4.1              | FPGA Implementation         |  | 115 |

|    |                    | 6.4.2              | Influence of the Sparsity   |  | 116 |

|    |                    | 6.4.3              | Mapping to Iterative Solver |  | 118 |

|    | 6.5                | Summ               | nary                        |  | 120 |

| 7  | Con                | clusion            | S                           |  | 121 |

| Α  | Арр                | endix <sup>-</sup> | Tables                      |  | 125 |

| В  | B Appendix Figures |                    |                             |  | 129 |

| Bi | Bibliography 1     |                    |                             |  | 137 |

# **List of Figures**

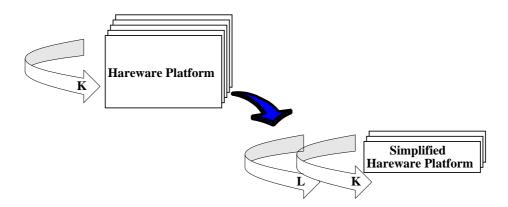

| 1.1<br>1.2 | Designer productivity gap (modified from SEMATECH)  Iterative algorithm design concept                                               |

|------------|--------------------------------------------------------------------------------------------------------------------------------------|

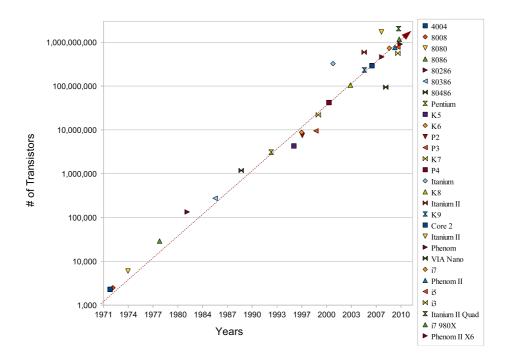

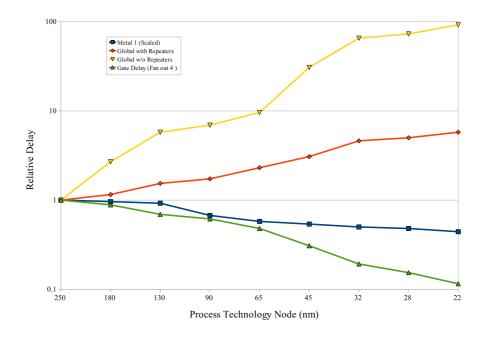

| 2.1        | Moore's Law: Plot of x86 CPU transistor counts from 1970 until 2010                                                                  |

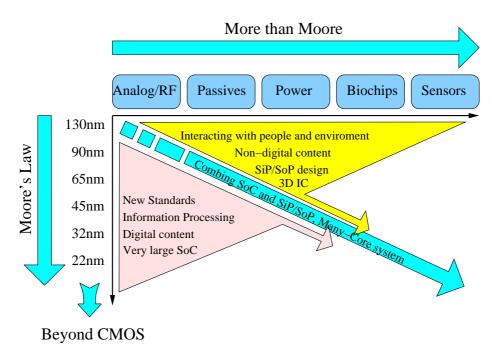

| 2.2        | IC scaling roadmap for More than Moore (modified figure from 2009 International Technology Roadmap for Semi-                         |

| 2.3        | conductors Executive Summary) [58]                                                                                                   |

| 2.0        | level (regenerated figure from International Technology                                                                              |

| 0.4        | Roadmap for Semiconductors 2003) [57]                                                                                                |

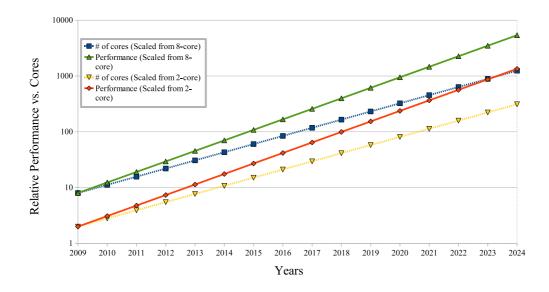

| 2.4        | The prediction of future multi-core SoC performance (regenerated figure from 2009 International Technology Roadmap                   |

|            | for Semiconductors System Drivers) [59]                                                                                              |

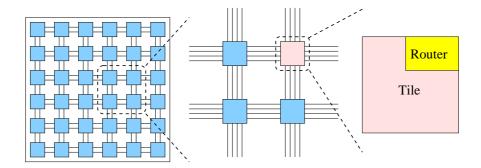

| 2.5        | A typical NoC architecture with a mesh style packet-                                                                                 |

|            | switched network                                                                                                                     |

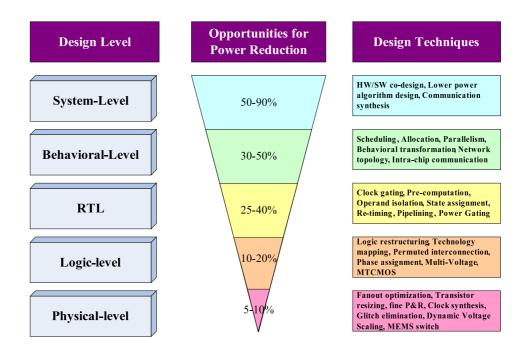

| 2.6        | Power reduction at each design level [88]                                                                                            |

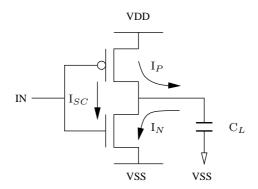

| 2.7        | A simple CMOS inverter                                                                                                               |

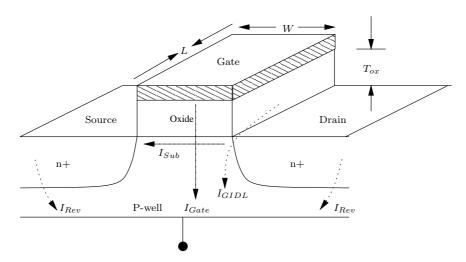

| 2.8        | There are four components of leakage sources in NMOS:                                                                                |

|            | Subthreshold leakage $(I_{Sub})$ , Gate-oxide leakage $(I_{Gate})$ ,<br>Reverse biased junction leakage $(I_{Rev})$ and Gate Induced |

|            | Drain Leakage $(I_{GIDL})$                                                                                                           |

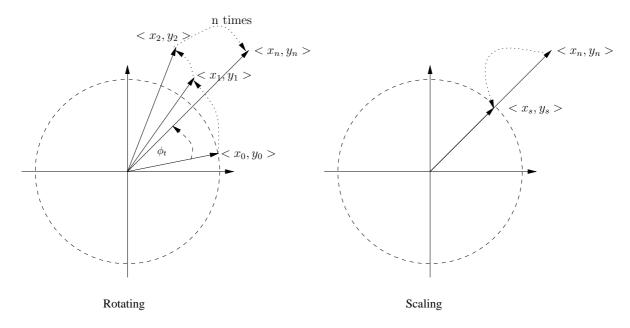

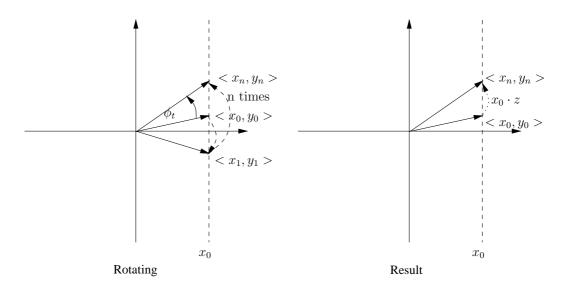

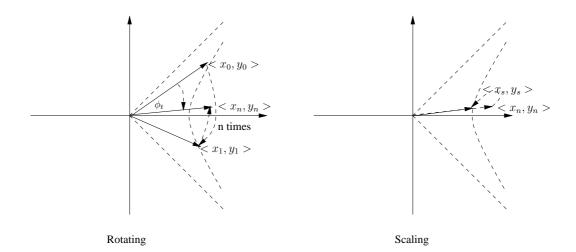

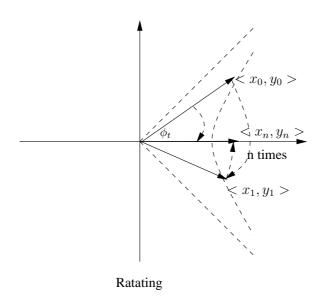

| 3.1        | CORDIC rotating and scaling a input vector $\langle x_0, y_0 \rangle$ in the orthogonal rotation mode                                |

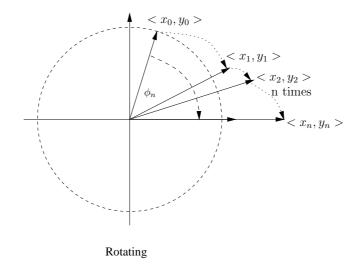

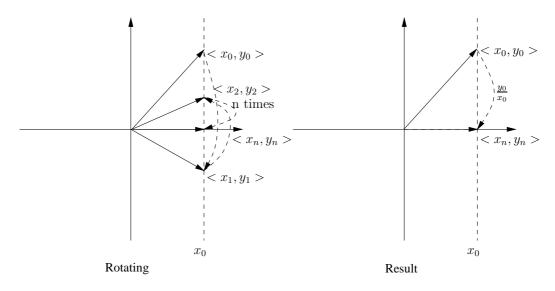

| 3.2        | CORDIC rotating a input vector $\langle x_0, y_0 \rangle$ in the or-                                                                 |

| 3.2        | thogonal vector mode                                                                                                                 |

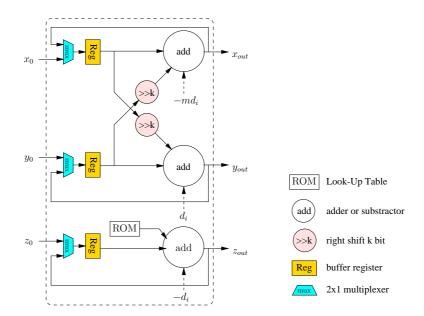

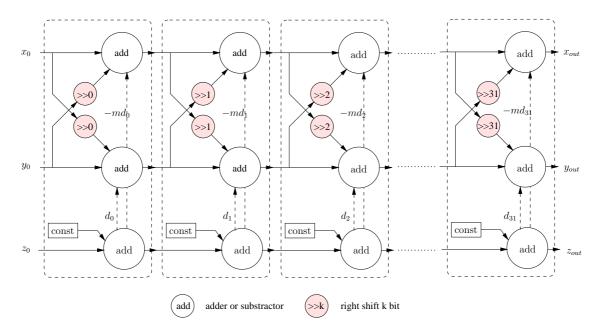

| 3.3        | Flow graph of a folded CORDIC (recursive) processor 33                                                                               |

| 3.4        | Flow graph of an unfolded (parallel) CORDIC processor 34                                                                             |

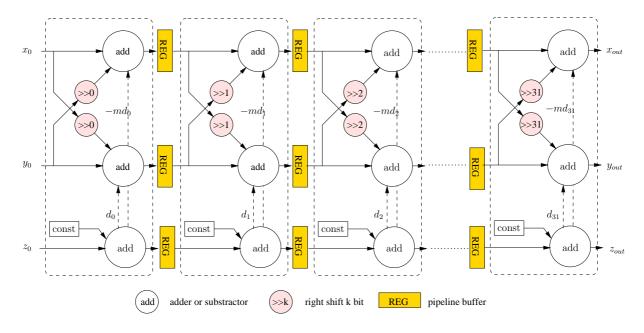

| 3.5        | Flow graph of an unfolded (parallel) CORDIC processor                                                                                |

|            | with pipelining $\dots \dots 34$                                                                                                     |

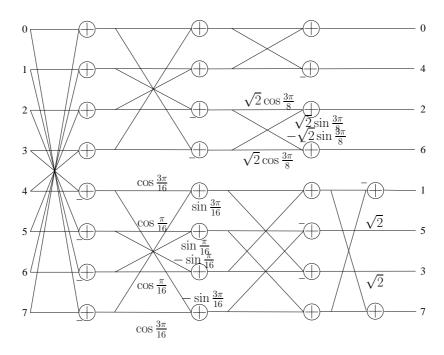

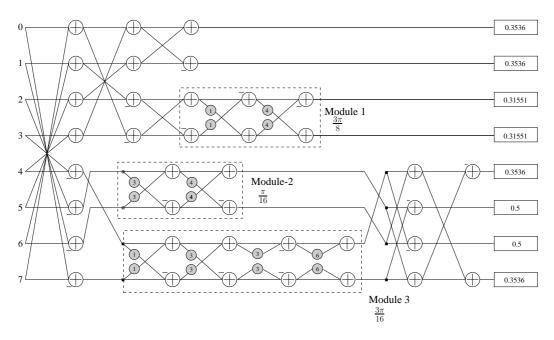

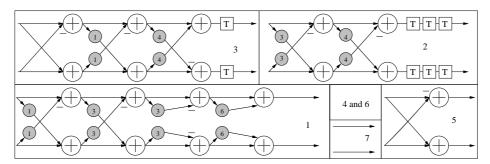

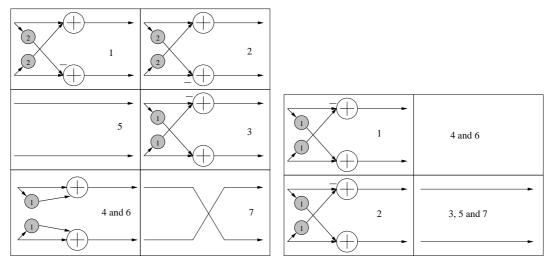

| 4.1        | Flow graph of an 8-point Loeffler DCT architecture 41                                                                                |

| 4.2  | Flow graph of an 8-point CORDIC based Loeffler DCT       |                |

|------|----------------------------------------------------------|----------------|

|      | -                                                        | 42             |

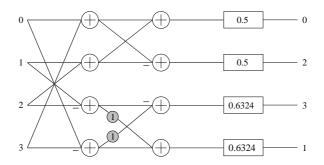

| 4.3  | Flow graph of the 4-point integer transform in H.264     | 44             |

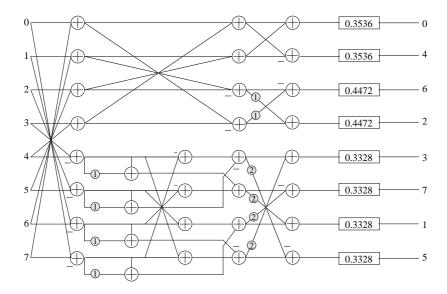

| 4.4  | Flow graph of the 8-point integer transform in H.264     | 46             |

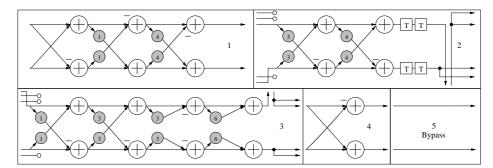

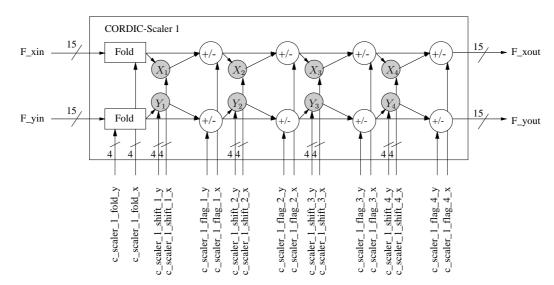

| 4.5  | Flow graph of an 8-point FDCIT Transform with five       |                |

|      | configurable modules for multiplierless DCT and integer  |                |

|      |                                                          | 47             |

| 4.6  |                                                          | 48             |

| 4.7  | Flow graph of an 8-point IDCIT Transform with seven      |                |

|      | configurable modules for multiplierless IDCT and inverse |                |

|      | integer transforms                                       | 49             |

| 4.8  | Three sub flow graphs of the modules of Figure 4.7       | 50             |

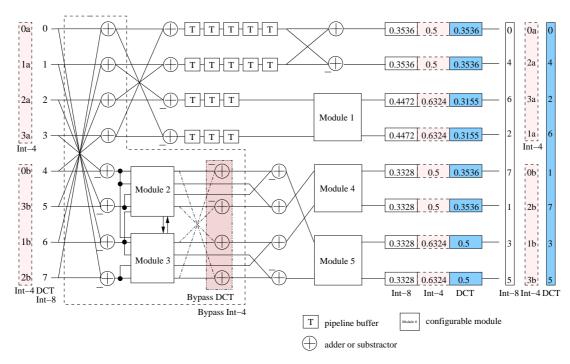

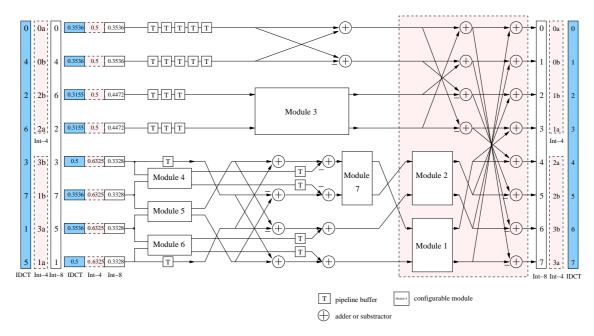

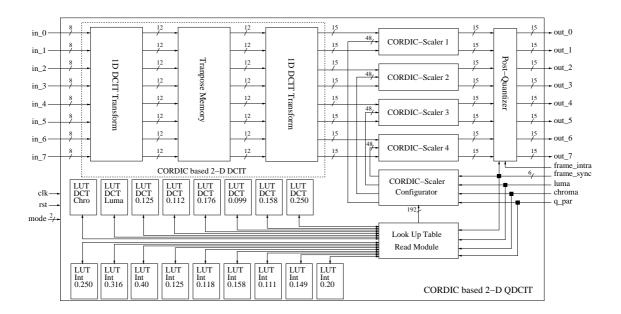

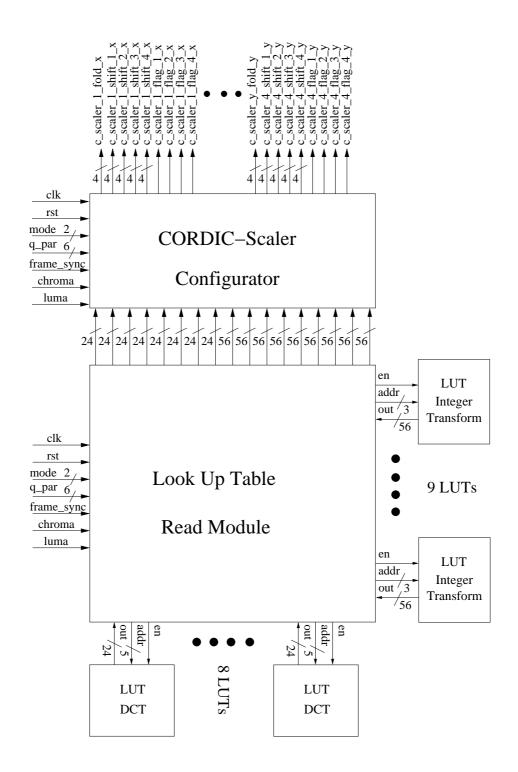

| 4.9  | The framework of the proposed CORDIC based 2-D FQD-      |                |

|      | CIT with four CORDIC-Scalers, a Post-Quantizer, a CORDI  | C-             |

|      | Scaler Configurator, a LookUp Table Read Module and      |                |

|      | 17 dedicated LUTs (8 are for DCT and the other 9 are     |                |

|      | 9                                                        | 52             |

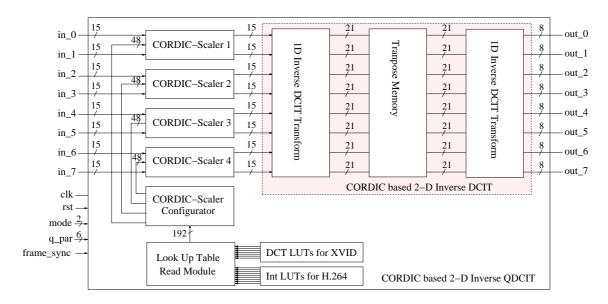

| 4.10 | Framework of a CORDIC based 2-D IQDCIT                   | 53             |

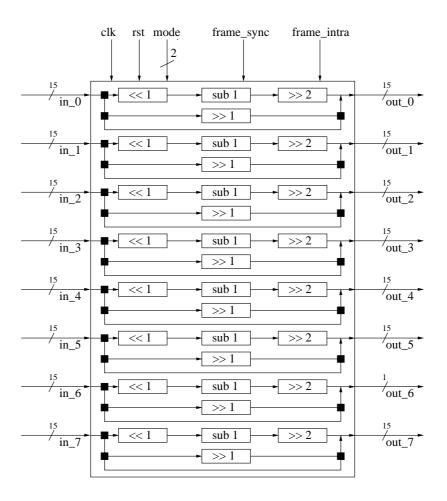

| 4.11 | Schematic view of the first CORDIC-Scaler with one Fold  |                |

|      | 1 1                                                      | 54             |

| 4.12 | Schematic view and IOs of the LUT reader module and      |                |

|      | 9                                                        | 60             |

|      | •                                                        | 62             |

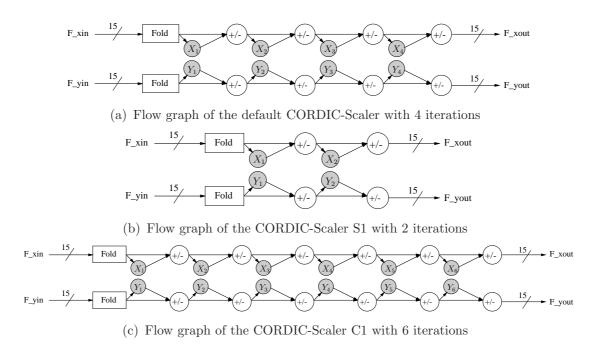

| 4.14 | Three flow graphs of CORDIC-Scaler with different num-   |                |

|      | 1                                                        | 65             |

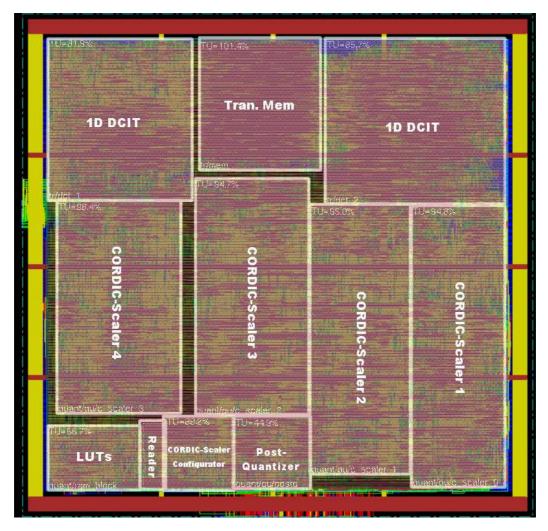

| 4.15 | Final layout view of the 2–D CORDIC based FQDCIT         |                |

|      | 1 00 0                                                   | 66             |

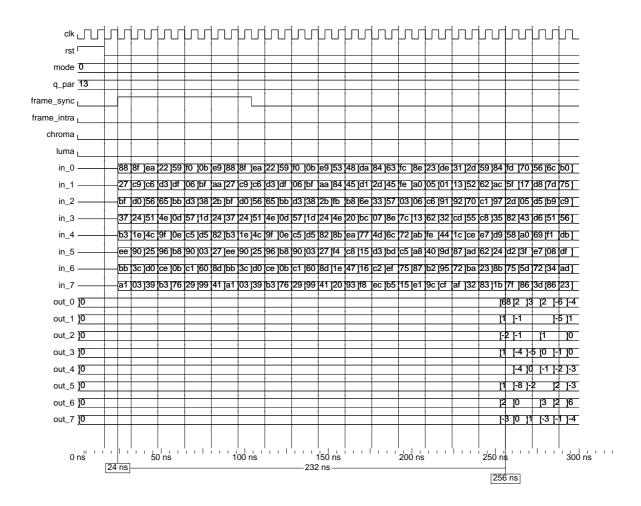

| 4.16 | Timing waveform of the 2–D CORDIC based FQDCIT           | 0.0            |

|      | (1)                                                      | 68             |

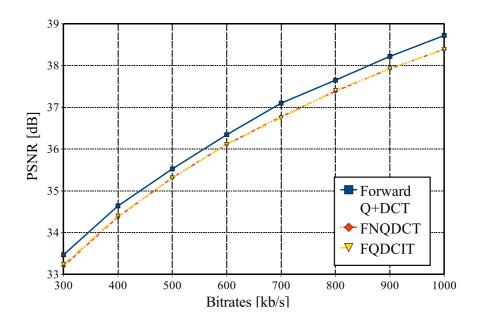

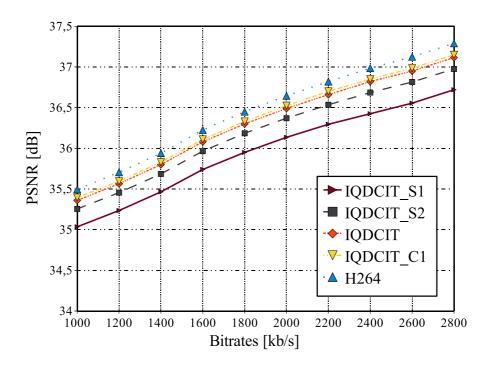

| 4.17 | The average Forward Q+DCT, FNQDCT and FQDCIT             |                |

|      | PSNR of the "foreman" and "paris" cif video test from    | <del>7</del> 1 |

| 4 10 | 9                                                        | 71             |

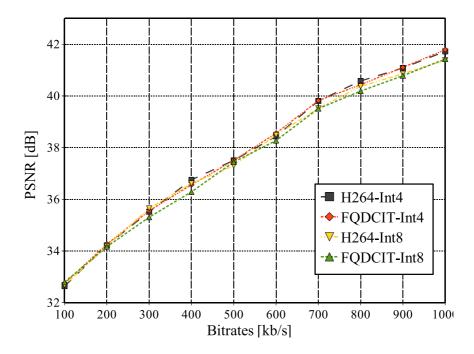

| 4.18 | The average FQDCIT PSNR of the "foreman" and "paris"     | <b>7</b> 1     |

| 4.10 | cif video test from low to high bitrates in H.264        | 71             |

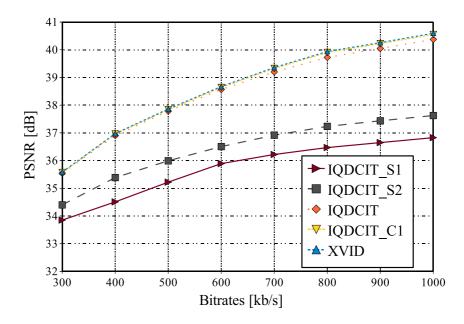

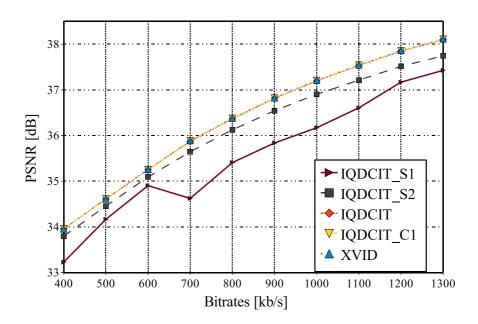

| 4.19 | The average IQDCIT PSNR of the "foreman", "paris"        |                |

|      | and "news" cif video test from low to high bitrates in   | 79             |

| 4.00 | XVID                                                     | 72             |

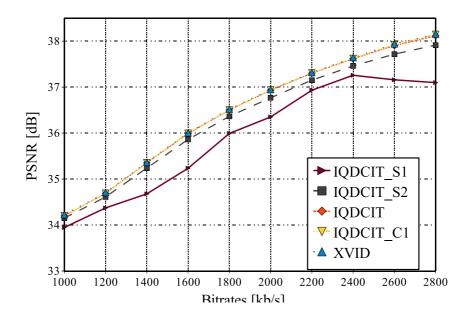

| 4.20 | The average IQDCIT PSNR of the "crew" and "ice"          | 79             |

|      | DVD video test from low to high bitrates in XVID         | 73             |

| 4.21 | The average IQDCIT PSNR of the "rush hour" and "blue sky" Full–HD video test from low to high bitrates in XVID                                                                                                                           | 73       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

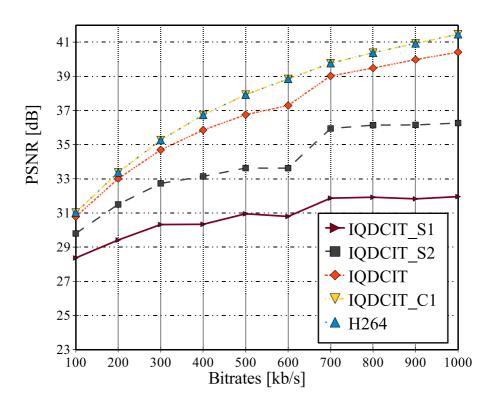

| 4.22 | The average IQDCIT PSNR of the "foreman", "paris" and "news" cif video test from low to high bitrates in                                                                                                                                 |          |

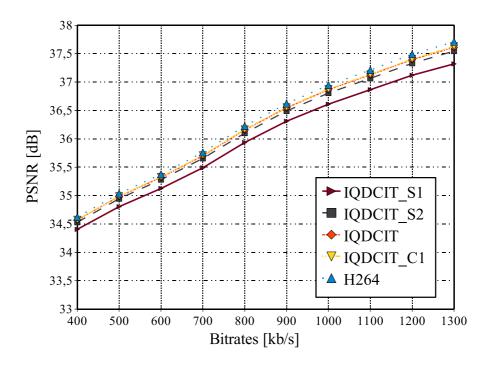

| 4.23 | H.264                                                                                                                                                                                                                                    | 74       |

| 4.24 | DVD video test from low to high bitrates in H.264  The average IQDCIT PSNR of the "rush hour" and "blue                                                                                                                                  | 75<br>76 |

|      | sky" Full-HD video test from low to high bitrates in H.264                                                                                                                                                                               | 76       |

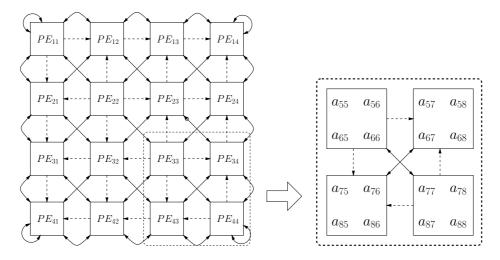

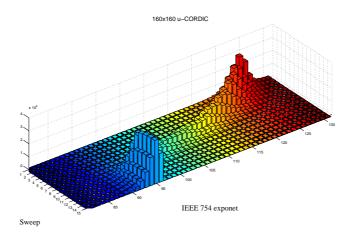

| 5.1  | A 4×4 EVD array, where n=8 for 8×8 symmetric matrix                                                                                                                                                                                      | 80       |

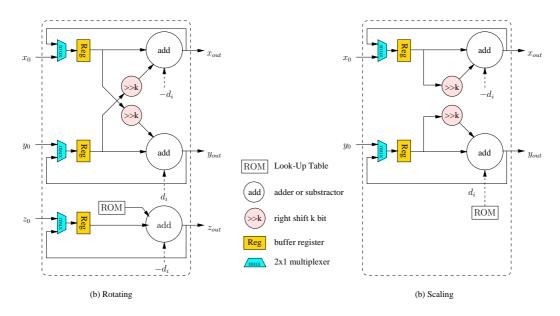

| 5.2  | Flow graph of a folded CORDIC (recursive) processor with the scaling                                                                                                                                                                     | 83       |

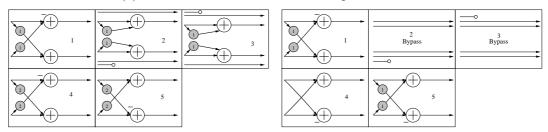

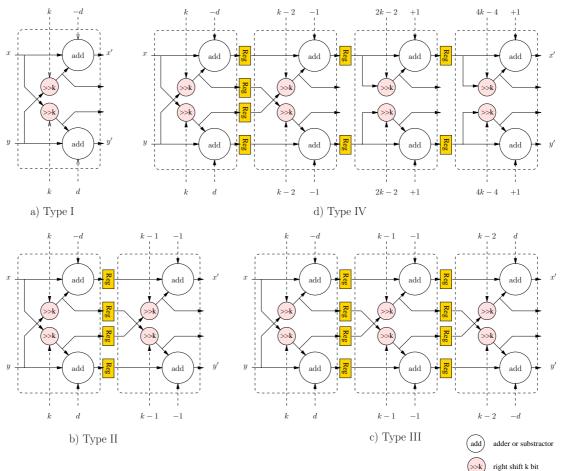

| 5.3  | Four simplified CORDIC rotation types                                                                                                                                                                                                    | 84       |

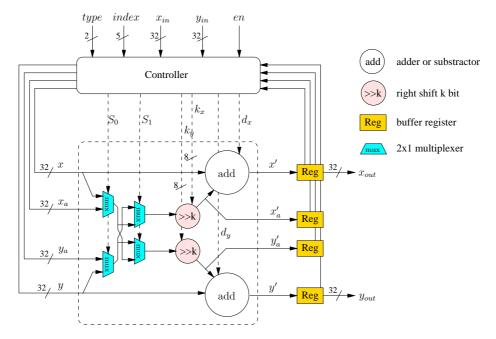

| 5.4  | The block diagram of a scaling–free $\mu$ –CORDIC PE, including 2 adders, 2 shifters and 4 multiplexers                                                                                                                                  | 86       |

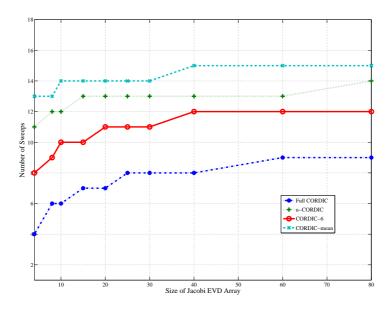

| 5.5  | The average number of sweeps vs. array sizes for four rotation methods ( $\mu$ -CORDIC, Full CORDIC and two adaptive methods)                                                                                                            | 87       |

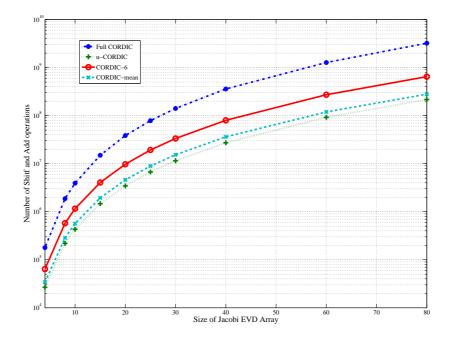

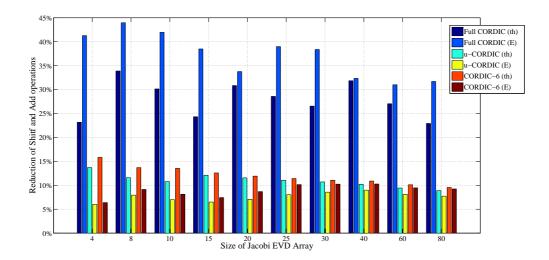

| 5.6  | The number of shift—add operations for four rotation methods on different size of array                                                                                                                                                  | 89       |

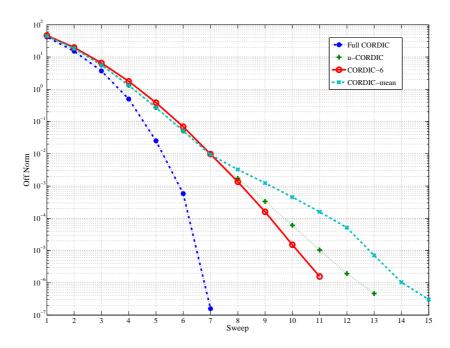

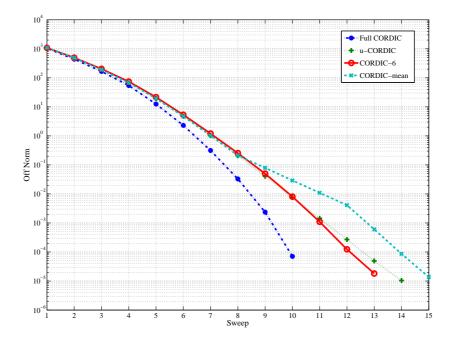

| 5.7  | The required number of sweeps vs. off-diagonal norm for 10×10 Jacobi EVD array with double floating precision.                                                                                                                           | 90       |

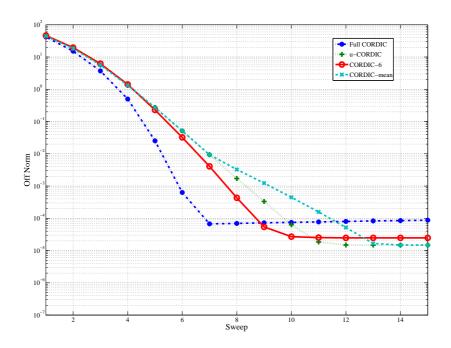

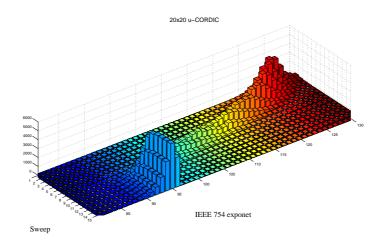

| 5.8  | The required number of sweeps vs. off-diagonal norm for $80\times80$ Jacobi EVD array with double floating precision .                                                                                                                   | 91       |

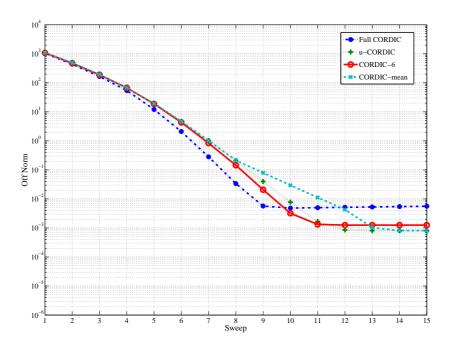

| 5.9  | The required number of sweeps vs. off-diagonal norm for $10\times10$ Jacobi EVD array with single floating precision .                                                                                                                   | 92       |

| 5.10 | The required number of sweeps vs. off-diagonal norm for                                                                                                                                                                                  |          |

| 5.11 | $80\times80$ Jacobi EVD array with single floating precision . The reduction of shift—add operations (in percent) for three rotation methods with the threshold strategy and preconditioned $E$ index on different size of array in IEEE | 93       |

| 5.12 | 754 single floating precision                                                                                                                                                                                                            | 94       |

| 5.13 | single floating precision                                                                                                                                                                                                                | 95       |

|      | single floating precision                                                                                                                                                                                                                | 95       |

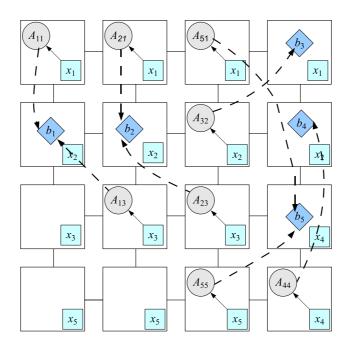

| 5.14       | The locations of six different PE types in a 4×4 Jacobi EVD array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

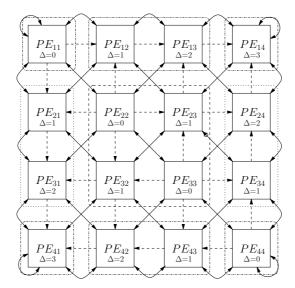

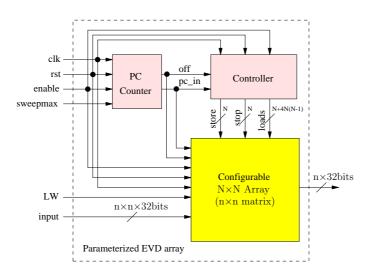

|            | A configurable parallel Jacobi EVD design 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

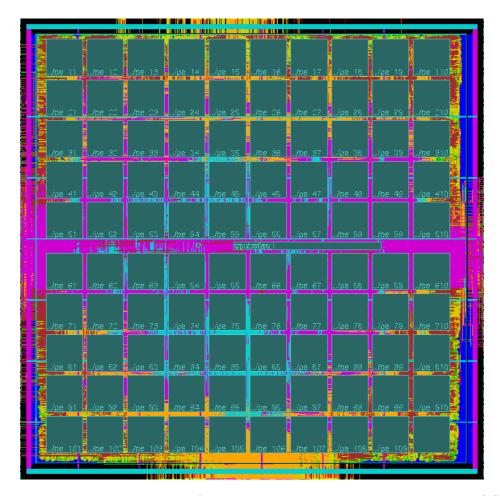

|            | Final layout view of a $10\times10$ Jacobi EVD array with the $\mu$ -CORDIC PE with TSMC 45nm technology library 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

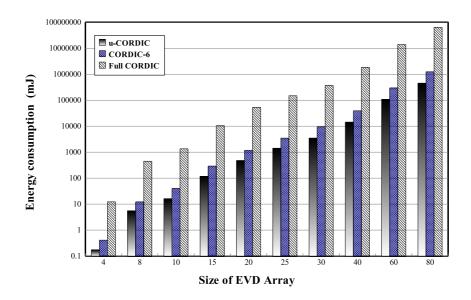

| 5.17       | The energy consumption per EVD operation with each size of EVD array (operating at 100 MHz) 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

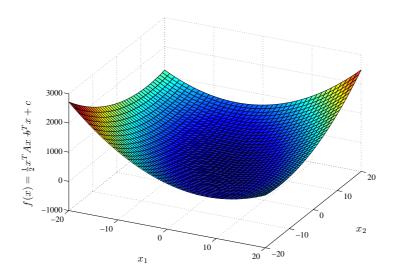

| 6.1        | The quadratic surface of the $f(x)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

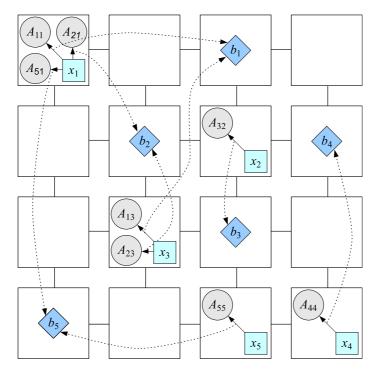

| 6.2        | A direct mapping of parallel SMVM operations based on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

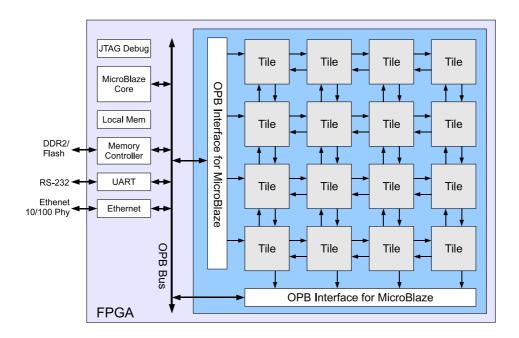

| 6.3        | the NoC architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0.0        | Virtex-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

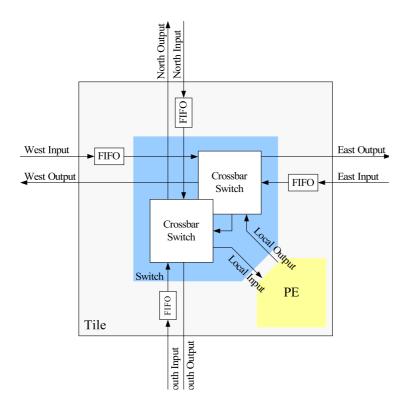

| 6.4        | Detailed switch interconnection including two 3×3 cross-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            | bars, five I/O ports and four FIFOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

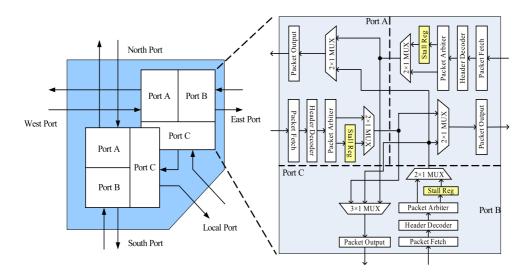

| 6.5        | A 5-stage pipelined switch with two 3×3 crossbars, five                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | I/O ports and four FIFOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

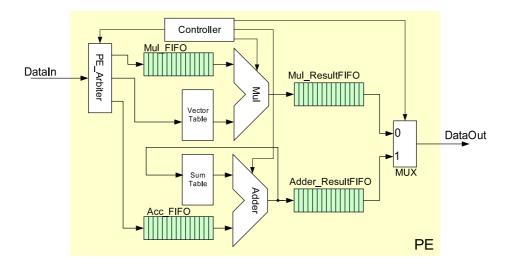

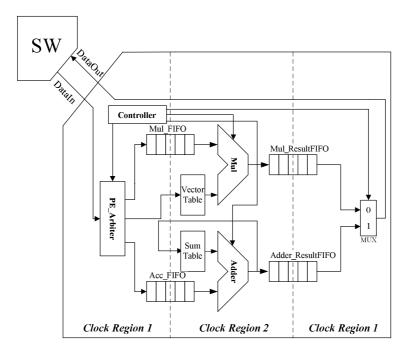

| 6.6        | Schematic view of the PE for the SMVM–NoC platform . 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

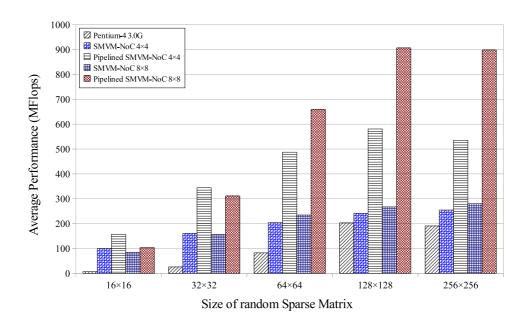

| 6.7        | Performance analysis of different matrix size with ran-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | dom sparsity on the Pentium-4 PC, non-pipelined 4×4/8×8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | SMVM-NoC, $4\times4/8\times8$ pipelined SMVM-NoC (operational control of the second state of th |

| 0.0        | ing at 200MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

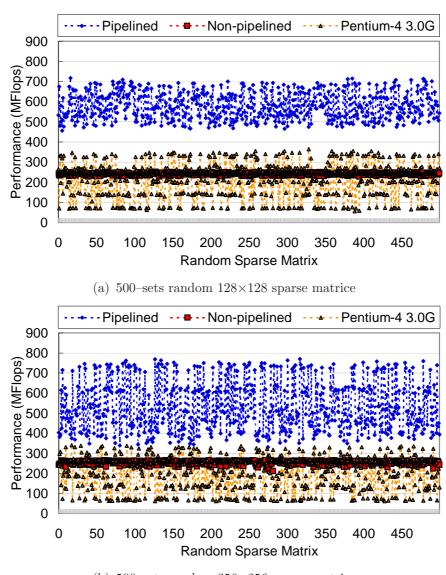

| 6.8        | Influence of sparsity on different architectures with ran-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <i>c</i> 0 | dom sparsity from 10% to 50%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

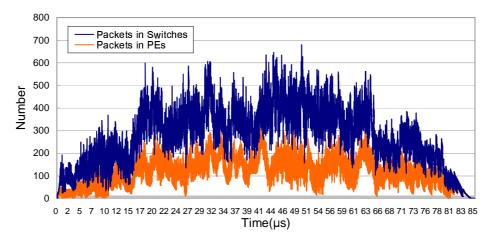

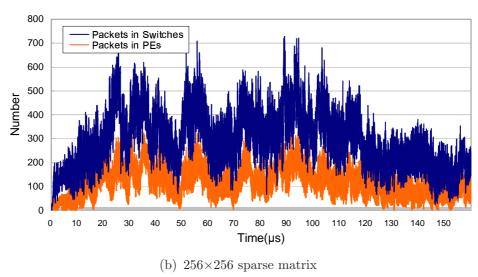

| 6.9        | Analysis of the packet traffics for the 4×4 pipelined SMVM–NoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.10       | Two clock regions for the PE and the switch, one for PE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0.10       | running at higher frequency, another lower frequency 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| B.1        | CORDIC linear rotation mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| B.2        | CORDIC linear vector mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| В.3        | CORDIC hyperbolic rotation mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| B.4        | CORDIC hyperbolic vector mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| B.5        | Seven video sequences for test the QDCIT transformation 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |