## Dissertation

zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften in der Fakultät Physik der Technischen Universität Dortmund

# Slim Edge Studies, Design and Quality Control of Planar ATLAS IBL Pixel Sensors

vorgelegt von

Tobias Wittig Lehrstuhl für Experimentelle Physik IV Fakultät für Physik Technische Universität Dortmund

Dortmund, April 2013

Dissertation zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften in der Fakultät Physik der Technischen Universität Dortmund

## Slim Edge Studies, Design and Quality Control of Planar ATLAS IBL Pixel Sensors

vorgelegt von

Tobias Wittig Lehrstuhl für Experimentelle Physik IV Fakultät für Physik Technische Universität Dortmund

Dortmund, April 2013

Gutachter: Zweitgutachter: Beisitzer: Termin der mündlichen Prüfung: Prof. Dr. C. Gößling, TU DortmundProf. Dr. Dr. W. Rhode, TU DortmundDr. B. Siegmann, TU Dortmund8. Mai 2013

# Contents

| 1. | Introduction          |                                                        |               |  |  |  |  |

|----|-----------------------|--------------------------------------------------------|---------------|--|--|--|--|

| 2. |                       | LHC and the Present ATLAS Detector                     | <b>3</b><br>3 |  |  |  |  |

|    |                       | ATLAS Detector                                         | 4             |  |  |  |  |

| 3. | ATLAS Pixel Sensors 7 |                                                        |               |  |  |  |  |

|    | 3.1.                  | Functionality of Planar Silicon Sensors                | 7             |  |  |  |  |

|    |                       | 3.1.1. Leakage Current                                 | 8             |  |  |  |  |

|    |                       | 3.1.2. Particle Detection                              | 8             |  |  |  |  |

|    | 3.2.                  | Radiation Damage in Silicon Semiconductors             | 9             |  |  |  |  |

|    |                       | 3.2.1. General Radiation Effects                       | 9             |  |  |  |  |

|    |                       | 3.2.2. Annealing                                       | 10            |  |  |  |  |

|    | 3.3.                  | Design of ATLAS Pixel Sensors                          | 11            |  |  |  |  |

|    | 3.4.                  | Modules and Read-Out Cards                             | 14            |  |  |  |  |

|    |                       | 3.4.1. Front End Chip                                  | 14            |  |  |  |  |

|    |                       | 3.4.2. Bump Bonding                                    | 15            |  |  |  |  |

|    |                       | 3.4.3. Modules                                         | 16            |  |  |  |  |

|    |                       | 3.4.4. Read-Out Cards                                  | 16            |  |  |  |  |

|    | 3.5.                  | Stave Assembly                                         | 17            |  |  |  |  |

| 4. | Plan                  | is for ATLAS Upgrades                                  | 19            |  |  |  |  |

|    |                       | LHC Schedule                                           | 19            |  |  |  |  |

|    | 4.2.                  | ATLAS Pixel Upgrades                                   | 19            |  |  |  |  |

|    |                       | 4.2.1. IBL                                             | 20            |  |  |  |  |

|    |                       | 4.2.2. New Inner Detector                              | 21            |  |  |  |  |

|    | 4.3.                  | Sensor Improvements                                    | 22            |  |  |  |  |

|    |                       | 4.3.1. Slim Edges                                      | 22            |  |  |  |  |

|    |                       | 4.3.2. IBL Sensor Production                           | 22            |  |  |  |  |

| 5. | Prot                  | otype Sensor Studies                                   | 25            |  |  |  |  |

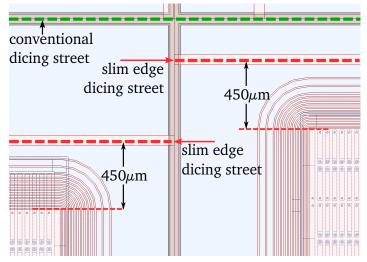

|    | 5.1.                  | Slim Edge Dicing Trials on Sensors                     | 25            |  |  |  |  |

|    |                       | 5.1.1. Dicing Trials                                   | 25            |  |  |  |  |

|    |                       | 5.1.2. Results after Irradiation                       | 28            |  |  |  |  |

|    |                       | 5.1.3. Discussion                                      | 30            |  |  |  |  |

|    | 5.2.                  | Leakage Current Dependencies of Irradiated Sensors     | 31            |  |  |  |  |

|    |                       | 5.2.1. Temperature Dependencies                        | 31            |  |  |  |  |

|    |                       | 5.2.2. Annealing Studies                               | 32            |  |  |  |  |

|    | 5.3.                  | Design of the Prototype Sensors                        | 34            |  |  |  |  |

|    |                       | 5.3.1. Modifications to the Present ATLAS Pixel Sensor | 34            |  |  |  |  |

|    |                       | 5.3.2. Sensor Edge Design                              | 34            |  |  |  |  |

|    |                       | 5.3.3. Wafer Overview                                  | 36            |  |  |  |  |

|     | 5.4. | Quality Inspection of the Prototype Production         | 38           |

|-----|------|--------------------------------------------------------|--------------|

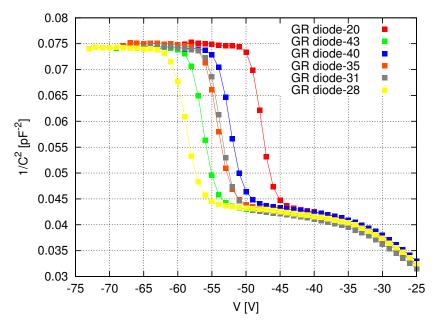

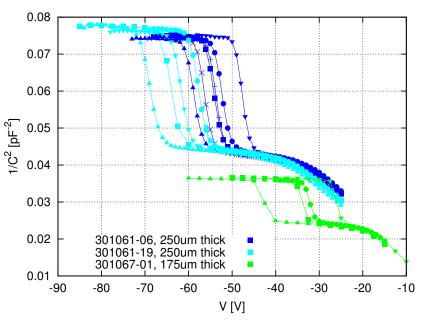

|     |      | 5.4.1. CV Measurements                                 | 39           |

|     |      | 5.4.2. IV Measurements                                 | 41           |

|     |      | 5.4.3. Discussion of Different Sensor Bulk Thicknesses | 46           |

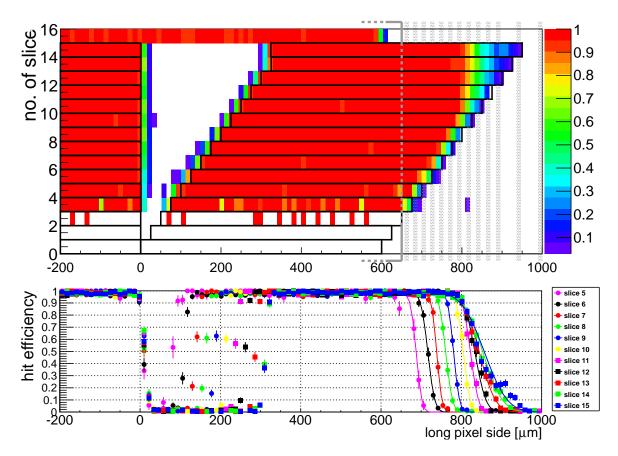

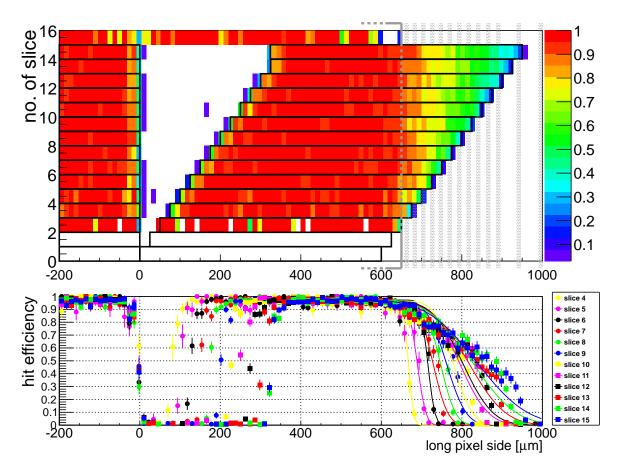

|     | 5.5. | Test Beam Results                                      | 48           |

|     |      | 5.5.1. Test Beam Operation                             | 48           |

|     |      | 5.5.2. FE-I4 Based Assemblies                          | 49           |

|     |      | 5.5.3. FE-I3 Based Assemblies                          | 55           |

|     |      | 5.5.4. Summary of Edge Efficiencies                    | 62           |

| 6.  | IBL  | Sensor                                                 | 65           |

|     | 6.1. | Design of Planar IBL Sensors                           | 65           |

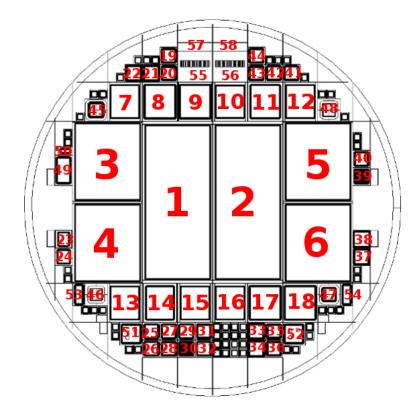

|     | -    | 6.1.1. Global Wafer Design                             | 65           |

|     |      | 6.1.2. Final Sensor Layout                             | 67           |

|     | 6.2. | IBL Planar Wafer Production                            | 68           |

|     | 6.3. | Quality Control                                        | 69           |

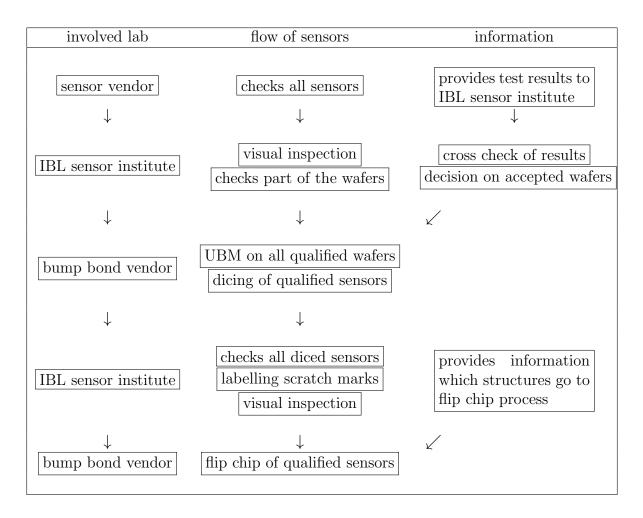

|     |      | 6.3.1. Quality Assurance Steps                         | 69           |

|     |      | 6.3.2. Quality Criteria                                | 71           |

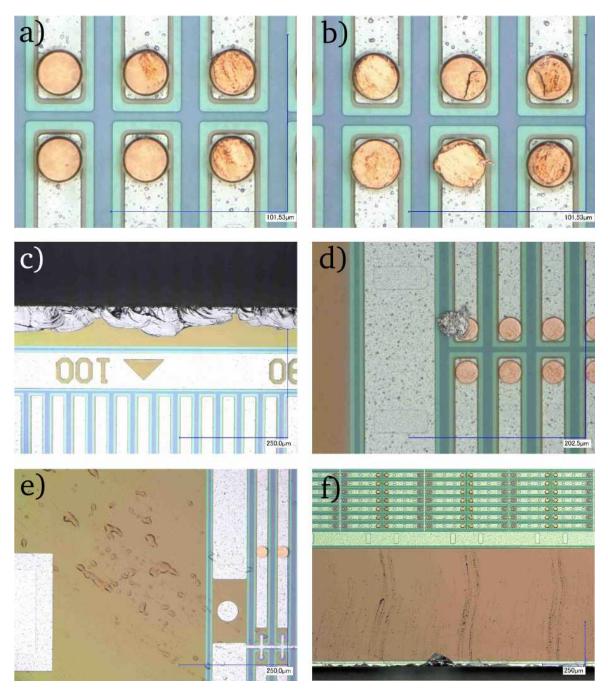

|     |      | 6.3.3. Visual Inspection                               | 72           |

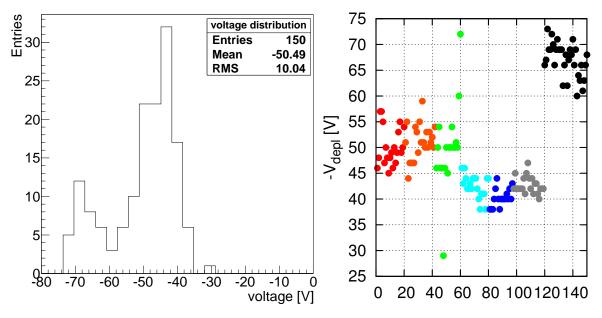

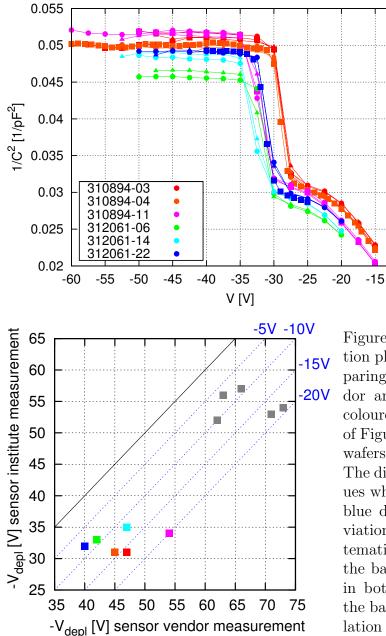

|     |      | 6.3.4. CV Measurements                                 | $74^{-1}$    |

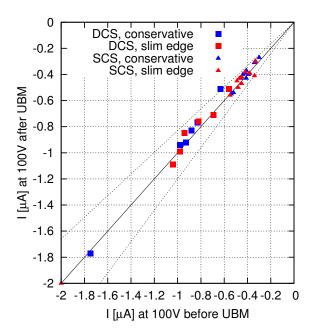

|     |      | 6.3.5. IV Measurements                                 | 77           |

|     |      | 6.3.6. Summary of the Quality Control                  | 84           |

| 7.  | Futi | ire ATLAS Pixel Upgrades                               | 89           |

| ••• | 7.1. |                                                        | 89           |

|     | 7.2. |                                                        | 90           |

|     |      | 7.2.1. Edge Design Improvements                        | 90           |

|     |      | 7.2.2. Modifications to Pixel Implantations            | 92           |

|     |      | 7.2.3. Modifications to the Bias Grid Design           | 94           |

|     |      | 7.2.4. On-Sensor Temperature Resistors                 | 94           |

| 8.  | Con  | clusions and Outlook                                   | 103          |

| ^   | Date | ailed Overview Tables of the Production Wafer          | 105          |

| А.  |      |                                                        | 105          |

|     |      | · -                                                    | $105 \\ 107$ |

|     | A.2. |                                                        | 107          |

| Β.  | Test | Beam Results                                           | 109          |

## 1. Introduction

In the 20th century the massive progresses of the particle physics have led to a deep understanding of the microscopic structure of the universe. The investigations and characterizations of the elementary particles and the fundamental forces have resulted in the standard model. It consists of three generations of quarks and leptons and four gauge bosons. Latter are the exchange particles of the three forces: The electromagnetism, the strong nuclear and the weak nuclear interaction. The gravitation is not included. The deeper understanding of matter and interactions was enabled by the advance to smaller scales which became possible because of particle accelerators running at ever increasing energies. The collisions at the interaction points generate new particles which are detected by detector systems which have become increasingly complex featuring more precise measurement techniques, higher resolution and a faster read-out. An increasing processing speed and computing power additionally enable to cope with high luminosities and thus to collect high statistics.

The LHC is currently the largest ring collider. With energies up to 7 + 7 TeV and a design luminosity of  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>, it enables the exploration of rare and high-energetic processes. The discovery of a new particle with a mass around 126 GeV, published in July 2012, represents one outstanding success of the operation of the LHC. At the time being, the assumption that the particle is a Higgs boson is more and more likely. This could represent the last missing component of the standard model. However, the standard model is limited and does not describe various matters which will have to be investigated in the future. Further fields of investigations are for example the description of the Higgs mechanism, a Grand Unified Theory, the super symmetry and the CP violation which could explain the asymmetry of matter and antimatter in the universe. Improvements of accelerators and detectors are hence mandatory in the future to explore beyond the standard model.

One of the four large experiments at the LHC is the ATLAS detector, a multi purpose detector. Its pixel detector, composed of three layers, is the innermost part of the tracker. As it is closest to the interaction point, it represents a basic part of the track reconstruction. Besides the requested high resolution one main requirement is the radiation hardness. In the coming years the radiation damage will cause deteriorations of the detector performance. With the planned increase of the luminosity, especially after the upgrade to the High Luminosity LHC, this radiation damage will be even intensified. This circumstance necessitates a new pixel detector featuring improved radiation hard sensors and read-out chips.

The present shutdown of the LHC is already utilized to insert an additional b-layer (IBL) into the existing ATLAS pixel detector. The current  $n^+$ -in-n pixel sensor design had to be adapted to the new read-out chip and the module specifications. The new stave geometry requests a reduction of the inactive sensor edge. In a prototype wafer production (Chapter 5) all modifications have been implemented. The sensor quality control was supervised which led to the decision of the final sensor thickness. In order

#### 1. Introduction

to evaluate the performance of the sensor chip assemblies with an innovative slim edge design, they have been operated in test beam setups before and after irradiation.

The second main topic of this thesis is the quality control of the planar IBL sensor wafer production (Chapter 6). The production was supervised from the stage of wafer delivery to that before the flip chip process. During the quality control, the most important measurements have been coordinated, analysed and documented to ensure that a sufficient amount of functional sensors are available for the module production.

In Chapter 7 improvements of the design and the dicing step are illustrated which are either already investigated or will be in the course of coming productions. They should help to cope with requirements and specifications of future ATLAS pixel detector upgrades concerning radiation hardness and slim edges.

# 2. The LHC and the Present ATLAS Detector

## 2.1. LHC

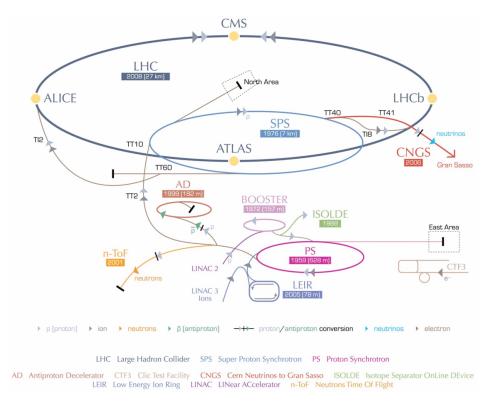

The Large Hadron Collider (LHC) at CERN, Geneva, is currently the world's largest particle accelerator. It is a ring collider with a circumference of 27 km where protons are accelerated to a maximum energy of 7 + 7 TeV. The high magnetic fields of up to 8.4 T which are required to deflect the beam, are generated by superconducting dipole magnets. The LHC is the last part of a chain of several pre-accelerators which form the CERN accelerator complex seen in Figure 2.1. At four interaction points, the

Figure 2.1.: Illustration of the CERN accelerator complex. [Lef06]

beams are crossed in order to provoke collisions and produce new particles. At each interaction point one of the four large experiments is located. These particle detectors are ALICE<sup>1</sup>, ATLAS<sup>2</sup>, CMS<sup>3</sup> and LHCb<sup>4</sup>. ALICE is a detector system specialized

<sup>&</sup>lt;sup>1</sup>A Large Ion Collider Experiment

<sup>&</sup>lt;sup>2</sup>A Toroidal LHC Apparatus

<sup>&</sup>lt;sup>3</sup>Compact Muon Solenoid

<sup>&</sup>lt;sup>4</sup>Large Hadron Collider beauty

in heavy ion collisions, LHCb one specialized in tests on CP violation in  $b\bar{b}$ -systems. ATLAS and CMS are multi purpose detectors. With a bunch crossing rate of 40 MHz, a design luminosity of  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> can be reached [LHC95].

In the first years of its operation starting in 2009, the LHC was operated at 3.5+3.5 TeV and 4+4 TeV. At the beginning of 2013, the first large machine shutdown started which will presumably last until spring of 2015. It is used to initiate first upgrades of the collider and the detectors. The total integrated luminosity which is collected so far is some tens of fb<sup>-1</sup> [LHCSt].

## 2.2. ATLAS Detector

The ATLAS experiment [Aad08a] is a  $4\pi$  multi purpose detector. One of its main goals is to prove or disprove the existence of the standard model Higgs boson as its mass has to be in the energy range of LHC. Due to the high luminosity and the associated high production rates, high statistic measurements up to the TeV scale can be done. Furthermore, the detector enables for example to do precision measurements of the top quark, to investigate the CP violation or new physics in terms of super symmetry.

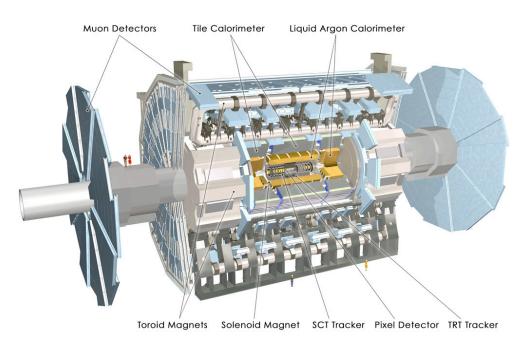

Figure 2.2.: Illustration of the ATLAS detector. [Apic]

The ATLAS detector has an overall diameter of 25 m, a length of 46 m and a weight of about 7000 t. It can be divided into subdetectors which are arranged cylinder symmetrically around the interaction point, see Figure 2.2. These are from the inside outwards the inner detector or tracker, the calorimeters and the muon detectors.

The tracker is enclosed by a solenoidal magnetic system which produces a nearly homogeneous field of 2 T causing track deflection for charged particles. The calorimeter is surrounded by superconducting toroidal air coils producing a magnetic field of more than 4 T for the muon spectrometer. The muon tracks are deflected and detected in high-precision tracking chambers.

The calorimeter is divided into an electromagnetic (EM) calorimeter and a hadronic calorimeter. Both are using the sampling technique to determine space resolved the energy of electrons respectively of hadron jets. They consist of alternating layers of passive absorber materials and scintillators with liquid Argon as an active medium.

The inner detector is consisting of the transition radiation tracker (TRT), the silicon strip detector (SCT) and the pixel detector. Its purpose is a high-precision measurement of the particle tracks. The number of layers is a compromise of higher track resolution and the increased probability of scattering due to a larger radiation length (see Section 3.1.2). Furthermore, it implicates high costs especially for the pixel detector.

The TRT consists of 4 mm thick straw tubes containing a xenon-based gas surrounding a sense wire. The particles crossing the tubes create transition radiation and are thus detected.

The SCT consists of silicon microstrip sensors in p<sup>+</sup>-in-n (see Section 3.1) technology. Each module has an area of  $6.36 \times 6.4 \text{ cm}^2$  with 768 read-out strips in a 80  $\mu$ m pitch. The cylindric barrel region of the detector has 8 layers where always two are mounted back-to-back at a 40 mrad angle in order to obtain a better tracking resolution which is in the order of 16  $\mu$ m in the radial direction ( $r\phi$ ) and 580  $\mu$ m along the beam pipe (z-direction).

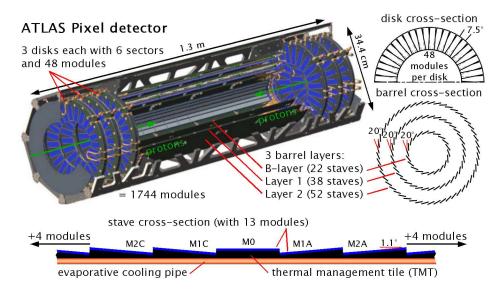

The pixel detector [ATL98, Aad08b] is the unit which is closest to the interaction point and thus the most important part of the tracking system especially for the b-tagging. A sketch is shown in Figure 2.3.

Figure 2.3.: Illustration of the ATLAS pixel detector [Bar02]. For further details see text.

The pixel detector consists of 1744 pixel modules (see Section 3.4.3). Around the interaction point, the modules are mounted consecutively on so called staves. The staves are forming three cylindrical barrel layers. The innermost one is called b-layer which illustrates its importance for the b-tagging efficiency.

Further modules are mounted on six end cap disks which complete the detector on

both sides for larger  $\eta$  values<sup>5</sup>. On each disk, the modules are placed back-to-back and staggered to maximize the detection efficiency.

The resolution of the pixel detector is  $12 \,\mu\text{m}$  in  $r\phi$ - and  $66 \,\mu\text{m}$  in z-direction for the barrel section. Including the disks it spans a pseudorapidity range  $|\eta| < 2.5$ .

The stave assembly is discussed in detail in Section 3.5.

<sup>&</sup>lt;sup>5</sup>pseudorapidity  $\eta = \ln(\tan \theta/2)$  with the polar angle  $\theta$  with respect to the beam axis

# 3. ATLAS Pixel Sensors

This chapter should help to understand the basic concepts which are necessary to understand the design, functionality and operation of the ATLAS pixel sensors. The first two sections give a brief introduction to silicon sensor technology. A detailed description of the band theory and the functionality of silicon sensors in general can be found in [Lut99].

It is followed by a description of the layout of the current ATLAS pixel sensors and modules. Much more detailed descriptions can be found in various works, for example [Hue01, Kla05, Kra04, Mo99].

## 3.1. Functionality of Planar Silicon Sensors

A planar silicon sensor is basically a semiconductor diode, i.e. a junction of n-doped and p-doped silicon. It is produced on silicon wafers which consist of a slightly n- or pdoped bulk material in the first place. Additionally, one surface is highly doped with an  $n^+$ , the other one with a p<sup>+</sup>-implantation. At the junction between the n- and p-doping a slim depletion zone is naturally formed due to the charge carrier recombination.

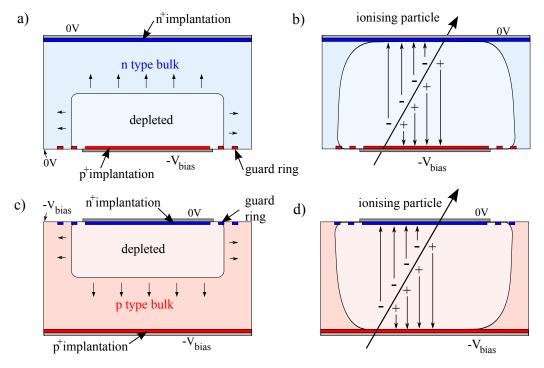

Figure 3.1.: Cross section through a silicon sensor for n-type bulk (a) and b)) and p-type (c) and d)). Adapted from [Kla05].

If a negative bias voltage  $V_{\text{bias}}$  is applied to the p-side whereas the n-side is kept on ground, the depletion zone grows through the bulk towards the other side (see Figure 3.1 a) for n-type bulk and c) for p-type bulk). The voltage at which the bulk is completely depleted is called depletion voltage  $V_{\text{depl}}$ . It is mainly dependent on the bulk thickness d and the bulk resistivity  $\rho$ :

$$V_{\rm depl} = \frac{d^2}{2\,\rho \cdot \mu_e \cdot \varepsilon_{\rm Si} \cdot \varepsilon_0} \tag{3.1}$$

with the electron mobility  $\mu_e = 1427 \frac{\text{cm}^2}{\text{Vs}}$ , the dielectric constant of silicon  $\varepsilon_{\text{Si}} = 11.75$ and the permittivity constant  $\varepsilon_0 = 8.85 \cdot 10^{-6} \frac{\text{pF}}{\mu\text{m}}$  [Lut99, Kla05].

#### 3.1.1. Leakage Current

If a silicon sensor is biased reversely, a leakage current arises which can be caused by several effects. The volume or bulk generation current and the avalanche breakdown are intrinsic even for an ideal sensor. Because it is impossible to produce silicon sensors without any impurities and defects, the interface generation current as well as ohmic currents can also contribute. The latter ones can stem from the bulk due to its non-negligible ohmic conductivity or also from the surface. For further details see [Kla05] and [Wue01].

An important feature of the dominant bulk generation current is the temperature dependency. In order to compare leakage current measurements which have been taken at different temperatures, Equation (3.2) can be used.

$$I_{\rm R} = I \cdot \left(\frac{T_{\rm R}}{T}\right)^2 \cdot \exp\left[-\frac{E_{\rm g}}{2k_{\rm B}}\left(\frac{1}{T_{\rm R}} - \frac{1}{T}\right)\right]$$

(3.2)

I is the current measured at any temperature T (in K),  $I_{\rm R}$  is the current corresponding to a reference temperature  $T_{\rm R}$  (in K) to which it is normalized.  $k_{\rm B} = 8,167 \cdot 10^{-5} \, {\rm eV/K}$ is the Boltzmann constant and  $E_{\rm g} = 1.21 \, {\rm eV}$  the silicon band gap energy [Chi11, ATL03, Lut99]. An increase of the temperature by 7 °C approximately doubles the leakage current. This is the reason why a temperature monitoring is important in order to be able to compensate any fluctuations.

Both the n- and p-type bulk designs exhibit the problem that during the operation there is a potential difference between the p-n-junction and the cutting edge. In order to prevent the sensor from possible electric discharges due to high fields, this region is provided with so called guard rings. These are floating highly doped implantations surrounding the p-n-junction electrode. On the basis of the so called punch-through effect, the bias voltage is decreased gradually from ring to ring. For further details see [Bis93, Hue01].

#### 3.1.2. Particle Detection

Particles traversing matter are interacting in various ways depending on their characteristics. Photons can cause three different effects. The probability of which effect is preferred is highly energy dependent. The photoelectric effect is dominant at lower energies, followed by the Compton effect at energies between  $30 \,\mathrm{keV}$  and  $5 \,\mathrm{MeV}$ . For higher energies the pair production is dominating.

A charged particle can interact with matter in several ways besides ionization. Bremsstrahlung is an electromagnetic radiation caused by the deceleration of the particle. It is inversely proportional to the radiation length which is an inverse measure of the energy loss dependent on the material. For heavier particles the Bethe-Bloch equation describes various kinds of interactions such as the mean elastic and inelastic energy loss as well as Čerenkov radiation. The characteristic of this differential energy loss features a minimum which is at  $3.8 \,\mathrm{MeV/cm}$  for silicon. A particle in the region of this minimum is called a minimum ionizing particle (MIP).

A MIP which crosses the depleted sensor bulk generates a tube of electron-hole pairs uniformly along its track. To generate one electron-hole pair in silicon, 3.6 eV are necessary. In a thin bulk material the energy loss of a particle can be described by a Landau distribution. In comparison to a Gauss distribution which is expected for sufficiently thick materials, it takes into account the possibility that a particle can loose a large fraction of its energy at once. This effects a distortion of the Gauss distribution at higher energies. The mean energy loss is not equal to the most probable energy loss but shifted to higher energies. With thicknesses of 250  $\mu$ m and below, the present silicon sensors fall into this category of thin materials. The most probable energy loss for example in a 250  $\mu$ m thick silicon bulk results to 70 keV. Divided by 3.6 eV, this is equal to 19400 electron-hole pairs [Rum09]. For further details see [Leo94].

Because of the applied voltage, the holes are drifting to the p-side which is on negative bias voltage whereas the electrons are drifting to the n-side which is grounded (see Figure 3.1 b) and d)). The electrons can be measured as a signal with an appropriate read-out chain. In order to obtain a spatial resolution which is required for a high energy collider tracking detector, one implantation can be segmented into strips or pixels which then have to be read-out separately. A planar pixel sensor with a p-type bulk where the n-side is segmented is called n<sup>+</sup>-in-p, i.e. n-pixels on p-bulk. This means the lowly n-doped substrate contains highly n<sup>+</sup>-doped implantation on the front side and highly p<sup>+</sup>-doped implantation on the back side. An n-bulk with n-pixels is analogously called n<sup>+</sup>-in-n.

## 3.2. Radiation Damage in Silicon Semiconductors

#### 3.2.1. General Radiation Effects

The discussed ionizing charge generation is reversible and does not damage the silicon crystal lattice. In contrast a non-ionizing interaction can damage the lattice permanently. Besides the interaction of a particle with a nucleus which can be converted, these damages can manifest in so called point defects like interstitials or vacancies caused by the removal of an atom. If enough energy is transferred to this atom, it can in turn cause further damage which leads to defect clusters. It is called Primary Knock-on Atom (PKA).

Because different particles like hadrons, electrons or pions are causing different effects, the extent of the defect is scaled to a so called standard irradiation. It is important for the comparison of different types of irradiation. The radiation damage caused by this Non-Ionizing Energy Loss (NIEL) is therefore converted to the energy loss which would be caused by neutrons with the energy of 1 MeV. The measurement unit is  $n_{eq}/cm^2$ . The fluence  $\Phi_{irr}$  which is applied at an irradiation facility can be normalized into an equivalent fluence  $\Phi_{eq} = \kappa \cdot \Phi_{irr}$ . The hardness factor  $\kappa$  is unique for each irradiation facility [Mo99, Rum09].

With an increasing irradiation there are several effects which have influence on the effective doping concentration. Besides donor removal due to defects in the crystal lattice, one important effect is that displacement damages act as acceptor-like states. The donor concentration  $N_{\rm D}$  is thus decreasing while the acceptor concentration  $N_{\rm A}$  is increasing. An n-type doped bulk is starting with a positive effective doping concentration  $N_{\rm eff} = N_{\rm D} - N_{\rm A}$ . After a certain irradiation dose it will get negative which means a type conversion of the bulk, it is getting p-type like. In other words the absolute value of the effective doping concentration  $|N_{\rm eff}|$  has a minimum. The fluence where the type conversion sets in, is dependent on the initial doping concentration. For bulk material comparable to that of the ATLAS pixel sensors the minimum of the effective doping concentration is in the region of  $1 - 10 \cdot 10^{13} n_{\rm eq}/\rm cm^2$  [Wun92, Hue01].

The depletion voltage can also be described in dependence on the absolute value of the effective doping concentration (for comparison see Equation (3.1)):

$$V_{\rm depl} = \frac{e_0 |N_{\rm eff}|}{\varepsilon_{\rm Si} \varepsilon_0} \frac{d^2}{2} \quad . \tag{3.3}$$

This relation leads to an increasing depletion voltage with higher irradiation fluences. Especially for higher fluences it is not worthwhile anymore to attempt to fully deplete thick sensor bulks as  $V_{\text{depl}}$  increases disproportional.

In the course of the ROSE Collaboration (RD48) it was investigated how to improve the radiation hardness of silicon sensor material [RD48, ROS96]. It was discovered that the radiation induced lattice defects can be significantly reduced if the standard float zone (FZ) silicon is oxygen enriched during the process. It is called diffusion oxygenated float zone (DOFZ) material. Besides improvements related to the annealing, the effective doping concentration is significantly less increasing with the fluence for DOFZ material. For further details see [Wun92, Web04].

#### 3.2.2. Annealing

The effective doping concentration  $N_{\text{eff}}$  can change in the course of time due to an effect called annealing. It can be classified into three differently acting parts according to the *Hamburg model* [RD48, Mo99, Kra04]:

$$\Delta N_{\text{eff}}(\Phi_{\text{eq}}, t(T_a)) = N_{\text{a}}(\Phi_{\text{eq}}, t(T_a)) + N_{\text{c}}(\Phi_{\text{eq}}) + N_{\text{y}}(\Phi_{\text{eq}}, t(T_a))$$

(3.4)

$N_{\rm a}$  is called the *short term annealing* or *beneficial annealing* part. It increases  $N_{\rm eff}$  which leads to a lower depletion voltage for a type converted n<sup>+</sup>-in-n sensor.  $N_{\rm a}$  decreases with time and is surpassed on a long time scale by the *anti-annealing* or *reverse annealing* part described by  $N_{\rm y}$ . Latter counteracts the beneficial annealing by decreasing  $N_{\rm eff}$  and thus increasing the depletion voltage.  $N_{\rm c}$  is a damage constant in time which only depends on the fluence.

As indicated in Equation (3.4) the annealing speed is dependent on the annealing temperature  $T_a$  because the mobility of defects grows with temperature. For the operation it means that the detector should always be kept as cold as possible. Interim deliberate warm-ups of the pixel detector can be used to benefit from the beneficial annealing. On the contrary, to minimize further sensor deteriorations, the warm-up periods should not last beyond the minimum in the annealing curve. For further details see [Kra04].

The leakage current of an irradiated sensor is proportional to the acquired equivalent fluence  $\Phi_{eq}$  and the depleted volume W:

$$I = \alpha \cdot \Phi_{\rm eq} \cdot W \tag{3.5}$$

The proportionality factor  $\alpha$  is called *current related damage rate*. It can be parameterised in the following way [Mo99]:

$$\alpha(t) = \alpha_I \cdot \exp\left(-\frac{t}{\tau_I}\right) + \alpha_0 - \beta \cdot \ln\left(\frac{t}{t_0}\right)$$

(3.6)

$t_0$  is set to 1 min. The temperature dependent variables are

$$\alpha_0 = -(8.9 \pm 1.3) \cdot 10^{-17} \text{A/cm} + (4.6 \pm 0.4) \cdot 10^{-14} \text{A K/cm} \cdot \frac{1}{T_a} \quad \text{and} \tag{3.7}$$

$$\frac{1}{\tau_1} = k_{0I} \cdot \exp\left(-\frac{E_I}{k_{\rm B}T_a}\right) \tag{3.8}$$

with the parameter values

$$k_{0I} = 1.2^{+5.3}_{-1.0} \cdot 10^{13} \mathrm{s}^{-1} \tag{3.9}$$

$$E_I = (1.11 \pm 0.05) \,\mathrm{eV}$$

. (3.10)

The temperature independent parameters are

$$\alpha_I = (1.23 \pm 0.06) \cdot 10^{-17} \text{A/cm}$$

and (3.11)

$$\beta = (3.07 \pm 0.18) \cdot 10^{-18} \text{A/cm} \quad . \tag{3.12}$$

### 3.3. Design of ATLAS Pixel Sensors

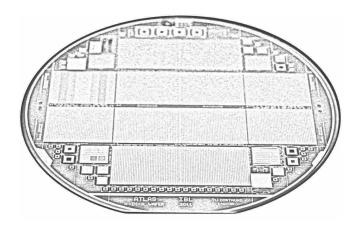

For the ATLAS pixel production the wafers have been produced by the two vendors  $\text{CiS}^1$  and TESLA/ON<sup>2</sup>. The so called sensor tile of the current ATLAS pixel detector is a planar n<sup>+</sup>-in-n silicon sensor. It is processed on n-type doped, 250  $\mu$ m thick DOFZ substrate material. The n<sup>+</sup>-implantation is segmented into a matrix of 400  $\mu$ m long (in z-direction) and 50  $\mu$ m wide (in  $r\phi$ -direction) pixels. Respectively one array of 18 columns and 160 rows are read out by one Front End I3 (FE-I3) chip [Per06].

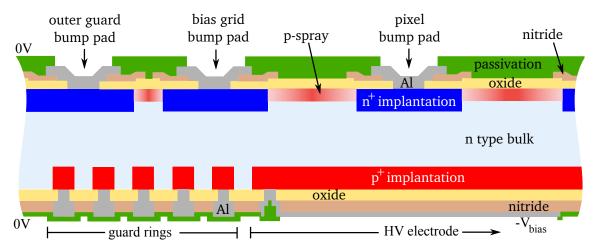

The sketch in Figure 3.2 shows a cross section of the sensor bulk and the differently processed layers on its surface. The n<sup>+</sup>-in-n design requires a double-sided wafer process

<sup>&</sup>lt;sup>1</sup>CiS Forschungsinstitut für Mikrosensorik und Photovoltaik GmbH, Erfurt, Germany, http://www.cismst.org/

<sup>&</sup>lt;sup>2</sup>ON Semiconductor Czech Republic a.s., Roznov, Czech Republic, http://www.onsemi.cz

because both sides have to be structured. Each surface consists of five layers which are from bottom to top:

- 1.  $n^+/p^+$ -implantation

- 2. oxide passivation

- 3. inner nitride passivation

- 4. metal (AlSi alloy)

- 5. outer nitride passivation

Figure 3.2.: Cross section of the ATLAS pixel sensor. Dimensions are not to scale. For detailed description see text. Original taken from [Dob04] and modified.

On the n-side it is possible that the oxide charges can cause a conducting n-channel between the pixel implantations. In order to insulate the  $n^+$ -implantations, a so called p-spray doping is applied to the pixel side between the steps 3 and 4. Its concentration is higher than the low doping of the bulk substrate but significantly lower than the  $n^+$ -implantations. For the present ATLAS pixel sensor design it is used a so called moderated p-spray. The p-doping is spread homogeneously over the complete wafer surface, i.e. there is no need of an additional mask. The strength of the doping is moderated by the nitride layer which is already existent. The full dose is placed in those regions without nitride, a reduced dose in those regions with nitride as indicated in Figure 3.2. The effective doping profile results in a smooth distribution without high field intensities next to the pixel implantations. Within the  $n^+$ -implantations the p-spray doping is completely compensated due to the large differences of the concentrations. For a more detailed description of the process steps see [Hue01, Web04, Roh99].

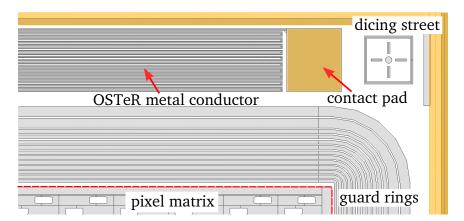

The p<sup>+</sup>-implantation is implemented as one large high voltage pad opposite of the pixel matrix which is surrounded by 16 guard rings. The purpose of the guard rings is a controlled potential drop from the high voltage pad to the grounded cutting edge. A more detailed description of the sensors edge design can be found in Section 5.3.2. Besides the pixelated n<sup>+</sup>-implantation which represents the active area there are two surrounding guard rings which represent the inactive edge: the bias grid ring and the outer guard.

The bias grid is implemented in order to have the possibility to test the sensor before the interconnection with the read-out chip, the bump bonding (see Section 3.4.2). Because

it is not practicable to contact the thousands of pixel cells one has to rely on the punch through effect. Two implantations on the n-side are insulated due to the intermediate p-spray. The intrinsic depletion zones which are generated at the p-n-junctions are separated. If the potential differences between the two implantations is exceeding a so called punch through voltage, the depletion zones connect and generate a conducting path between the implantations. The latter are drawn to the same potential minus the respective punch through voltage. This voltage difference is dependent on the distance between the two implantations. For further details see [Bis93, Hue01].

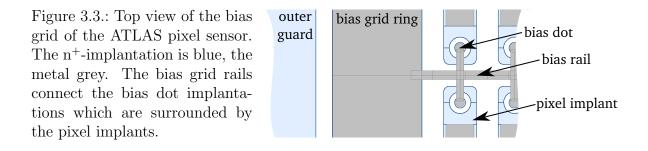

If the ground potential is applied to the sensors edge, the punch through takes place between the implantations from the edge inwards. The effect is not sufficient to guarantee an active area having a homogeneously potential above  $V_{depl}$  because the potential difference between edge and pixel increases with each row [Roh99]. In order to obtain the same potential on each pixel, they are connected via the bias grid (see Figure 3.3). A metal bias rail runs between each double column and is connected to the bias dot. The latter is a circular implantation inside the pixel implantation. The punch through takes place in between these implantations so that each pixel is on the same potential. The bias rails are connected to the bias grid ring. If a sensor is tested, the dicing street

which is connected to the outer guard is on ground potential. In order to guarantee that each pixel is also on ground potential, the punch through effect has to take place only twice: One larger distance of  $15 \,\mu\text{m}$  from the outer guard to the bias grid ring and one small distance of  $5 \,\mu\text{m}$  between the bias dot and the pixel implantation.

During the assembly the sensor is connected to the FE-I3 read-out chip via bump bonds (see Section 3.4.2). The bump bond pads are located at the end of the pixel implants, opposite to the bias dots. Each pixel as well as the n<sup>+</sup>-edge-implantations are hence put on ground potential. Even if some bumps are not connected, those pixels are not floating and thus affecting the sensor performance due to the bias grid which keeps them close to ground potential.

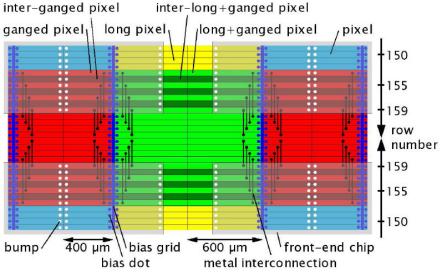

One sensor tile is read out by  $2\times 8$  FE-I3 chips (see also Figure 5.8). The chips need a safety margin between each other in the order of 400  $\mu$ m. Because there is no direct read-out possible in this region and the sensor should not have any inactive part within the active area, the pixel layout is modified in the edge region of the chips as seen in Figure 3.4. The pixels of the edge columns are elongated to 600  $\mu$ m, called long pixels. The four pixel rows which cannot be covered by the chip are connected via metal conductors to every second of the last seven pixels which do have bump connections. These are called ganged pixels. Due to the larger capacitance these pixels feature the disadvantage of an increased noise.

#### 3. ATLAS Pixel Sensors

Figure 3.4.: Top view sketch of the ATLAS sensor-chip assembly in the corner region between four FE-I3. For detailed description see text. [Dob04].

## 3.4. Modules and Read-Out Cards

## 3.4.1. Front End Chip

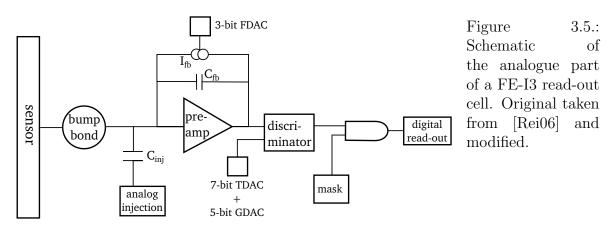

The Front-End chip represents the first part of the processing electronics. Each pixel cell of the sensor is connected to one pixel cell of the front end via bump bonds (see Section 3.4.2). Each Front End pixel cell features an analogue and a digital part. A schematic of the analogue part of a FE-I3 can be seen in Figure 3.5. The charge which

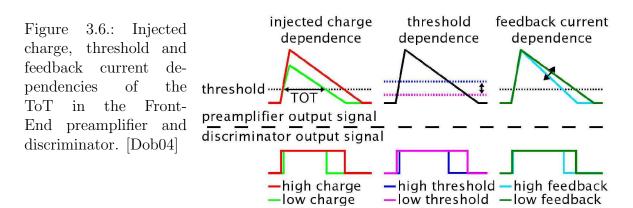

is coming from the sensor is amplified by a preamplifier. The feedback capacity  $C_{\rm fb}$  is charged by the signal and discharged by the feedback current I<sub>fb</sub>. The resulting output of the preamplifier has a rising and a trailing edge of the signal as seen in Figure 3.6. The discriminator digitizes this signal by converting it to a time-over-threshold (ToT) value. The ToT is thus a measure of the amount of charge. The same input signal can cause differing outputs of the discriminators of different Front End pixel cells as their properties are varying. Each chip thus has to be tuned before its operation. It can be done by optimizing the discriminator threshold and the feedback current using several DACs<sup>3</sup>. The injected charge, threshold and feedback current dependencies of the ToT are illustrated in Figure 3.6. It can be seen that the ToT is increased with a higher amount of charge, a lower threshold or a lower feedback current. Further details can be found in [Dob04], for FE-I4 also [Jen11].

<sup>&</sup>lt;sup>3</sup>Digital Analog Converter

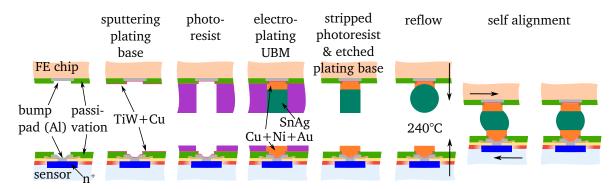

#### 3.4.2. Bump Bonding

The interconnection between the sensor and the read-out chip is done via so called bump bonds. This is an industrially used technique which is needed as each sensor pixel cell has to be read out by one pixel cell of the Front-End chip. For the ATLAS pixel production there have been two bump bond vendors who used different techniques. The IZM<sup>4</sup> uses tin-silver bumps (formerly lead-tin) while AMS<sup>5</sup> uses indium bumps. For all sensor productions which are investigated during this thesis, the only bump vendor is IZM. It is thus confined to the tin-silver bump process. A sketch is seen in Figure 3.7. Before the actual bump bond process, the pads of the sensor and the

Figure 3.7.: Tin-silver bump bonding process which is performed at IZM. For further description see text. Taken from [Dob04] and modified.

chip have to be prepared with additional metal layers, the so called under bump metal (UBM). They are applied onto the passivation openings to achieve a good mechanical and electrical contact for the bumps. The UBM pads which consist of three layers of copper, nickel and gold are electro-plated. They are in total approximately 7  $\mu$ m high. As the electro-plating is a wafer-level process, it has to be executed before the dicing step. The bump bond is applied on the pads of the chip. It is a 20  $\mu$ m high cylinder which consists of an eutectic alloy of 96.5% tin and 3.5% silver. After a reflow step at 240 °C, the bump takes the form of a sphere. The interconnection step between sensor and chip is called the flip chip process. Due to the surface tension of the melted bumps, a self alignment occurs which balances a possible misalignment. A detailed description of the bump bonding process can be found in [Web04].

<sup>&</sup>lt;sup>4</sup>Fraunhofer Institut für Zuverlässigkeit und Mikrointegration, Berlin, Germany, http://www.izm.fraunhofer.de/

<sup>&</sup>lt;sup>5</sup>Alenia Marconi Systems, Rome, Italy, now SELEX, http://www.selex-es.com/

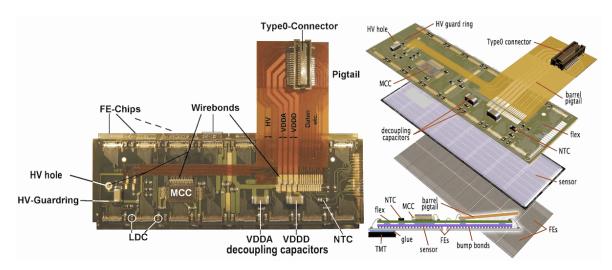

#### 3.4.3. Modules

The ATLAS pixel module is the smallest unit of the present ATLAS pixel detector (see Figure 3.8 and also Figure 5.8). The assembly of sensor tile and 16 FE-I3 chips is called

Figure 3.8.: Sketch of the ATLAS pixel module. For detailed description see text. [Tro12]

bare module. It is glued to a flex which contains passive SMD components, a  $10 \text{ k}\Omega$  ceramic NTC thermistor and an active module control chip (MCC). The high and the low voltage supplies as well as the signal processing is routed via an attached so called pigtail to a type 0 connector. The FE-I3 chips are wire bonded to the flex. The high voltage is wire bonded from the flex via a HV-hole directly to the sensors p-side. A detailed description of the ATLAS pixel modules can be found in [Dob04, Boy03].

#### 3.4.4. Read-Out Cards

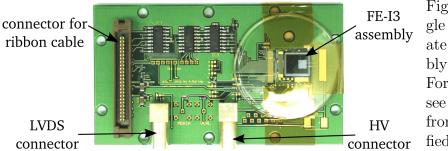

In order to test the performance and efficiency of sensor chip assemblies in lab or at test beam setups (see Section 5.5), they have to be wire bonded to special read-out cards. Figure 3.9 shows a FE-I3 single chip card (SCC). It was originally designed at the university of Bonn. Besides being responsible for LVDS and HV supply, this

Figure 3.9.: FE-I3 single chip card to operate a sensor chip assembly in lab or test beam. For detailed description see text. Original taken from [Tro12] and modified.

circuit board is read out by a ribbon cable which is connected to the USB-Pix system [USBPix]. The latter is operated by the STControl software [STCon]. This system is able to perform tunings and scans of the assembly. This is necessary in order to guarantee that all pixels are tuned for example to the same threshold and the assembly

is thus configured homogeneously. Further details of the USB-Pix system and the STControl software can be found in [Jen11] and [Lap12].

## 3.5. Stave Assembly

In the barrel section of the ATLAS pixel detector, 13 modules are mounted on one stave. The stave is made of a carbon-fibre composite material and serves as a mechanical support for the modules, cables and the cooling pipe. (see also Figure 2.3) [Aad08b]. In Figure 3.10, a bi-stave can be seen, i.e. two staves which share one cooling loop. The staves are mounted cylindrically around the beam pipe and form the barrel layers.

Figure 3.10.: Bi-stave of the ATLAS pixel detector before mounting. The arrow marks the point where two modules are shingled on top of each other's edges. The roofing of the two staves can be seen as well. At the left end of the staves, the connectors for the cooling pipes are visible. [Tro12]

In order to compensate the dead space of 1.1 mm due to the sensors inactive edge area, the module edges overlap each other (called 'shingling') at their short side on the stave, see arrow in Figure 3.10. This arrangement implicates a significantly increase of required space in  $r\phi$ -direction for each layer. The compensation of the dead space at the long side of the modules is done by an overlap of the staves, called 'roofing'. With this kind of arrangement the detector gets hermetic enclosed in the barrel region.

# 4. Plans for ATLAS Upgrades

## 4.1. LHC Schedule

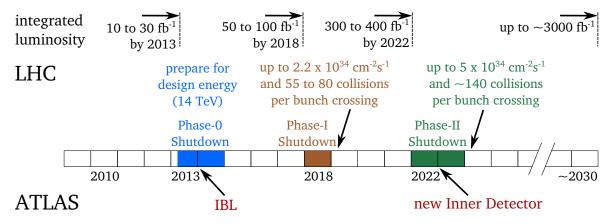

In the current LHC shutdown, the collider will be prepared to run at its design energy of 7 + 7 TeV (see Figure 4.1). The instantaneous luminosity which has reached up to now values up to  $7.7 \cdot 10^{33} \text{ cm}^{-2} \text{s}^{-1}$  [ATLPub] will be increased to the designated value of  $1 \cdot 10^{34} \text{ cm}^{-2} \text{s}^{-1}$ . Until a shutdown in 2018, the integrated luminosity will have

Figure 4.1.: Time schedule for the upgrades of LHC and ATLAS. Informations taken from [ATL12].

reached up to  $100 \text{ fb}^{-1}$ . After this Phase-I upgrade of the LHC, the peak instantaneous luminosity will increase to  $2.2 \cdot 10^{34} \text{ cm}^{-2} \text{s}^{-1}$  and deliver around 300 to 400 fb<sup>-1</sup> by 2022. At this time, the potential increase in statistics will not justify the effort of running such a huge and expensive machine. However, further improvements in the generation and collimation of high-intensity beams indicate that a luminosity of up to  $5 \cdot 10^{35} \text{ cm}^{-2} \text{s}^{-1}$  might be achievable with some upgrades to the accelerator. In this Phase-II, the so called High Luminosity LHC (HL-LHC) will begin collisions around 2024. It is planned to operate the machine until a total integrated luminosity of up to  $3000 \text{ fb}^{-1}$  is reached [ATL12].

The costs for this improvement are a significantly increased number of pile-up events per bunch-crossing. This will lead to larger occupancies and radiation damage especially for the inner tracking detectors. The current LHC detectors will thus as well have to be upgraded to cope with these challenges.

## 4.2. ATLAS Pixel Upgrades

The upgrades of the ATLAS pixel detector are planned for the Phase-0 and the Phase-II shutdowns.

### 4.2.1. IBL

The design luminosity of the present ATLAS pixel detector is  $10^{34}$ cm<sup>-2</sup>s<sup>-1</sup>. As a first step to ensure a satisfactory operation of ATLAS also with higher luminosities, the current Phase-0 shutdown is used to install an additional pixel b-layer, the so-called insertable b-layer (IBL). The principle motivation is to provide an increased tracking performance like improving the track pattern recognition capability, the reconstructed track accuracy and the primary and displaced vertex identification performance (btagging) in high-luminosity conditions [IBL12]. This is particularly necessary as the tracking performance of the present pixel detector will decrease due to the emerging radiation damages.

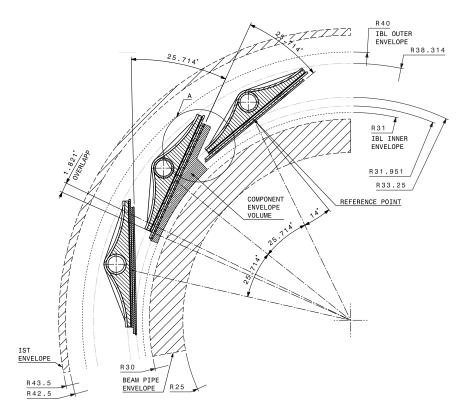

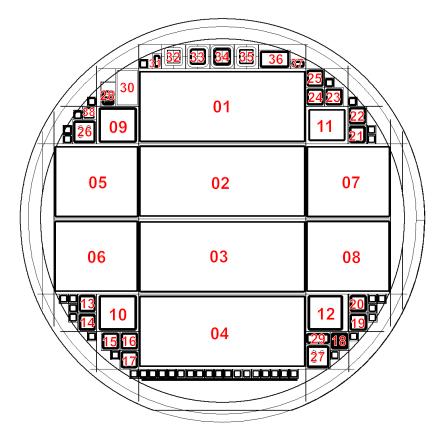

Figure 4.2 shows a cross section of one quarter of the IBL, looking into beam direction. This new layer contains 14 staves and will be mounted on a new, smaller beam pipe at an average radius of 33 mm. With an outer envelope of 40 mm it fits within the existing b-layer.

Figure 4.2.: Cross section of the  $r\phi$ -plane of one quarter of the IBL. [IBL10]

Due to the close proximity to the interaction point, a radiation tolerance up to a fluence of  $5 \cdot 10^{15} n_{eq}/cm^2$  is required for sensors and read-out chips. This fact, as well as an expected high occupancy per pixel cell, leads to the necessity of a new read-out chip, the FE-I4 (see [IBL12]). Its pixel cells are shortened to  $50 \,\mu\text{m} \times 250 \,\mu\text{m}$  so that the z-resolution is significantly improved. The pixels are arranged in a matrix of 336 rows times 80 columns, leading to dimensions of  $20.2 \,\text{mm} \times 18.8 \,\text{mm}$ ; about five times larger than those of the present FE-I3.

The requirements for the sensors are furthermore the ability to operate at -15 °C after irradiation with a maximum bias voltage of 1 kV. The maximum power dissipation

at this temperature must not exceed  $200 \,\mathrm{mW/cm^2}$  due to the limited cooling power capabilities. Because of the extreme spatial constraints of the IBL, its modules cannot be shingled anymore on the staves. They have to be arranged in a flat way so that the small module edges abut. The geometric inefficiency of the sensor caused by its inactive edge has to stay below 2.2% (see Section 4.3.1).

The current planning for the IBL foresees two scenarios. One option is to equip the central 75% of the staves with planar n<sup>+</sup>-in-n sensors and in the high- $\eta$  region 25% with 3D silicon sensors [Via09]. The second option foresees a 100% planar sensor solution. In both cases the planar modules are Double Chip Modules (DCM), i.e. one planar n<sup>+</sup>-in-n sensor (Double Chip Sensor, DCS) is read-out by two FE-I4 chips. At the time of the submission of this thesis, the decision of which scenario will be carried out is not yet made. Further details of the IBL can be found in [IBL10].

#### 4.2.2. New Inner Detector

To cope with the increased occupancy at HL-LHC, a complete replacement of the inner tracker will be necessary. Currently, only two detector technologies are foreseen: The strip detector outside the radius of  $\sim 30$  cm and the pixel detector inside of the  $\sim 30$  cm radius from the beam. The TRT is omitted completely. Outside the  $\sim 30$  cm radius the costs for pixel sensors would become unaffordable whilst inside, both occupancy and radiation damage become too large for strip sensors. For further details see [ATL12].

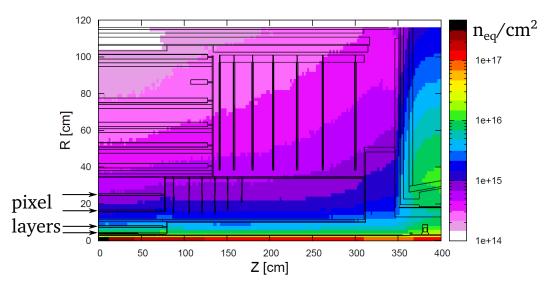

Figure 4.3.: Simulation of an rz-map of the neutron equivalent fluence, expected for the ATLAS Inner Tracker region, normalised to  $3000 \text{ fb}^{-1}$  of 14 TeV minimum bias events. Taken from [ATL12] and modified.

As ATLAS is using planar pixel sensors now and will continue to gain considerable experience during its operation, it is a natural choice to explore whether their radiation hardness is sufficient for HL-LHC usage. Simulations as seen in Figure 4.3 predict a NIEL dose of about  $2 \cdot 10^{16} n_{eq}/cm^2$  for the innermost layer and around  $10^{15} n_{eq}/cm^2$  for the outermost pixel layer. Investigations of the radiation hardness of n<sup>+</sup>-in-n sensors at HL-LHC fluences can be found in [Rum13] and [Alt14]. Improvements of the design and technologies which are relevant and of use for the ATLAS pixel Phase-II upgrades are presented in Chapter 7.

## 4.3. Sensor Improvements

## 4.3.1. Slim Edges

The spatial constraints for the IBL necessitate a flat edge-to-edge mounting of the modules on the stave. If the edge design of the current ATLAS pixel sensor is inherited for the IBL DCS, this would cause a geometric inefficiency in the order of 5%. This is incompatible with the 2.2% which is mandatory. This fact necessitates a drastic reduction of the sensors inactive edge region. An inefficiency of 2.2% relating to the IBL DCS would require a decrease of the inactive edge down to 450  $\mu$ m per side.

Besides the spatial constraints in the IBL, the shingling of the modules on the staves implicates generally several disadvantages. The mounting is complicated as the alignment on the inclined stave is more challenging as on a flat one. More material is needed in the detector which implicates an undesired larger radiation length of the tracker. Furthermore, the cooling performance of the modules is limited due to the irregular basis.

For the outermost layers of a future detector, the option of a double-sided stave is feasible which enables a module overlap. In contrast the inner layers will likely rely on flat staves requiring again slim edges to achieve sufficient geometric efficiency. It is conceivable that the specifications to the inactive sensor fraction are even more demanding than for the IBL. It is planned to use the IBL read-out chip FE-I4 for the outer layers and the end cap discs of the HL-LHC upgrade. A successor model which is based on the FE-I4 will be used for the inner layers [ATL12]. Hence all results obtained with IBL-type sensors are also relevant and of note for the Phase-II ATLAS pixel upgrade.

Because the inactive area of the present ATLAS pixel sensor is necessary to decrease the high voltage to the cutting edge it has to be investigated in how far a reduction is compatible with a reliable sensor operation. These slim edge studies represent one main topic of this thesis.

After reaching the pixel side, the depletion zone propagates laterally into the edge region with increasing bias voltage. If it reaches the cutting edge, many charge carriers can be induced by surface impurities and cause a massive increase of the leakage current. Thus, a dependency of the breakdown voltage from the safety margin distance is expected. Furthermore, it has to be investigated in how far the situation changes after irradiation of the sensor. Due to the irradiation induced bulk type conversion, the planar n-type sensor behaves like a p-type sensor. Results are presented in Chapter 5.

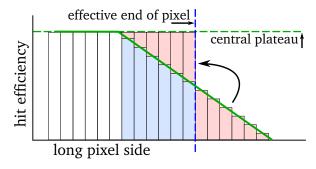

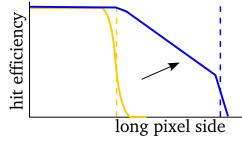

An innovative method to decrease the inactive sensor edge without risking to reduce the sensor yield is a shifting of the active area opposite to the guard rings. This subject is illustrated in Section 5.3.2. Because this design approach was not used before, it has to investigate in how far the efficiency of these pixels behaves. Analyses of data taken in test beam setups are discussed in Section 5.5.

### 4.3.2. IBL Sensor Production

The usage of a new read-out chip for the IBL necessitates the fabrication of new compatible  $n^+$ -in-n sensors. Therefore, the existing planar pixel sensor design has to

be adapted to the FE-I4 geometry as well as to the IBL module specifications. The slim edge results have to be incorporated in order to guarantee a sufficient geometric efficiency.

A prototype production preceding to the main IBL production is required in order to do pretests with the new designed sensors, evaluate their functionality and, if applicable, change the design moderately. The design and the quality control of both productions until the flip chip step represent another topic of this thesis. The respective results of the prototype production are presented in Sections 5.3 and 5.4, those of the main IBL production in Sections 6.1 and 6.3.

# 5. Prototype Sensor Studies

## 5.1. Slim Edge Dicing Trials on Sensors

A first step in order to investigate in how far the sensors inactive edge can be reduced is done with FE-I3 single chip sensors (SCS) of the ATLAS production. Results of initial dicing tests can be found in [Wit09]. Section 5.1.1 represents a summary of these measurements.

All results of this Section 5.1 have been published in [Mue10].

#### 5.1.1. Dicing Trials

#### Procedure

In order to characterize the functionality of a silicon sensor, an IV measurement is the most meaningful test. An increasing negative high voltage is applied to the high voltage electrode on the p-side whilst the leakage current is measured on the grounded n-side. As long as the depletion zone expands in the bulk, the leakage current increases square root like, mainly caused by the volume generation current. After  $V_{depl}$  is reached, the current should saturate in a flat plateau for an ideal sensor. Because the bulk has a not completely negligible conductivity, the ohmic part of the current causes a more or less flat slope. A breakdown indicates an avalanche like increase of the leakage current. In order to guarantee a stable operation, the sensor should not be biased in the range of a breakdown.

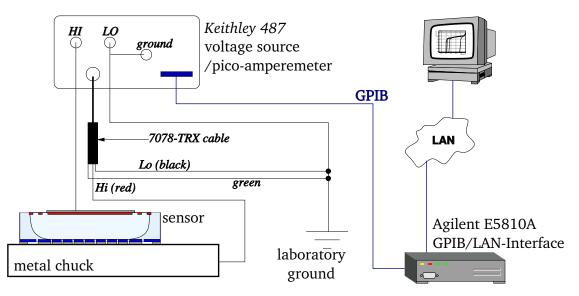

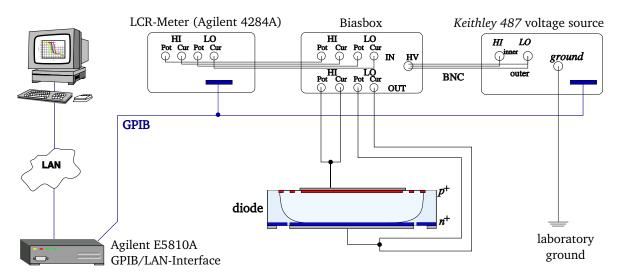

A schematic of a setup for IV measurements can be seen in Figure 5.1. In this case the diced sensor is lying on a grounded metal chuck, n-side down. The high voltage pad is contacted via a probe needle. The measurement is done by a *Keithley 487* device which serves as a pico-amperemeter as well as the high voltage source. An additional temperature logging is done via a *Keithley 196* multimeter (not in the sketch) which measures the resistivity of a PT100 temperature probe. Both devices are read out via GPIB and controlled by a *Lab-View* software.

A total number of 76 diced FE-I3 SC sensors of the ATLAS production are IV measured initially up to 500 V to guarantee that all of them withstand voltages of more than 350 V. Concerning the ATLAS quality assurance criteria (see [ATL03]) the sensor should have a leakage current below 100 nA at the operation voltage of 150 V. These sensors with a much higher breakdown voltage have been selected in order to be able to see deteriorations in the IV characteristic afterwards.

The sensors are then cut with a conventional diamond wafer dicing saw outside the active area. They are divided into seven groups where each group is assigned to one

#### 5. Prototype Sensor Studies

Figure 5.1.: Schematic of the setup for IV measurements. The high voltage is applied via a probe needle. In this sketch the sensor is already diced and the ground contact is given by a metal chuck. If the sensor is still not separated, the wafer is fixed at its edge and the ground is applied via a second probe needle to the dicing street. Original taken from [Rum09] and modified.

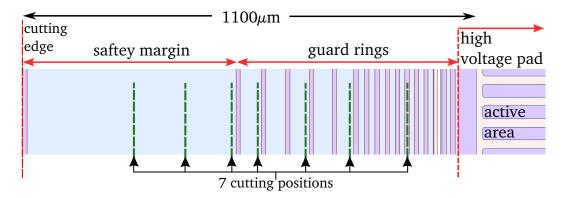

cutting position. An overview can be seen in Table 5.1. Figure 5.2 shows a sketch of the sensors inactive edge between the dicing street and the active area. The guard rings can be seen in red. The seven cutting positions are marked in green.

Table 5.1.: Overview of the seven cutting positions and distances from the high voltage pad.

|   | cutting position                        | distance from high voltage pad |

|---|-----------------------------------------|--------------------------------|

| 1 | half of safety margin cut away          | $810\mu{ m m}$                 |

| 2 | three quarter of safety margin cut away | $670\mu{ m m}$                 |

| 3 | 16 guard rings remaining                | $590\mu{ m m}$                 |

| 4 | 15 guard rings remaining                | $530\mu{ m m}$                 |

| 5 | 13 guard rings remaining                | $420\mu{ m m}$                 |

| 6 | 11 guard rings remaining                | $315\mu{ m m}$                 |

| 7 | cut into inner guard rings              | $170\mu{ m m}$                 |

Because of the imprecise alignment of the wafer saw, an error tolerance for the distance in the order of  $30 \,\mu\text{m}$  has to take into account. The seventh position is, depending on the accuracy of the alignment, equal to six or seven remaining guard rings.

After cutting one or two sides (for some sensors even three or four sides) at the described positions, the sensors are characterised again after each step. It is observed that if a significant reduction of the breakdown voltage occurred, this happened already after the first cut. Subsequent cutting steps do not lead to significant further reduction.

Figure 5.2.: Sketch of the different cutting positions that were chosen: The three outer ones only reduced the safety margin while the four inner ones removed some of the guard rings.  $n^+$ -implantation on the pixel side in blue,  $p^+$ -implantation on the back side in red.

#### Results

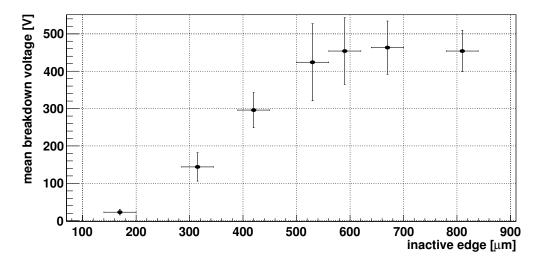

A summary of the described dicing trials can be seen in Figure 5.3. The mean breakdown voltage is plotted against the remaining inactive edge after cutting (see Table 5.1). The vertical error bars indicate the standard deviation, the horizontal ones the uncertainty due to the dicing position. In this case the breakdown voltage is defined as the last voltage value which was measured before reaching the current compliance of 1000 nA. If the compliance is not exceeded, the maximum voltage of 500 V is taken.

Figure 5.3.: Mean breakdown voltage of the unirradiated sensors, plotted against the remaining inactive edge after the slim edge cutting. The error bars indicate the standard deviations. As long as the guard rings are not affected (three rightmost positions), the breakdown voltage stays constant. By cutting off the guard rings the breakdown voltage decreases with the reduced safety margin.

In the plot two linear trends can be identified. As long as the cut is done in the safety margin outside the guard rings (positions 1, 2 and 3) the breakdown voltage appears to stay constant within the error bars. This effect can be attributed to the maximum bias voltage of the voltage supply so that higher breakdown voltages than 500 V cannot

be determined. If they were taken into account, it is supposable that the breakdown voltages would rise further with increasing safety margin.

The second linear trend is visible in the decrease of the breakdown voltage if the number of guard rings is reduced (positions 4 to 7). Nevertheless, only the most aggressively cut sensors definitely fail to fulfil the ATLAS quality assurance criteria. In particular, the position 5 with 13 remaining guard rings and approximately 420  $\mu$ m of inactive edge width appears acceptable with sufficient safety margin for full depletion of a 250  $\mu$ m thick sensor before irradiation. Eleven guard rings on average seem enough to grant full depletion. However, individual samples breakdown at around 100 V which is less than demanded by ATLAS quality assurance criteria. A further reduction to 7 guard rings or less prevents the operational capability of unirradiated sensors.

One explanation for this behaviour could be the fact that the cutting was done using a tool which might have inflicted crystal damage at the cutting edge. This damage can extend some tens of  $\mu$ m into the sensor area and disabling the function of more guard rings than have been cut. Besides, the fact that no dicing streets are used results in a blurred edge containing partially n<sup>+</sup>-implants and/or metal which can modify the electric field at the edge.

### 5.1.2. Results after Irradiation

#### Procedure

In order to investigate in how far the IV characteristic changes after irradiation induced bulk conversion, 56 of the sensors are neutron irradiated at the TRIGA reactor of the Jožef Stefan institute in Ljubljana [Lju]. They are distributed again into four groups of different fluences:

- $0, 5 \cdot 10^{15} \, n_{eq}/cm^2$

- $2 \cdot 10^{15} \, n_{eq} / cm^2$

- $7 \cdot 10^{15} \, n_{eq} / cm^2$

- $15 \cdot 10^{15} \, n_{eq}/cm^2$

The fluences cover different stages of irradiation during the operation of ATLAS. The lowest fluence corresponds to the situation shortly after type conversion whereas the highest one represents the magnitude of HL-LHC conditions. After irradiation, they were stored in a freezer to avoid uncontrolled annealing until the activation had sufficiently worn off after approximately 2 months. For reference purpose several sensors diced at the conventional cutting edge were included in the irradiation procedure.

The IV measurements of the irradiated sensors works in principle as described previously for unirradiated ones. A challenge is the leakage current which is highly increased for irradiated sensors in comparison to unirradiated ones (compare Section 3.2, Equation (3.5)). To compensate this and avoid a sensor self-heating, it has to be cooled during the measurement as it is done in later detector operation. Therefore, the sensor is lying on a brass plate which is cooled down to  $\sim -15$  °C by a Peltier cooler. A PID (proportional-integral-derivative) control is used to stabilise the temperature at a constant level. For planar sensors the depletion voltage is strongly correlated with the irradiation fluence (see Equation (3.3)). To guarantee a sufficient charge collection, the bias voltage has to be increased respectively. In this case the sensors are measured up to voltages of 1500 V applied by a *Keithley 248* HV source. The bias voltage is fed to the single chip sensors via a spring. The pixel side is contacted via the cutting edges of the sensors using the brass plate.

#### Results

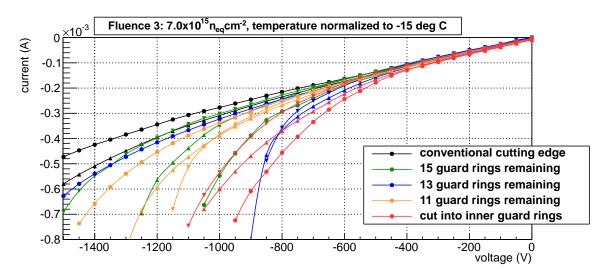

Figure 5.4 shows one example of the IV measurements of the irradiated sensors with the fluence of  $7 \cdot 10^{15} \,\mathrm{n_{eq}/cm^2}$ . The leakage currents are normalized to the intended temperature of  $-15 \,^{\circ}\mathrm{C}$  by using Equation (3.2).

Figure 5.4.: Example of the IV measurements of the irradiated sensors with the fluence of  $7 \cdot 10^{15} \,\mathrm{n_{eq}/cm^2}$ . The leakage currents are normalized to  $-15 \,^{\circ}\mathrm{C}$ . The different cutting positions are encoded by different colours.

It can be seen that after irradiation, no sudden breakdowns occur any more. This indicates that the guard rings are mainly necessary before irradiation. After the irradiation induced bulk conversion it appears that their functionality is considerably changed. However some kind of escalations of the currents beyond a bias voltage of about 700 V are obvious. One explanation is a significant sensor self-heating due to an insufficient cooling. The measured temperatures on the brass plate showed an increase of more than 4°C with increasing voltages. Although the leakage currents are normalized to -15°C it cannot be excluded that the actual sensor temperature was even higher than the temperature of the brass plate.

A trend that the escalation effect is more pronounced in samples with slimmer edges is visible. This could indicate that the number of guard rings is still important for the control of leakage currents after irradiation. On the other hand it is also conceivable that it is just an effect of a declined heat transfer from the sensor to the chuck due to the reduced contact surface at the sensors edges.

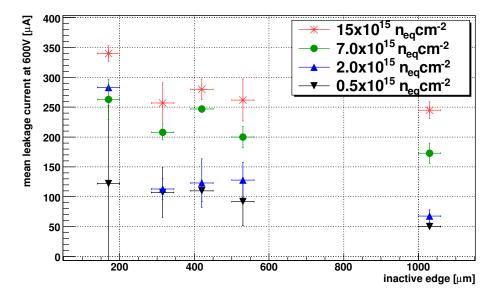

Because of the shape of the IV curves of the irradiated sensors it does not make any sense to identify a kind of breakdown voltage as it is done for the results of the unirradiated sensors. To achieve a consistent picture, the mean leakage current at one defined voltage and the related standard deviation were derived for samples cut at different edge positions and irradiated to the different fluences. The values are plotted in Figure 5.5 against the remaining inactive edge after cutting. A voltage of 600 V is chosen as in that range the escalation is still not existent. The vertical error bars indicate the standard deviation, the horizontal ones the uncertainty due to the dicing position.

Figure 5.5.: Results of the slim edge cut sensors after irradiation. The mean leakage current at 600 V is plotted against the remaining inactive edge. The vertical error bars indicate the standard deviation, the horizontal ones the uncertainty due to the dicing position. The different fluences are encoded by different colours. It can be seen that the leakage currents are by trend increasing with the fluence and slightly for reduced edge widths. For the most aggressive cut a significant rise is seen especially for the two lower fluences.

As it can be seen the leakage currents of the irradiated sensors are increasing with the fluence as expected. Furthermore, they increase slightly for reduced edge widths. Only for the most aggressive cut, a significant rise is seen especially for the two lower fluences. This effect was already discussed before. The current changes down to  $300 \,\mu\text{m}$  edge width are almost negligible if the uncertainty of the actual sensor temperature is taken into account. Nevertheless even the current increase of the most aggressively cut sensors is tolerable.

#### 5.1.3. Discussion

The presented results show that a significant reduction of the distance between cutting edge and high voltage pad of ATLAS pixel sensors is feasible. Before irradiation the sensors with 13 remaining guard rings and  $\sim 420 \,\mu\text{m}$  inactive edge clearly fulfil the ATLAS quality criteria. This is an important result as the IBL design specification of  $450 \,\mu\text{m}$  inactive edge can already be fulfilled. Even a reduction to 11 guard rings seems realistic taking into account the option of adapting the quality criteria to future

sensor layouts. For example a reduced bulk thickness can implicate the possibility to decrease the operation voltage. This subject is further discussed in Section 5.4.

After irradiation the situation is getting less critical. The reduction of the safety margin including the guard rings has no considerable influence on the leakage current. The influence of the temperature on the leakage current is in contrast much more important.

# 5.2. Leakage Current Dependencies of Irradiated Sensors

It was shown that for irradiated sensors the reduced inactive edge distance only influences the leakage current insignificantly. It is expected that the sensor temperature as well as an annealing step will cause a larger impact on the leakage current and thus to the sensor power dissipation.

### 5.2.1. Temperature Dependencies

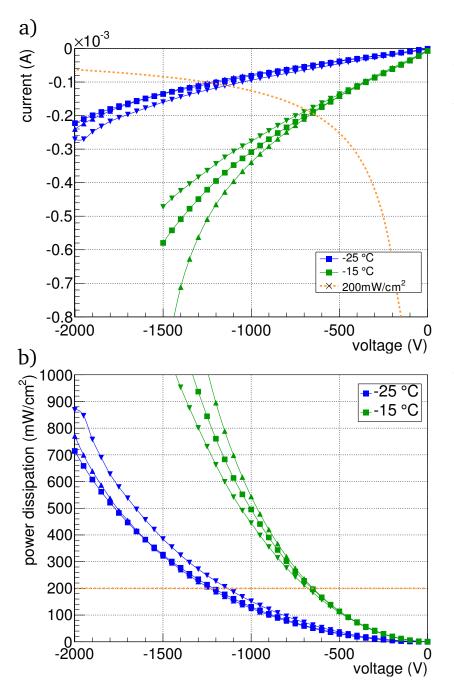

Three FE-I3 single chip sensors are regarded which are neutron irradiated to a fluence of  $7 \cdot 10^{15} \,\mathrm{n_{eq}/cm^2}$ . In order not to overlay different effects, those have been selected which have been diced at the conventional cutting edge. Figure 5.6 a) shows the result of the IV measurements at  $-15\,^{\circ}\mathrm{C}$  in green and at  $-25\,^{\circ}\mathrm{C}$  in blue.

The leakage current decrease with the lower temperature is obvious. For example at 1000 V and also below it is decreased by a factor of  $\sim 3.9$ . This is even a bit more than the theoretical value of 3.4 which is expected for these temperatures (compare Equation (3.2)). One explanation is that the sensor self-heating effect is much more dominant at higher temperatures. If the sensor is cooled to lower temperatures, this effect is supposably suppressed from the outset and an escalation is much more unlikely. It again has to be taken into account that the temperature is not measured on the sensor so that a possible light and lingering temperature increase could not be noticed.

In Figure 5.6 b) the values are translated to the electrical power  $P = V \cdot I$  nominated per square centimetre. It can be seen that the approximative linear voltage dependency of the current translates into a quadratic dependency of the power. The yellow dashed line in both plots marks 200 mW/cm<sup>2</sup>. As already mentioned, this value is the normalized power dissipation benchmark for the IBL sensors. For the IBL condition at -15 °C and a maximum bias voltage of 1000 V the power consumption exceeds this limit as seen in the plot. One has to keep in mind that the fluence is actually a bit higher than the IBL benchmark of  $5 \cdot 10^{15} n_{eq}/cm^2$ . It can be assumed that for the IBL end-of-life scenario the power dissipation would be slightly lower.

For possible HL-LHC scenarios higher voltages than 1000 V may be necessary for planar n<sup>+</sup>-in-n sensors to guarantee a sufficient collected charge. In this case a cooling down to -15 °C will not be sufficient at all as the thermal runaway gets uncontrollable as seen in Figure 5.6. However by cooling down to -25 °C the power dissipation reaches the 200 mW/cm<sup>2</sup> limit at ~ 1200 V. To be operable up to 2000 V, the temperature would have to be reduced further, e.g. in this case down to -35 °C. Furthermore, the investigated fluence of  $7 \cdot 10^{15} \,\mathrm{n_{eq}/cm^2}$  is of course not representative for an expected

Figure 5.6.: a): IV measurements of three neutron irradiated sensors with a fluence of  $7\cdot 10^{15}\,n_{\rm eq}/cm^2.$ The measurements are performed at  $-15^{\circ}C$ (green) and at -25 °C (blue). The current reduction at -25 °C is obvious. In b) the currents are translated to the electrical power nominated per square centimetre. It can be seen that the approximative linear voltage dependency of the current translates into a quadratic dependency of the The yellow power. dashed line in both plots marks the benchmark  $\operatorname{IBL}$ of  $200 \, {\rm mW/cm^2}$ .

HL-LHC scenario. Higher power consumptions due to higher irradiation damages will have to be compensated with even lower operation temperatures or controlled annealing steps.

## 5.2.2. Annealing Studies

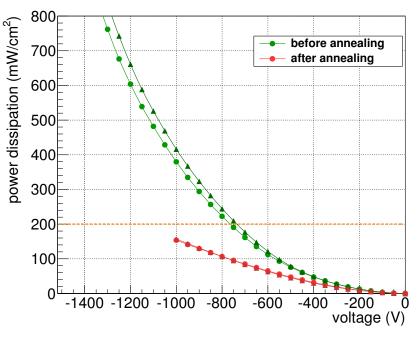

As pointed out in Section 3.2.2 there will be designated machine shutdowns where the ATLAS pixel detector will be warm-up for a longer time period. These monitored annealing phases are beneficial for the operation as the sensors leakage current and thus their power dissipation can be reduced.

An investigation is done with two sensors irradiated to  $4 \cdot 10^{15} \, n_{eq}/cm^2$ . It is tried to simulate a warm-up period of 100 days at 20 °C which could be a realistic scenario. To

accelerate the annealing process significantly, the sensors can be heated in an oven. Therefore, it is calculated for which  $t-T_a$ -pairs the current related damage rate  $\alpha$  (see Equation (3.6)) takes the same value as for 100 days at 20 °C which is

$$\alpha_{100\,\mathrm{d},20\,\mathrm{^{\circ}C}} = 3.145 \cdot 10^{-17} \,\mathrm{A/cm} \quad . \tag{5.1}$$

The result is ~ 5.75 hours at 60 °C. The measured power dissipation at -15 °C before (in green) and after (in red) annealing is seen in Figure 5.7.

Figure 5.7.: Power dissipation at -15 °C of two sensors irradiated to  $4 \cdot 10^{15} \, n_{eq}/cm^2$  plotted against the operation voltage. It can be seen the results before (green) and after (red) the annealing step of ~ 5.75 hours at 60°C. A clear reduction can be observed afterwards. Even at 1000 V the power dissipation stays significantly below the IBL benchmark of  $200 \,\mathrm{mW/cm^2}$ .

The reduction of the power dissipation after the annealing step is obvious. Whereas the  $200 \text{ mW/cm}^2$  limit is reached at 750 V before annealing it afterwards stays well below up to 1000 V. At 1000 V the power consumption is reduced by a factor of ~ 2.6. It has to be taken into account that the fluence applied to the sensors are slightly reduced compared to the IBL benchmark. The leakage current is linear dependent with the fluence if the same depleted volume is by approximation assumed to be constant (see Equation (3.5)). With this assumption an extrapolation of the expected power dissipation for  $5 \cdot 10^{15} \text{ n}_{eq}/\text{cm}^2$  can be made by multiply the factor 1.25. Even for the maximum bias voltage of 1000 V it hence should not exceed the 200 mW/cm<sup>2</sup> limit. This extrapolation is actually conservative as the depleted volume is rather decreased for higher fluences and the resulting leakage current should be rather lower.

The previous results show that planar n<sup>+</sup>-in-n sensors are capable to deal with one of the basic IBL criteria. The power consumption benchmark of  $200 \text{ mW/cm}^2$  can be maintained up to the maximum operation voltage of 1000 V at  $-15 \,^{\circ}\text{C}$  taking into account a designated annealing phase. Thus, an operation under IBL conditions is in principle feasible. This result does not yet give information about the performance of irradiated sensors. Detailed radiation hardness studies including for example the hit efficiency and collected charge can be found in [Rum13] and [Alt14].

## 5.3. Design of the Prototype Sensors

Parts of this section have been published in [Wit12].

#### 5.3.1. Modifications to the Present ATLAS Pixel Sensor

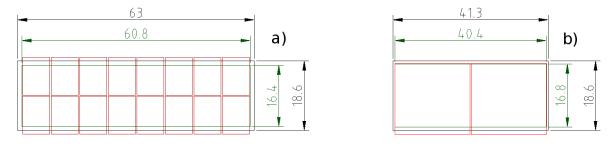

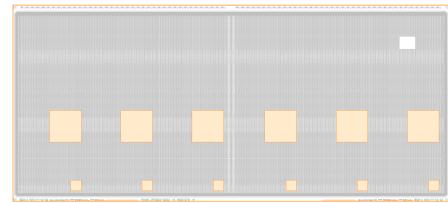

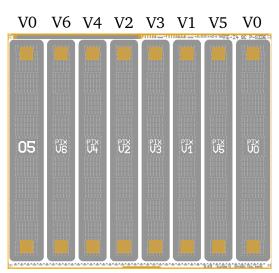

Based on the sensor design developed for the ATLAS pixel detector, modifications were made for the upgrade sensors. In order to be compatible to the newly developed FE-I4 read-out chip, the sensor geometry had to be adapted. The pixel size has been shrunk to  $250 \,\mu\text{m} \times 50 \,\mu\text{m}$  which results in better z-resolution of the detector along the beam pipe and in a lower hit occupancy per pixel. The pixel matrix is enlarged to 80 columns  $\times$  336 rows so that the area of an FE-I4 covers nearly six times the area of an FE-I3. The IBL will consist of n<sup>+</sup>-in-n 2×1 Double Chip Sensors (DCS), i.e. one sensor is read out by two FE-I4 chips as seen in Figure 5.8b).

Figure 5.8.: Comparison of the dimensions of the present ATLAS pixel module (a)) and the planar IBL module (b)). The sensor cutting edges are in black, the sensor active area in green and the Front-End read-out chips in red. Dimensions in mm.

To accommodate the edge region of the read-out chip and a necessary gap between them, the sensor pixels of the inner edge columns (the last of the left and the first of the right chip) are extended to  $450 \,\mu\text{m}$ . In comparison to the ATLAS pixel module there are no gaps between the Front End chips in the vertical direction which have to be covered with ganged pixels (compare Figure 3.4). For this reason the IBL DCS have no ganged pixels.

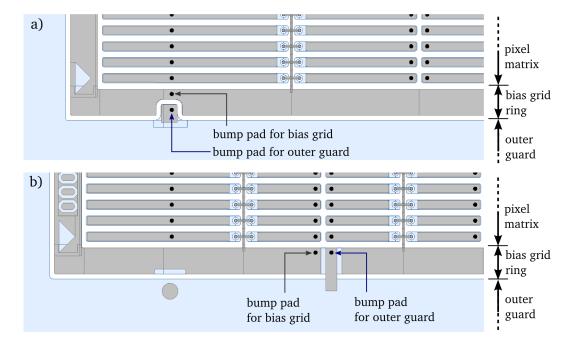

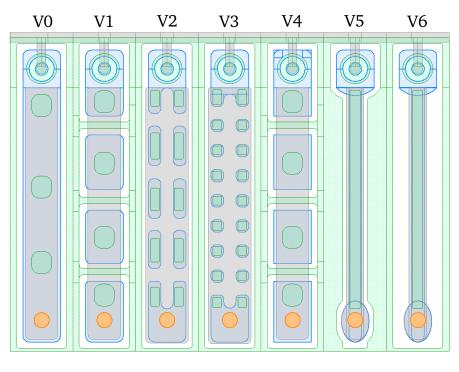

The additional bump pads which ground the bias grid ring and the surrounding outer guard can be seen in Figure 5.9. In the ATLAS pixel design these bump pads are placed within the first and last column, in the IBL design they are placed within the second and last but one (bias grid ring) and within the third and last but two (outer guard) column. These bumps are routed to ground via the read-out chip. Within the FE-I4A, the two bumps are shorted together while for the FE-I4B, they are accessible separately.

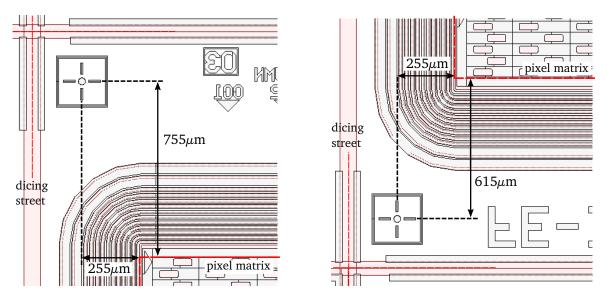

#### 5.3.2. Sensor Edge Design

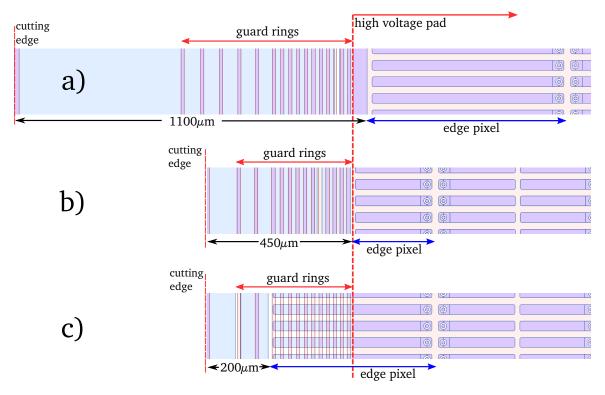

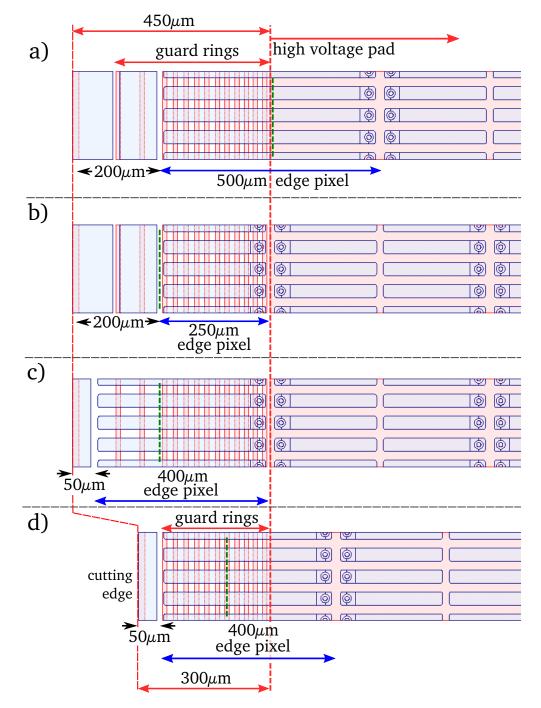

A comparison of the IBL and the ATLAS pixel sensor edge design can be seen in Figure 5.10. In the ATLAS pixel sensor design (Figure 5.10 a)) the 16 guard rings

Figure 5.9.: Top view of the n-side corner of the active area of the ATLAS pixel (a)) and the IBL design (b)). The  $n^+$ -implantation is blue, the metal grey. The additional bump pads (black circles) which ground the bias grid ring and the outer guard are marked.

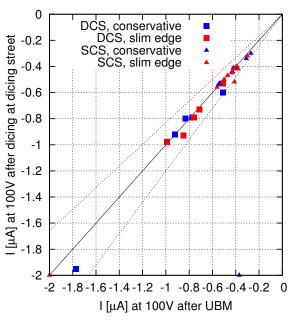

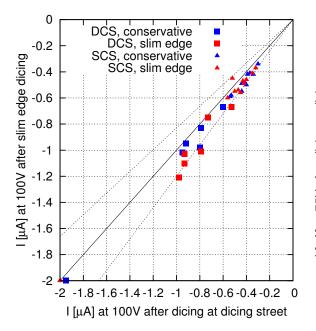

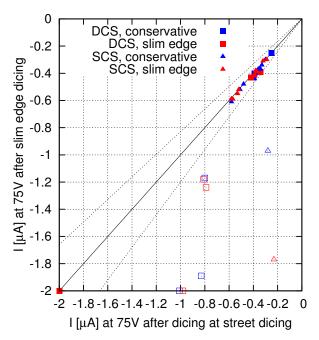

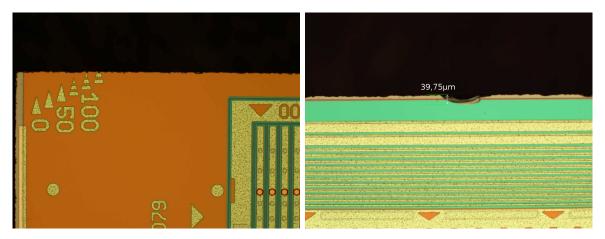

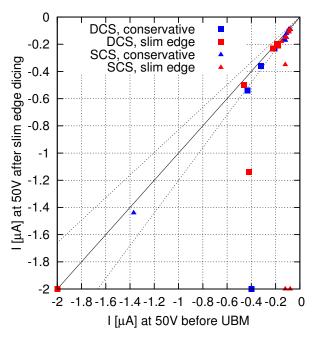

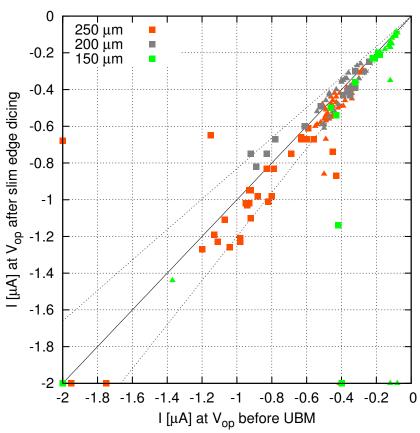

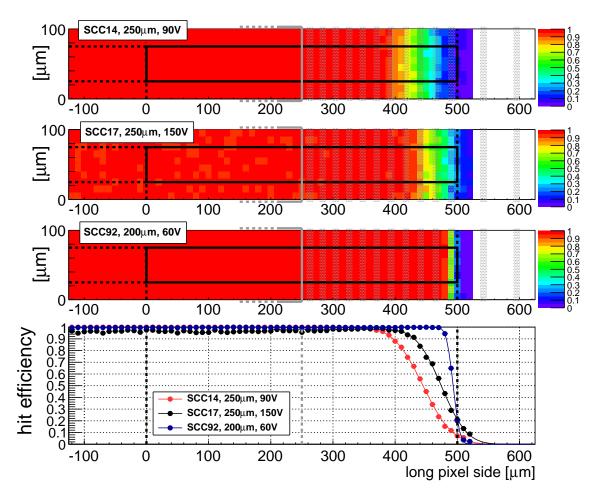

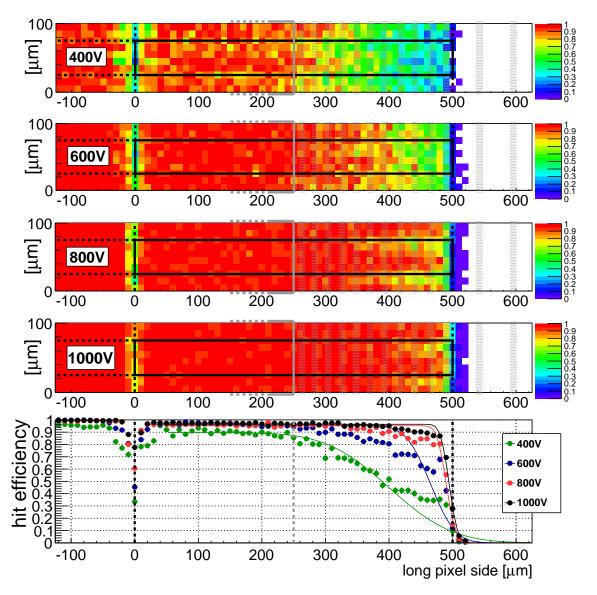

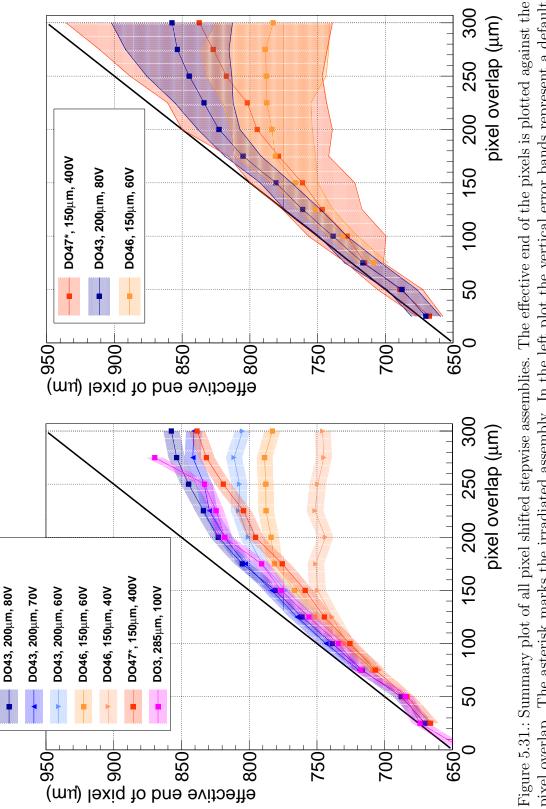

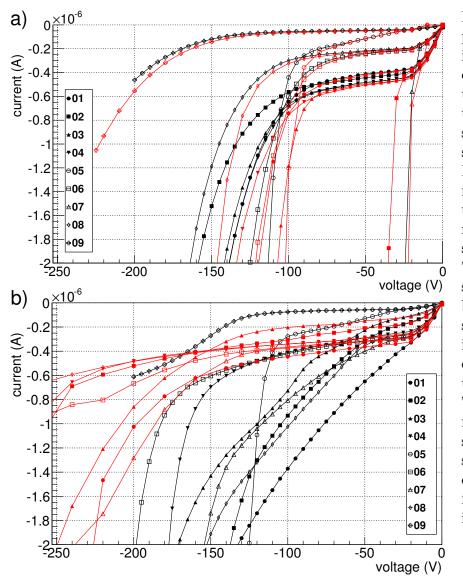

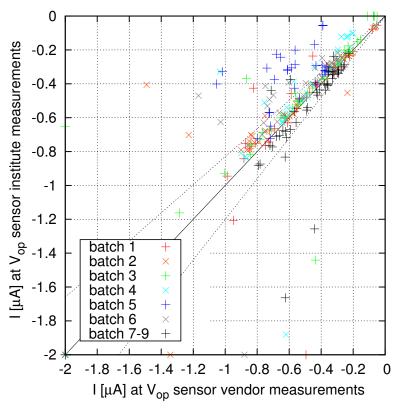

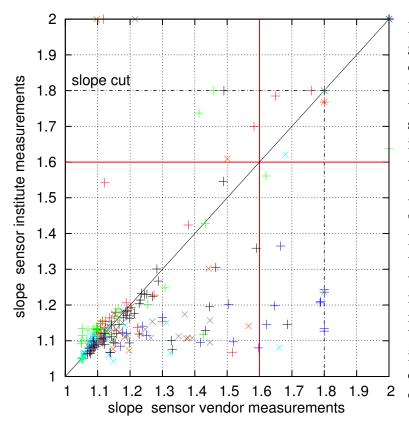

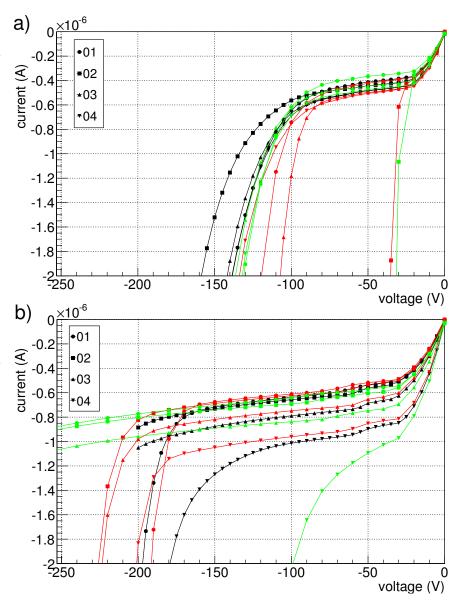

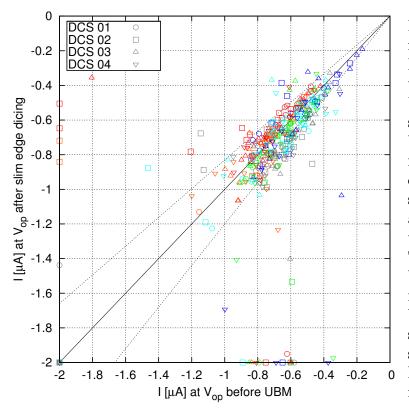

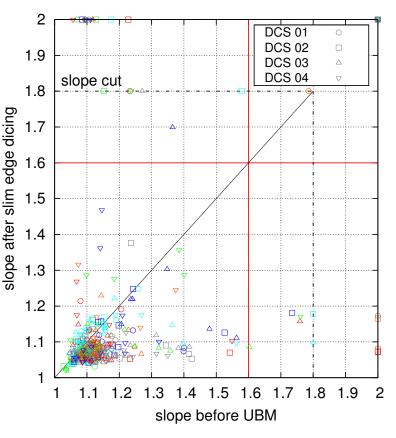

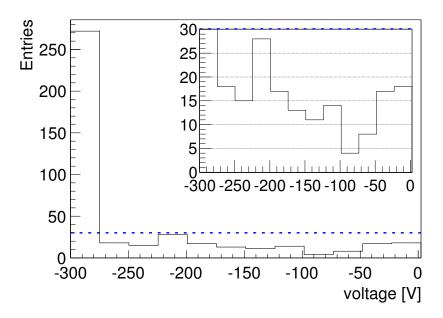

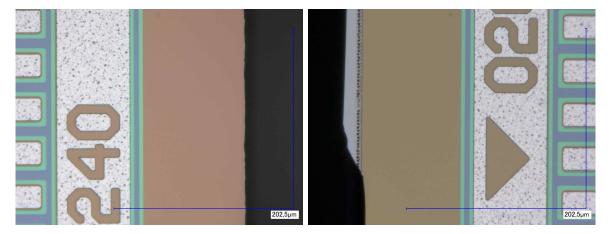

covering a width of about  $600 \,\mu\text{m}$  and the  $500 \,\mu\text{m}$  safety margin are adding up to an overall inactive edge of  $1100 \,\mu\text{m}$  between the edge pixels and the cutting edge.