## Automatic Parallelization for Embedded Multi-Core Systems using High-Level Cost Models

### Dissertation

zur Erlangung des Grades eines

Doktors der Ingenieurwissenschaften

der Technischen Universität Dortmund an der Fakultät für Informatik von

Daniel Alexander Cordes

Dortmund 2013

Tag der mündlichen Prüfung: 11. November 2013

**Dekan / Dekanin:** Prof. Dr. Gernot A. Fink Gutachter / Gutachterinnen: Prof. Dr. Peter Marwedel Prof. Dr. Albert Cohen

# Acknowledgments

First of all, I would like to thank my advisor Prof. Dr. Peter Marwedel for his commitment and the possibility to accomplish the research leading to this PhD thesis. Without his initial ideas and his advices, this thesis would not have been feasible in this form. I would also like to thank him for the interesting work which I could contribute to the MNEMEE European research project. This project and the following funding allowed me to participate in many interesting project meetings and conferences all over the world. I would also like to thank Prof. Dr. Albert Cohen for his commitment to participate as an external reviewer for this PhD thesis. Special thanks go to Dr. Michael Engel for his advices over the years, the various technical discussions, and his intensive proof-reading support for the originated publications and this thesis.

The collaborating work with all my colleges at our Department of Computer Science XII also had a big influence on the quality of this work. I would also like to thank Florian Schmoll, my office colleague, who always found time for various extensive technical and non-technical discussions. Additional acknowledgments go to Andreas Heinig who provided the required operating system as well as the middleware necessary to evaluate the approaches of this thesis. Besides, I would like to thank Olaf Neugebauer, Timon Kelter, Helena Kotthaus, Björn Bönninghoff, and Jan C. Kleinsorge for their technical feedback and proof-reading support. It was an enjoyable time for me while working in this excellent research team.

Above all, I would like to mention that it would not be possible for me to write this thesis without the love and support of my family. I owe special thanks to my girlfriend Regina Fritsch, my parents Ernst Walter and Claudia Catharina Cordes as well as my brother Steven Cordes. All of them play an important role in my life and are always there for me. Therefore, I dedicate this work to them.

Additional thanks go to the European Community since parts of the research leading to this thesis have received funding from the European Community's MNE-MEE Project which was part of the Seventh Framework Programme FP7 under grant agreement no 216224. Later parts of the work have been supported by Deutsche Forschungsgemeinschaft (DFG) within the Collaborative Research Center SFB 876 "Providing Information by Resource-Constrained Analysis", project A3.

# Abstract

Nowadays, embedded and cyber-physical systems are utilized in nearly all operational areas in order to support and enrich peoples' everyday life. To cope with the demands imposed by modern embedded systems, the employment of Multiprocessor System-on-Chip (MPSoC) devices is often the most profitable solution. However, many embedded applications are still written in a sequential way. In order to benefit from the multiple cores available on those devices, the application code has to be divided into concurrently executed tasks. Since performing this partitioning manually is an error-prone and also time-consuming job, many automatic parallelization approaches were developed in the past. Most of these existing approaches were developed in the context of high-performance and desktop computers so that their applicability to embedded devices is limited. Many new challenges arise if applications should be ported to embedded MPSoCs in an efficient way. Therefore, novel parallelization techniques were developed in the context of this thesis that are tailored towards special requirements demanded by embedded multi-core devices.

All approaches presented in this thesis are based on sophisticated parallelization techniques employing high-level cost models to estimate the benefit of parallel execution. This enables the creation of well-balanced tasks, which is essential if applications should be parallelized efficiently. In addition, several other requirements of embedded devices are covered, like the consideration of multiple objectives simultaneously. As a result, beneficial trade-offs between several objectives, like, e.g., energy consumption and execution time can be found enabling the extraction of solutions which are highly optimized for a specific application scenario.

To be applicable to many embedded application domains, approaches extracting different kinds of parallelism were also developed. The structure of the global parallelization approach facilitates the combination of different approaches in a plugand-play fashion. Thus, the advantages of multiple parallelization techniques can easily be combined. Finally, in addition to parallelization approaches for homogeneous MPSoCs, optimized ones for heterogeneous devices were also developed in this thesis since the trend towards heterogeneous multi-core architectures is inexorable.

To the best of the author's knowledge, most of these objectives and especially their combination were not covered by existing parallelization frameworks, so far. By combining all of them, a parallelization framework that is well optimized for embedded multi-core devices was developed in the context of this thesis.

# **Publications**

Parts of this thesis have been published in proceedings of the following conferences and workshops (in chronological order):

- 1. Daniel Cordes, Loop Analysis for a WCET-optimizing Compiler Based on Abstract Interpretation and Polylib (in German), Master's thesis, Technische Universität Dortmund, 2008.

- 2. Niklas Holsti, Jan Gustafsson, Guillem Bernat, Clément Ballabriga, Armelle Bonenfant, Roman Bourgade, Hugues Cassé, Daniel Cordes, Albrecht Kadlec, Raimund Kirner, Jens Knoop, Paul Lokuciejewski and Merriam, WCET Tool Challenge 2008: Report, in Proceedings of the International Workshop on Worst-Case Execution Time Analysis (WCET), Prague, Czech Republic, 2008.

- 3. Paul Lokuciejewski, Daniel Cordes, Heiko Falk, and Peter Marwedel, A Fast and Precise Static Loop Analysis Based on Abstract Interpretation, Program Slicing and Polytope Models, in Proceedings of the International Symposium on Code Generation and Optimization (CGO), Seattle, Washington, USA, 2009.

- 4. Daniel Cordes and Peter Marwedel, An automatic parallelization tool for embedded systems, based on hierarchical task graphs, Research Poster at the Designing for Embedded Parallel Computing Platforms: Architectures, Design Tools, and Applications (DEPCP'2010) (DATE Workshop), Dresden, Germany, 2010.

- 5. Christos Baloukas, Lazaros Papadopoulos, Dimitrios Soudris, Sander Stuijk, Olivera Jovanovic, Florian Schmoll, Daniel Cordes, Robert Pyka, Arindam Mallik, Stylianos Mamagkakis, François Capman, Séverin Collet, Nikolaos Mitas, and Dimitrios Kritharidis, Mapping Embedded Applications on MPSoCs: The MNEMEE Approach, in Proceedings of the International Symposium on VLSI (ISVLSI), Washington, DC, USA, 2010.

- Daniel Cordes, Peter Marwedel, and Arindam Mallik, Automatic parallelization of embedded software using hierarchical task graphs and integer linear programming, in Proceedings of the International Conference on Hardware/Software Codesign and System Synthesis (CODES+ISSS), Scottsdale, Arizona, USA, 2010.

- 7. Daniel Cordes, Andreas Heinig, Peter Marwedel, and Arindam Mallik, Automatic Extraction of Pipeline Parallelism for Embedded Software Using Linear Programming, in Proceedings of the International Conference on Parallel and Distributed Systems (ICPADS), Tainan, Taiwan, 2011.

- 8. Daniel Cordes and Peter Marwedel, *Multi-objective aware extraction of task-level parallelism using genetic algorithms*, in Proceedings of the Design, Automation and Test in Europe Conference Exhibition (DATE), Dresden, Germany, 2012.

- Daniel Cordes and Peter Marwedel. PAXES Parallelism Extraction for Embedded Systems: Three Approaches – One Tool Research Poster at the Designing for Embedded Parallel Computing Platforms: Architectures, Design Tools, and Applications (DEPCP'2010) (DATE Workshop), Dresden, Germany, 2012.

- 10. Daniel Cordes, Michael Engel, Peter Marwedel, and Olaf Neugebauer, Automatic extraction of multi-objective aware pipeline parallelism using genetic algorithms, in Proceedings of the International Conference on Hardware/Software Codesign and System Synthesis (CODES+ISSS), Tampere, Finland, 2012.

- 11. Daniel Cordes, Michael Engel, Olaf Neugebauer, and Peter Marwedel, Automatic Extraction of Multi-Objective Aware Parallelism for Heterogeneous MPSoCs, in Proceedings of the International Workshop on Multi-/Many-core Computing Systems (MuCoCoS), Edinburgh, Scotland, UK, 2013.

- 12. Daniel Cordes, Michael Engel, Olaf Neugebauer, and Peter Marwedel, Automatic Extraction of Pipeline Parallelism for Embedded Heterogeneous Multi-Core Platforms, in Proceedings of the International Conference on Compilers, Architectures, and Synthesis for Embedded Systems (CASES), Montreal, Canada, 2013.

- 13. Daniel Cordes, Michael Engel, Olaf Neugebauer, and Peter Marwedel, Automatic Extraction of Task-Level Parallelism for Heterogeneous MPSoCs, in Proceedings of the International Workshop on Parallel Software Tools and Tool Infrastructures (PSTI), Lyon, France, 2013.

# Contents

| 1        | Intr | roduction                                      | 1        |

|----------|------|------------------------------------------------|----------|

|          | 1.1  | Motivation                                     | 3        |

|          | 1.2  | Automatic Parallelization for Embedded Systems | 5        |

|          | 1.3  | Contribution of this Work                      | 7        |

|          | 1.4  | Author's Contribution to this Dissertation     | 6        |

|          | 1.5  | Outline                                        | 11       |

| <b>2</b> | Rel  | ated Work                                      | 3        |

|          | 2.1  | Task-Level Parallelism                         | 14       |

|          | 2.2  | Data-Level Parallelism                         | 16       |

|          | 2.3  |                                                | 16       |

|          | 2.4  | •                                              | 22       |

|          | 2.5  | ·                                              | 24       |

|          | 2.6  | _                                              | 25       |

|          | 2.7  |                                                | 26       |

| 3        | Fra  | mework 2                                       | 26       |

| U        | 3.1  |                                                | 30       |

|          | 0.1  |                                                | 30       |

|          |      |                                                | 32       |

|          | 3.2  |                                                | 33       |

|          | 0.2  |                                                | 34       |

|          |      | •                                              | 35       |

|          |      |                                                | 36       |

|          |      |                                                | 37       |

|          | 3.3  |                                                | 37       |

|          | 5.5  |                                                | 37       |

|          |      |                                                | 38       |

|          |      | •                                              |          |

|          | 3.4  |                                                | 39<br>40 |

|          |      | ·                                              |          |

| 4        |      | S.                                             | 11       |

|          | 4.1  | 1 ( )                                          | 13       |

|          |      | *                                              | 13       |

|          | 4.0  |                                                | 16       |

|          | 4.2  |                                                | 52       |

|          |      | • • • • • • • • • • • • • • • • • • • •        | 52       |

|          |      |                                                | 57       |

|          | 4.9  | Cummany.                                       | 30       |

Contents

| 5 | Sing | gle-Ob  | jective Parallelization for Homogeneous MPSoCs          |                        | 61  |

|---|------|---------|---------------------------------------------------------|------------------------|-----|

|   | 5.1  | Intege  | er Linear Programming                                   |                        | 63  |

|   | 5.2  | ILP-b   | ased Task-Level Parallelization Approach                |                        | 63  |

|   |      | 5.2.1   | Motivating Example for Task-Level Parallelism           |                        | 64  |

|   |      | 5.2.2   | Integration into the Global Parallelization Approach $$ |                        | 67  |

|   |      | 5.2.3   | Parallelization Model                                   |                        | 68  |

|   |      | 5.2.4   | ILP-based Parallelization Approach                      |                        | 70  |

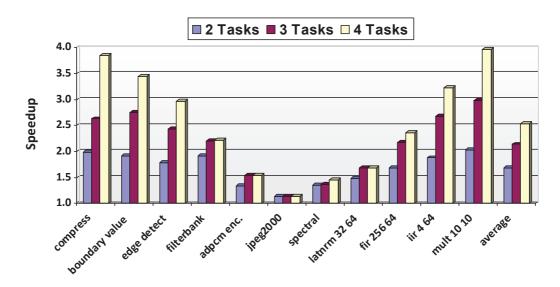

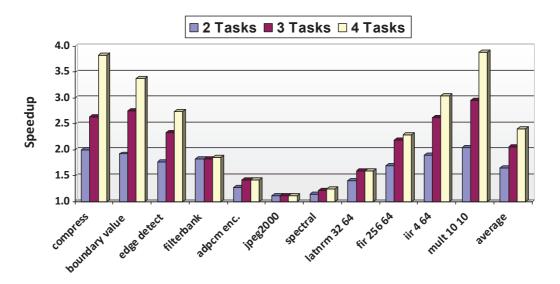

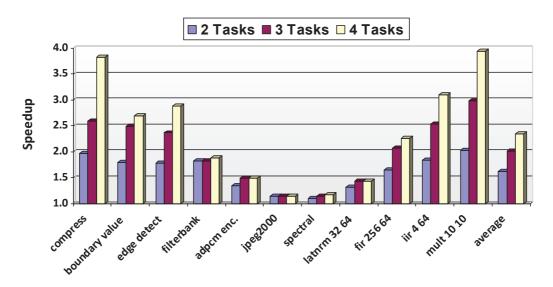

|   |      | 5.2.5   | Experimental Results                                    |                        | 78  |

|   | 5.3  | ILP-b   | ased Pipeline Parallelization Approach                  |                        | 84  |

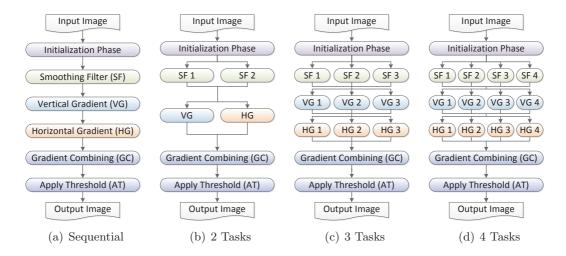

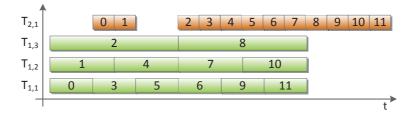

|   |      | 5.3.1   | Motivating Example for Pipeline Parallelism             |                        | 84  |

|   |      | 5.3.2   | Augmented Program Dependence Graph                      |                        | 87  |

|   |      | 5.3.3   | Integration into the Global Parallelization Approach    |                        | 89  |

|   |      | 5.3.4   | Parallelization Model                                   |                        | 90  |

|   |      | 5.3.5   | ILP-based Parallelization Approach                      |                        | 92  |

|   |      | 5.3.6   | Experimental Results                                    |                        | 99  |

|   | 5.4  | Summ    | nary                                                    |                        | 103 |

| 6 | Mu   | lti-Obj | jective aware Parallelization for Homogeneous MPSo      | $\mathbf{C}\mathbf{s}$ | 105 |

|   | 6.1  | Genet   | ic Algorithms                                           |                        | 108 |

|   | 6.2  | GA-ba   | ased Task-Level Parallelization Approach                |                        | 109 |

|   |      | 6.2.1   | Integration into the Global Parallelization Approach    |                        | 110 |

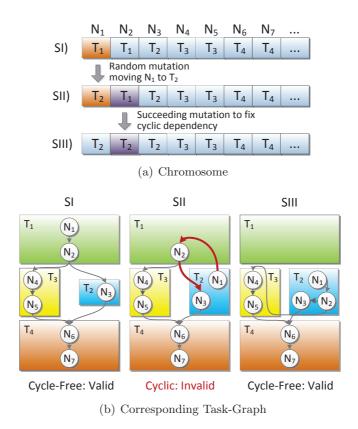

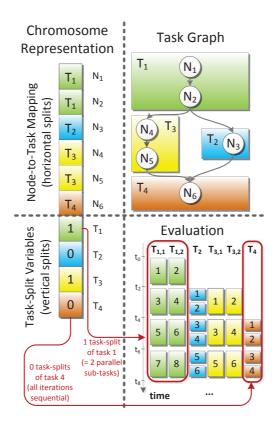

|   |      | 6.2.2   | Chromosome Structure                                    |                        | 111 |

|   |      | 6.2.3   | Objective Evaluation                                    |                        | 113 |

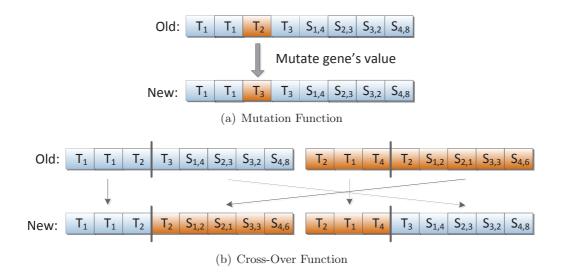

|   |      | 6.2.4   | Mutation & Cross-Over                                   |                        | 116 |

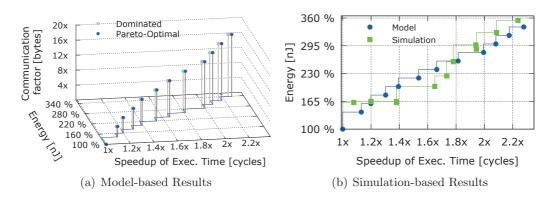

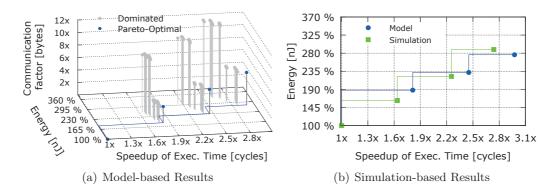

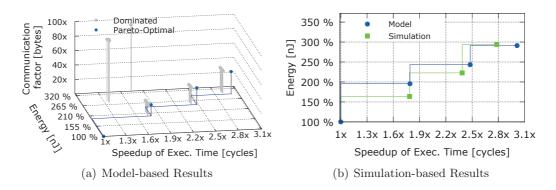

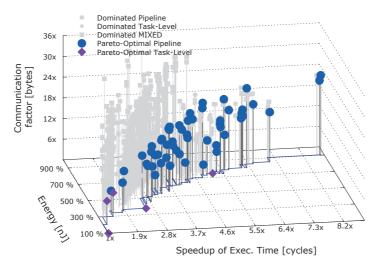

|   |      | 6.2.5   | Experimental Results                                    |                        | 118 |

|   | 6.3  | GA-ba   | ased Pipeline Parallelization Approach                  |                        | 122 |

|   |      | 6.3.1   | Integration into the Global Parallelization Approach    |                        | 123 |

|   |      | 6.3.2   | Chromosome Structure                                    |                        | 124 |

|   |      | 6.3.3   | Objective Evaluation                                    |                        | 126 |

|   |      | 6.3.4   | Mutation & Cross-Over                                   |                        | 129 |

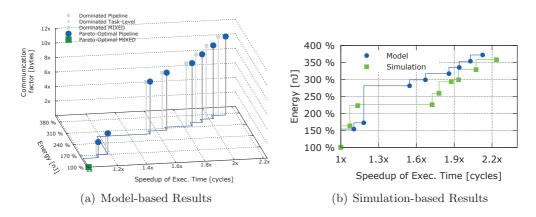

|   |      | 6.3.5   | Experimental Results                                    |                        | 129 |

|   | 6.4  | Summ    | nary                                                    |                        | 134 |

| 7 | Sing | ole-Oh  | jective Parallelization for Heterogeneous MPSoCs        |                        | 137 |

|   | 7.1  | _       | ased Task-Level Parallelization Approach                |                        | 139 |

|   |      | 7.1.1   | Motivating Example                                      |                        | 140 |

|   |      | 7.1.2   | Integration into the Global Parallelization Approach    |                        | 142 |

|   |      | 7.1.3   | ILP-based Parallelization Approach                      |                        | 143 |

|   |      | 7.1.4   | Simple Loop Parallelization Approach                    |                        | 150 |

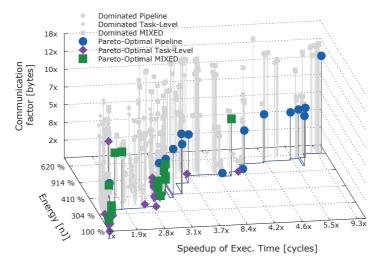

|   |      | 7.1.5   | Experimental Results                                    |                        | 152 |

|   | 7.2  |         | ased Pipeline Parallelization Approach                  |                        | 158 |

|   |      | 7.2.1   | Motivating Example                                      |                        | 158 |

|   |      | 7.2.2   | Integration into the Global Parallelization Approach    |                        |     |

|   |      | 7.2.3   | ILP-based Parallelization Approach                      |                        |     |

| Contents | xi |

|----------|----|

|          |    |

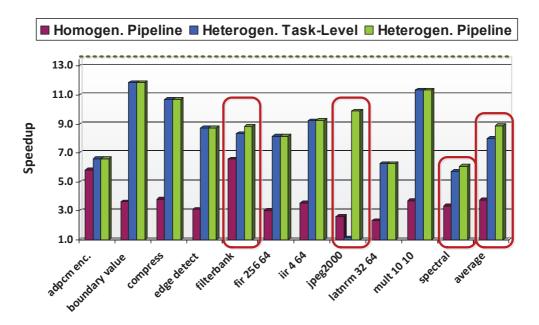

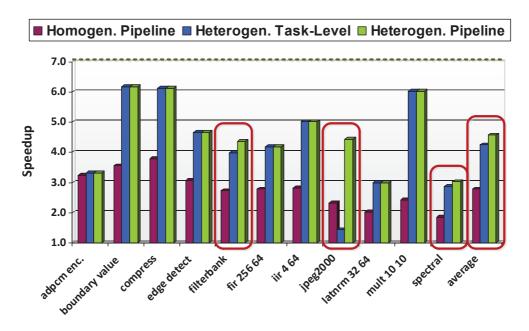

|               |                        | 7.2.4 Experimental Results                                         | 169          |

|---------------|------------------------|--------------------------------------------------------------------|--------------|

|               | 7.3                    | Summary                                                            | 175          |

| 8             | Mu                     | ti-Objective aware Parallelization for Heterogeneous MPSoCs        | s <b>177</b> |

|               | 8.1                    | Integration into the Global Parallelization Approach               | 178          |

|               | 8.2                    | GA-based Approaches for Heterogeneous Architectures                | 180          |

|               |                        | 8.2.1 Chromosome Structure for Task-Level Parallelism              | 180          |

|               |                        | 8.2.2 Chromosome Structure for Pipeline Parallelism                | 183          |

|               |                        | 8.2.3 Objective Evaluation                                         | 186          |

|               |                        | 8.2.4 Mutation & Cross-Over                                        | 188          |

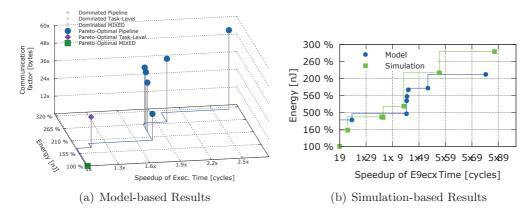

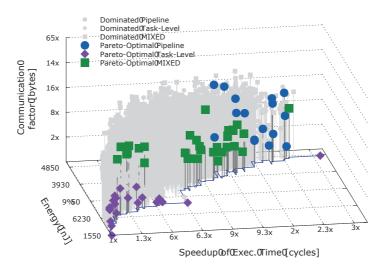

|               | 8.3                    | Experimental Results                                               | 189          |

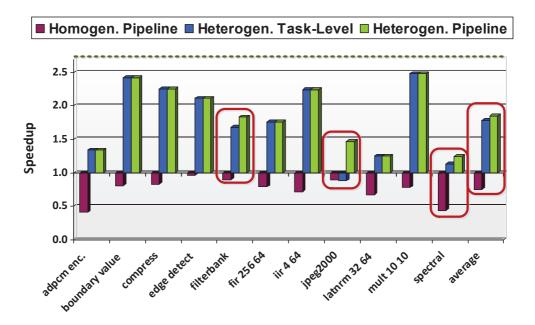

|               |                        | 8.3.1 Statistics of the GA-based Approaches                        | 192          |

|               | 8.4                    | Summary                                                            | 193          |

| 9             | Sun                    | nmary and Future Work                                              | 195          |

|               | 9.1                    | Research Contributions                                             | 196          |

|               | 9.2                    | Future Work                                                        | 198          |

| $\mathbf{A}$  | App                    | pendix                                                             | 201          |

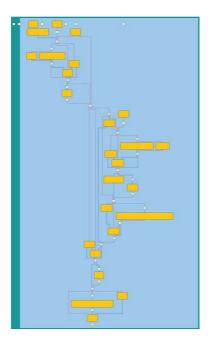

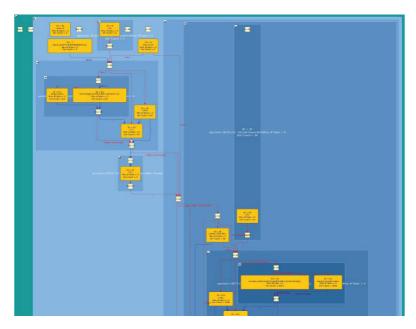

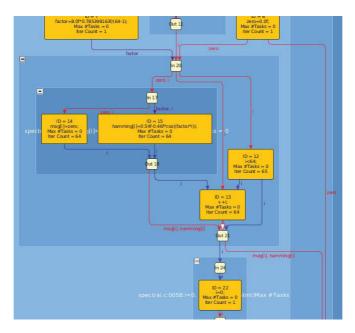

|               | A.1                    | Visualization Example of the Generated Augmented Hierarchical Task |              |

|               |                        | Graph (AHTG)                                                       | 201          |

|               | A.2                    | Additional ILP Formulations                                        | 203          |

|               |                        | A.2.1 And-Operator in ILP                                          | 203          |

|               |                        | A.2.2 Preconditions in ILP                                         | 203          |

| Bi            | bliog                  | graphy                                                             | 205          |

| Li            | st of                  | Figures                                                            | 221          |

| $\mathbf{Li}$ | st of                  | Algorithms                                                         | 225          |

| Li            | $\operatorname{st}$ of | Tables                                                             | 226          |

| $_{ m In}$    | dex                    |                                                                    | 227          |

# List of Abbreviations

AHTG Augmented Hierarchical Task Graph

DMA Direct Memory Access

DSP Digital Signal Processor

**DSWP** Decoupled Software Pipelining

**DVFS** Dynamic Voltage and Frequency Scaling

**DVS** Dynamic Voltage Scaling

FCDG Forward Control Dependence Graph

**GA** Genetic Algorithm

**HSCG** Hierarchical Structured Control-Flow Graph

HTG Hierarchical Task Graph

ILP Integer Linear Programming

KPN Kahn Process Network

LP Linear Programming

MNEMEE Memory Management Technology for Adaptive and Efficient Design

of Embedded Systems

MoCModel of ComputationMPIMessage Passing InterfaceMPSoCMultiprocessor System-on-Chip

**PA4RES** Parallelization for Resource Restricted Embedded Systems

PDG Program Dependence Graph

**PS-DSWP** Parallel-Stage Decoupled Software Pipelining

RAW Read-after-Write

SA Simulated Annealing

SDF Synchronous Data Flow

**SDL** Specification and Description Language

TLP Thread-Level Parallelism

UMA Unified Memory Architecture

UPC Unified Parallel C

**VLIW** Very Long Instruction Word

WAR Write-after-Read WAW Write-after-Write

**WSCDFG** Weighted Statement Control Data Flow Graph

# Introduction

#### Contents

| 1.1 | Motivation                                     | 3  |

|-----|------------------------------------------------|----|

| 1.2 | Automatic Parallelization for Embedded Systems | 5  |

| 1.3 | Contribution of this Work                      | 7  |

| 1.4 | Author's Contribution to this Dissertation     | 9  |

| 1.5 | Outline                                        | 11 |

The importance and pervasiveness of embedded and cyber-physical systems have significantly increased in the last two decades. Like defined in [Mar11], embedded systems are information processing systems that are embedded into enclosing products. Already in 2008 the number of sold smart phones reached 50% of the amount of desktop computer devices sold [Bus09]. Only three years later, in 2011, smart phone shipments surpassed the number of sold PCs [Bus11]. This statistic peaks in numbers which show that the smart phone shipments grew by 87% year over year while the number of sold PCs only grew by 3%, which highlights the increasing importance of embedded devices. But besides obvious devices like smart phones, most people do not recognize or even know when and with how many embedded systems they get into touch every day. Nowadays, a large number of areas of life are difficult or nearly impossible to cope without the help of embedded or cyber-physical devices. For example, traffic would collapse without the help of traffic lights especially in large cities. Also many means of transportation, like, e.g., cars, railways or airplanes are based on several distributed embedded controllers like anti-lock braking systems (ABS), electronic stability protection systems (ESP), airbags or collision avoidance systems. In addition, many people have to rely on their pacemakers to continue their lives in a regular way. These examples cover only a minor part of the enormous number of application domains of embedded systems that can be found in areas like automotive electronics, avionics, railways, telecommunication, the health sector, security, consumer-electronics, fabrication equipment, smart buildings, logistics, robotics, military applications, and many more [Mar11].

To solve the requirements of these examples, highly specialized embedded systems are required. Such systems, in contrast to desktop or high-performance architectures, underlie specific characteristics and resource limitations. These limitations have to be taken into account when embedded systems are designed and optimized. Certainly, one of the most significant aspects is the limited supply of energy caused by battery-driven devices. Other limitations, like, e.g., less computational power,

small memories, and limited package space for the designed devices apply to many embedded systems, as well. Consequently, dependability, efficiency and real-time behavior are highly important due to the restrictions and safety-critical application domains mentioned.

Besides these indispensable systems, many other embedded systems exist which try to make the peoples' everyday life more pleasant with multi-media, mobile and other services from the consumer electronics area. Especially for this application domain, an enormous alteration of the devices available on the market could be observed in the last two decades. Simple mobile phones with b/w screens and low resolution displays were replaced by powerful smart phone devices. A study [ITF12] from 2012 has recently shown that 49.7% of all American citizens already exchanged their ordinary mobile phones for such smart phone devices. High-resolution photos and videos are taken via mobile tablet PCs or smart phone devices before they are sent to friends all around the world via E-Mail or Messaging Services. In the home entertainment area, tube televisions were substituted by feature rich smart TVs enabling additional multi-media services like browsing, gaming and social networking while watching a movie. In the domain of automotive systems, not only luxury cars are nowadays equipped with a large network of sensors and embedded processors observing and steering the car while providing the occupants with music, video and navigation services. These examples cover only a minor part of the enormous changes that happened in the domain of multi-media rich embedded systems.

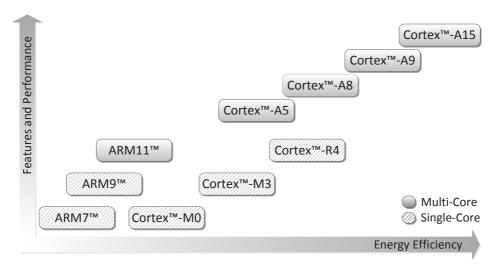

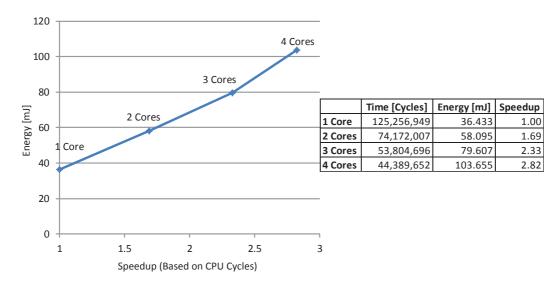

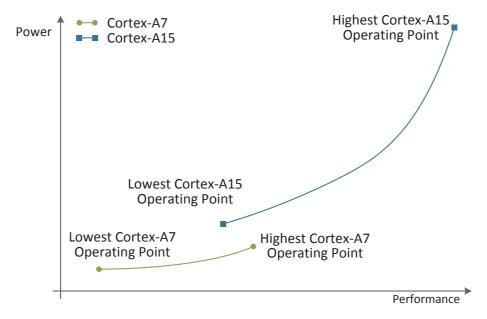

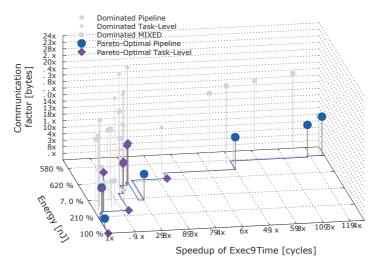

However, to be able to provide all these feature-rich services on mobile embedded devices, the complexity of the employed embedded software has also drastically increased. To fulfill the performance requirements imposed by today's embedded software, the performance of the underlying hardware has to scale, as well. In contrast to desktop and high-performance architectures, most embedded devices are battery-driven. This discourages the solution of just further increasing the cores' frequencies since higher clock frequencies generally lead to higher energy consumption. The last years have shown that the trend towards multi-core architectures seems to be the most promising solution to gain more performance while maintaining energy efficiency. In contrast to the desktop and high-performance community, embedded designers had to draw their conclusions in a much shorter period so that today's embedded systems often benefit from multi-core architectures. The trend towards multi-core architectures is also reflected in Figure 1.1 which compares performance and energy efficiency characteristics of ARM's most popular embedded processors. As can be seen, the shaded single-core processors ARM7 and ARM9 as well as most processors belonging to the Cortex-M and Cortex-R series are located at the bottom left to bottom central-position of the diagram denoting few features, low performance and low energy efficiency. In contrast, the shown multi-core processors ARM11 and the processors of the Cortex-A series are located at a position of the diagram which denotes higher energy efficiency and more performance. However, the performance of the presented single-core processors is also often increased by combining them to form multi-processor architectures. Especially the combination of different and specialized processing units to heterogeneous Multiprocessor 1.1. Motivation 3

**Figure 1.1:** Comparison of Performance and Energy Efficiency of Single- and Multi-Core ARM Processors (Based on Figure from [ARM13c])

System-on-Chip (MPSoC) devices revealed gainful trade-offs between performance, energy consumption, and other objectives, which are hard to obtain by homogeneous multi-core devices. The diagram emphasizes that the current state-of-the-art approach to provide feature-rich embedded systems with enough performance lies in the utilization of embedded MPSoC devices. Up to now, this technology has not reached an insurmountable limitation. Hence, it can be assumed that this trend will continue in the future, as well.

#### 1.1 Motivation

By providing multiple, less complex cores on one device, performance can be increased with a lower energy consumption compared to a platform containing only one core operating at a high CPU frequency. As a consequence, Multiprocessor System-on-Chip devices replace traditional embedded single-core architectures wherever more computational power is required. Unfortunately, the benefits of MPSoCs imply additional effort. A single application has to be partitioned into concurrently executed tasks to benefit from the multiple cores available on an MPSoC. Approaches developed earlier, extracting Instruction Level Parallelism for Very Long Instruction Word (VLIW) machines or superscalar processors, are not well applicable to multi-processor systems. Instruction Level Parallelism is too fine-grained since it executes only single statements in parallel. For MPSoC architectures, task creation and communication overhead is too high to use this kind of parallelism. Instead, Thread-Level Parallelism (TLP) is much more coarse-grained so that, in spite of the additional overhead introduced by task creation and communication primitives, this kind of parallelism can still lead to performance gains on multi-core architectures.

Recent surveys, as well as online articles, like, e.g., [TIO13], [Won12], and [Mer07], state that most software – especially for embedded systems – is still developed by using the sequential programming language C. This is not surprising since C compilers exist for a large amount of architectures which eases portability of highly optimized low-overhead application code. Moreover, the C language supports direct access to various hardware components and can be compiled into efficient machine code without the need for runtime interpreters. However, the sequential mindset of this programming language makes it difficult to extract Thread-Level Parallelism to exploit the performance provided by current MPSoCs. Traditionally, one of the following approaches can be used to exploit TLP:

- Re-Design in High-Level MoC: In early design phases of embedded systems high-level Models of Computation (MoCs), like, e.g., Kahn Process Networks [Kah74] or State Charts [Har87], are often applied. Many high-level MoCs inherently express parallelism by, e.g., concurrent states or services connected via explicit communication channels. This eases the step of implementing parallelism in later phases. Unfortunately, as already stated, most embedded software was developed in sequential C for decades. Thus, millions of lines of legacy code have to be ported to one of the considered MoCs to benefit from the proposed advantages. Most companies will not invest the large amount of time and money required to port existing functionality. Hence, high-level MoCs may better be applied for new software projects instead of existing ones.

- Manual Parallelization: Manual parallelization of existing legacy code seems to be less time consuming than re-designing entire applications in highlevel MoCs. Several libraries and language extensions, like, e.g., PThreads [NBF96] and OpenMP [DM98], have been proposed for the C language enabling the extracting of parallelism for sequentially written C-applications. However, the task of manually parallelizing an application for MPSoCs is a particularly error-prone and also time consuming job. The application designer has to deliver the expected functionality of the designed software in an efficient and portable way, optimized for a specific hardware platform, and validated against hundreds of test cases. Besides this time consuming and complicated job, the application designer has to extract and balance tasks as well as to insert communication and synchronization primitives manually. If one of these primitives is missed or placed at a wrong position, the application might get invalid or end up in a deadlock. This is a challenging problem which gets even more complicated if the targeted architecture is equipped with heterogeneous cores with differing performance characteristics.

- Automatic Parallelization: Automatic parallelization seems to be the most promising solution since existing legacy code can be divided into concurrently executed tasks automatically. In addition, tasks can be balanced for the available processing units and communication as well as synchronization primitives

can be inserted in a correct manner to avoid deadlock scenarios in an automated way. Furthermore, applications just have to be re-compiled by such tools to port them to various hardware platforms efficiently. Fortunately, many researchers invented a large amount of parallelization techniques in the last decades with a focus on desktop- and high-performance architectures. However, the problem of extracting efficient parallelism from sequentially written applications still remains unsolved and many limitations, especially for embedded systems, are not considered, as will be discussed in the following section.

### 1.2 Automatic Parallelization for Embedded Systems

By combining multiple cores on embedded MPSoCs, new possibilities arise in the context of embedded computing due to the increased performance provided by these devices. However, existing applications have to be parallelized to benefit from the additionally available cores. In an optimal way, this parallelization step should be automated as stated in the previous section. But even though a large amount of parallelization approaches already exists, most of them are optimized for high-performance architectures and are hence not well applicable to resource-restricted embedded MPSoCs. The reason for this limitation is the rise of rather new requirements for embedded multi-core systems, which were hard to foresee from the perspective of the high-performance community. Therefore, new and highly-optimized parallelization techniques are indispensable to utilize embedded MPSoCs efficiently, which was the ambitioned idea for this thesis.

From an embedded perspective, for example, less parallelism and thus less performance is often more. An application which runs several times faster than its given deadline consumes an unnecessarily large amount of energy. As soon as the given deadline is still met, less parallelism may be extracted so that an architecture with fewer and less performant cores can be used which drastically reduces the overall energy consumption. These energy savings lead to a higher battery service life and are important for embedded systems that are often applied in a mobile context. Moreover, due to the simplicity of many embedded devices – in contrast to highperformance architectures – overhead introduced by parallelism (e.g., task creation and communication overhead) is often costly. Accordingly, techniques are necessary to weigh whether parallel execution really accelerates the application. Misjudgment may directly lead to lower performance and higher energy consumption. These and also other requirements and characteristics, like, e.g., heterogeneity of the employed processing units, are mostly not considered by existing parallelization approaches so far. Therefore, the parallelization approaches presented in this thesis were designed to fill this desideratum of missing parallelization tools tailored towards special requirements of embedded MPSoCs.

The most important aspects, which have to be taken into account if applications should be parallelized for embedded MPSoCs, are discussed from a more technical perspective in the following:

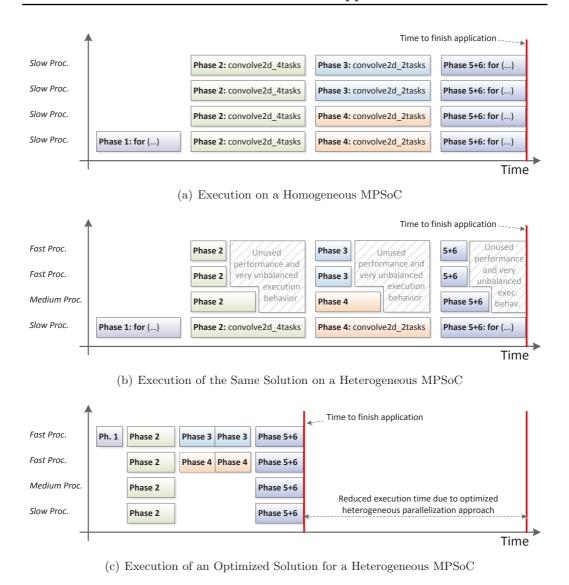

Task Balancing: In order to profit most from multi-processor platforms created tasks should be balanced so that all tasks finish nearly at the same time. Otherwise, much performance and also energy may be lost since some of the cores wait for completion of other ones leading to an unbalanced execution behavior. For embedded devices, task balancing is even more complicated and also more important. In contrast to desktop and high-performance architectures, most embedded systems are not constructed as an Unified Memory Architecture (UMA) where each core can access all memory locations. In the case of embedded systems, memory hierarchies are often employed, providing fast and low-energy private memories. Since these memory locations can neither be accessed nor cached by other processing units, communication is often much more expensive for most considered objectives. This even increases the gap between communication and computation costs for embedded systems. As a consequence, extracted parallelism has to be much more coarsegrained for many embedded devices, and it should be clearly deliberated whether parallelization really accelerates the performance of the application. Otherwise, too expensive task creation and communication costs may shadow the benefits of the extracted parallelism and may even lead to a decrease of the application's performance in the worst case.

Multiple Optimization Objectives: Most existing parallelization tools focus on the optimization of the execution time as their only optimization objective. This is, in general, acceptable for desktop and high-performance architectures since large memories and – spoken from an embedded perspective – a nearly unlimited amount of energy are available. The situation changes if parallelization tools focus on embedded devices. Here, multiple objectives should be taken into account simultaneously. It may, for example, be beneficial to reduce the amount of extracted parallelism to put some of the cores into idle mode or to move to an architecture with less provided cores if a given timing criterion is still met. This can reduce the system's energy consumption, heating problems, and can also save chip area.

Online vs. Offline Decisions: Additional overhead for runtime decisions should be avoided as much as possible due to lower computational power of embedded devices and the demand for timing predictability. OpenMP, for example, observes the number of executed tasks to decide at runtime how many tasks will be created if a new parallel region is reached. This behavior is not well suitable for embedded systems. Here, the number of created tasks should be determined off-line at compile time. As a result, the number and computational complexity of the extracted tasks can be optimized for a given architecture.

**Type of Parallelism:** Applications often profit differently from the available parallelization strategies. This makes it hard to find an optimal parallelization type for various application domains. However, many embedded applications have a streaming-oriented structure and profit from pipeline parallelism [TF10]. In ad-

dition, other parallelization strategies, like, e.g., task- and data-level parallelism, should be combined with pipeline parallelism to profit from different parallelization strategies and also a combination of them. Most existing parallelization frameworks focus only on the extraction of one kind of parallelism so that they are not well suitable for a wide range of application domains.

Heterogeneity: The advantages of heterogeneity in type and performance characteristics of the employed processing units are often utilized in embedded MPSoCs. By combining cores with different performance characteristics, less computational intensive tasks can, for example, be mapped to less performant processing units which consume less energy. However, the task of extracting and balancing parallelism for a heterogeneous MPSoC is much more complicated than for homogeneous ones but should also be considered by parallelization tools that are optimized for embedded systems.

### 1.3 Contribution of this Work

Even though automatic parallelization has been an active research area for decades, existing approaches are not well applicable to parallelize sequentially written applications for embedded MPSoCs. In order to overcome this limitation, this thesis presents a new framework including several novel approaches tailored towards limitations and special requirements that have to be taken into account if applications should be efficiently parallelized for embedded MPSoCs.

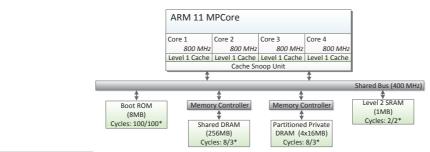

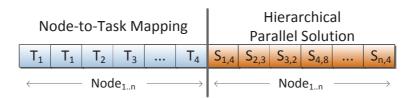

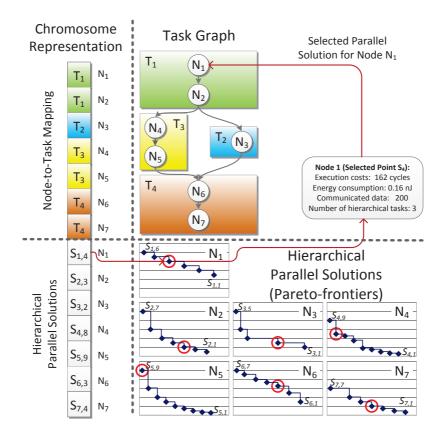

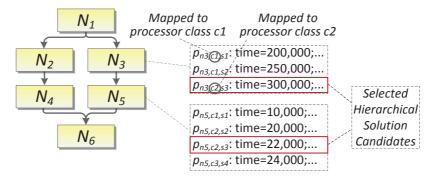

As already discussed in the previous section, automatic balancing of extracted tasks is an important aspect to parallelize embedded software efficiently (cf. Task Balancing). To achieve this, sophisticated parallelization approaches based on Integer Linear Programming and Genetic Algorithms are proposed and integrated into the presented framework of this thesis. All approaches employ high-level cost models to evaluate the benefit of different parallel solution candidates. The cost models contain information about task creation, execution, and communication costs for multiple objectives to steer the granularity of the extracted parallelism automatically. Integer Linear Programming is NP-complete in the general case but can be solved efficiently for small or medium-sized problems. Therefore, the framework presented in this thesis employs a hierarchical parallelization approach using an Augmented Hierarchical Task Graph (AHTG) as central intermediate representation. The hierarchical structure of the graph directly correlates to the hierarchical structure of the application's source code. Only a small number of statements are processed at once, due to the segmentation into different hierarchical levels. This enables the use of the sophisticated parallelization algorithms presented in this thesis.

To extract parallelism from applications of different application domains, the framework presented in this thesis combines three different parallelization types, namely, task-level parallelism, loop-level parallelism and pipeline parallelism (cf.

Type of Parallelism). The considered applications can profit either from one or also from a combination of the presented parallelization types. All parallelization extraction techniques are integrated into the hierarchical parallelization approach. By combining different approaches on several hierarchical levels, parallelism with different granularities can be extracted to find solutions optimized for various applications. The framework can also be easily extended by additional parallelization approaches, due to its hierarchical structure.

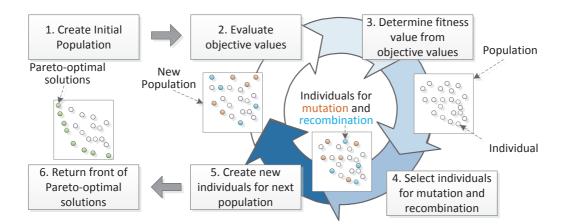

In contrast to many existing parallelization approaches, this thesis also presents parallelization techniques considering multiple optimization objectives at the same time (cf. Multiple Optimization Objectives). In this way, energy consumption and communication overhead can be optimized in addition to the execution time. The presented techniques return a front of Pareto-optimal solutions to the application designer so that the solution fitting best to a particular application scenario can be chosen as final solution. All considered parallelization types (task-level, loop-level and pipeline parallelism) are developed as multi-objective aware parallelization techniques.

The parallelization techniques presented in this thesis also make use of platform specific information of the target architecture (cf. Online vs. Offline Decisions). This enables platform specific optimizations, taken at compile-time, which are directly integrated into the parallelization process. One example for these offline optimizations is the limitation of the maximum number of extracted tasks. For each presented approach, the upper bound of extractable tasks is set to the number of available processing units by default. Then, the hierarchical approach determines the best combination of different solution candidates which do not exceed the upper task boundary. As a consequence, additional scheduling overhead at runtime can be avoided.

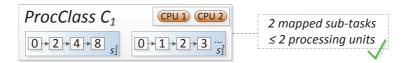

Heterogeneity is one key aspect for current and future embedded MPSoCs (cf. Heterogeneity). By combining cores with different performance characteristics, performance increases can be achieved with lower energy consumption and less heat dissipation issues compared to homogeneous MPSoCs. Unfortunately, the complexity of the parallelization problem drastically increases since these performance variances have to be taken into account if the extracted tasks should be automatically balanced. Therefore, the presented framework also contains novel approaches extracting the considered parallelization types for single and also multiple objectives simultaneously. The approaches optimize tasks for specific processing units and take care that these tasks are mapped to the corresponding cores by processor class premappings. This makes the presented framework also able to utilize heterogeneous multi-core architectures in an efficient way.

To summarize, this thesis presents and combines the following novel aspects:

- Exploitation of platform specific information, like estimated execution and task creation costs

- Automatic balancing of tasks by all presented approaches

- Integration of cost models into sophisticated Integer Linear Programming and Genetic Algorithm-based approaches instead of applying simple heuristics

- Multiple objectives are considered at the same time instead of just optimizing execution time

- Support for homogeneous and heterogeneous architectures

- Combination of several parallelization types with different granularities optimized for embedded applications

- Many decisions are taken offline at compile-time to avoid additional runtime overhead

- Use of a hierarchical divide-and-conquer based parallelization approach to prune the vast solution space of the complex parallelization problem for sophisticated algorithms

#### 1.4 Author's Contribution to this Dissertation

According to §10(2) of the "Promotionsordung der Fakultät für Informatik der Technischen Universität Dortmund vom 29. August 2011", a dissertation within the context of doctoral studies has to contain a separate list that highlights the author's contributions to research and results obtained in cooperation with other researchers. Even though, the approaches presented in this thesis were entirely envisioned and developed by the author of this thesis, Prof. Dr. Peter Marwedel contributed the generalized idea to develop parallelization approaches that are optimized for resource-restricted embedded systems. He also gave useful advices, like, e.g., extending the framework to parallelization approaches for heterogeneous architectures. Thus, the author of this thesis would like to thank him, here, once again. Besides these advices, the following list describes the author's contribution to publications leading to the chapters of this thesis in more detail:

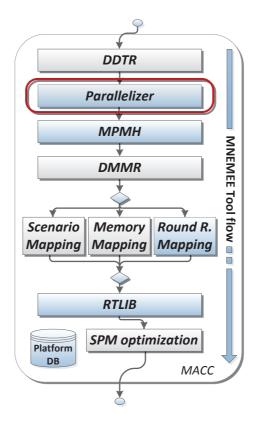

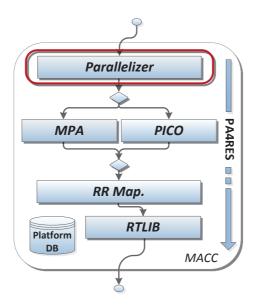

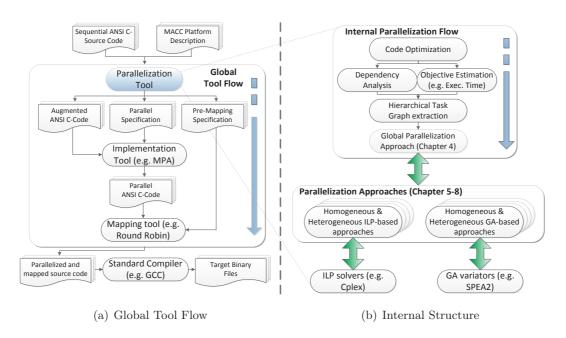

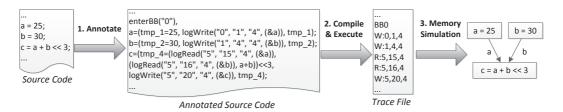

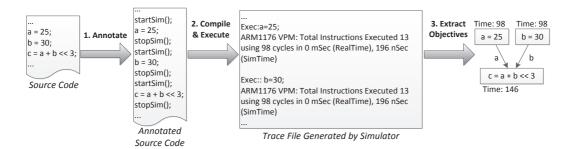

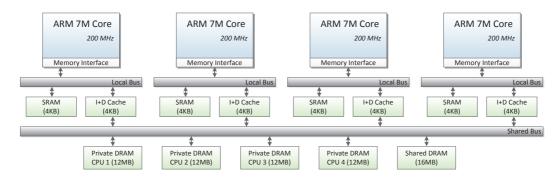

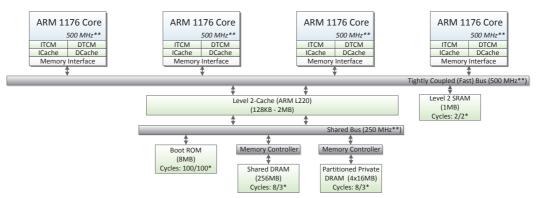

Chapter 3: Chapter 3 presents internals of the parallelization framework and additional tools which are used to map the parallelized applications to an embedded MPSoC. A brief overview of the parallelization framework's internals is also given in [CMM10]. The integration of the parallelization approaches into the framework developed in the European FP7 project MNEMEE was described in [BPS+10]. Several authors cooperated in writing this publication. The author of this thesis provided the text for Chapter II.C in [BPS+10] describing the first parallelization approach developed in the context of thesis. The remainder of Chapter 3 describes the target platforms used for simulation-based evaluations in Chapters 5-8. The employed simulators are the MPARM [BBB+05] and Synopsis's CoMET [Syn13a], which is more recently know as the Virtualizer tool suite [Syn13b]. The provision and adaptation of the platforms were mostly done by Andreas Heinig and was only assisted by the author of this thesis.

Chapter 4: General concepts of the parallelization framework including the employed intermediate representation are presented in Chapter 4. The general idea described in this chapter was briefly published in [CMM10] and [CHM+11] but was also summarized in other publications of the author for comprehensiveness. Chapter 4 of this thesis contains also many unpublished details about the employed hierarchical parallelization approach. The presented Augmented Hierarchical Task Graph (AHTG) is based on the Hierarchical Task Graph (HTG) presented in [GP94]. The changes made to the graph intermediate representation and the way how to use it to extract parallelism with the sophisticated parallelization techniques presented in this thesis were completely developed by the author of this thesis. However, the author was inspired by many technical discussions with Prof. Dr. Peter Marwedel, members of the department, and participants of the MNEMEE project. Nonetheless, the publications in [CMM10] and [CHM+11] were entirely designed by the author of this thesis. The co-authors of the publications, as well as other members of the department, assisted the author in various ways.

Chapter 5: Two Integer Linear Programming-based parallelization approaches extracting task-level and pipeline parallelism for homogeneous architectures are presented in Chapter 5. Both approaches were entirely designed and developed by the author of this thesis. The corresponding publications [CMM10] and [CHM+11] are entirely based on the author's work. The co-authors of the publications, as well as other members of the department, assisted the author in technical and conceptual discussions especially how to structure the publications. Additionally, many parts were intensively revised by the co-authors.

Chapter 6: Chapter 6 describes multi-objective aware approaches for homogeneous MPSoCs. It is based on the publications presented in [CM12] and [CEM+12]. Both approaches, as well as the publications, were completely designed, developed and mostly written by the author of this thesis. The co-authors, as well as other members of the department, assisted the author in proof-reading, providing small text fragments, and various technical as well as methodological discussions.

Chapter 7: This chapter presents two ILP-based parallelization approach for heterogeneous embedded MPSoCs, which are based on the homogeneous ones presented in Chapter 5. The developed approaches were published in [CEN+13c] and [CEN+13b]. The co-authors of the publications assisted the author of this thesis in writing the introduction of the papers, proof-reading and technical discussions.

Chapter 8: This chapter finally presents the last developed parallelization approaches focusing on multi-objective aware parallelization approaches for heterogeneous MPSoCs, which were published in [CEN+13a]. The co-authors of the publication assisted the author of this thesis in writing the introduction of the paper, proof-reading and technical discussions.

1.5. Outline 11

<sup>\*</sup> DoAll Data-Level Parallelism is also extracted as a special case of the pipeline parallelization approaches presented in the corresponding sections.

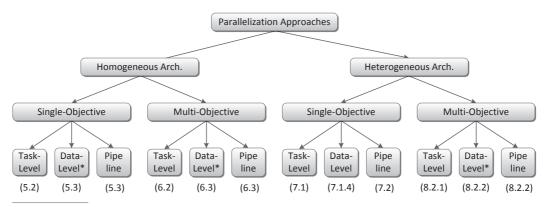

Figure 1.2: Structure of Thesis and Contributions of Dissertation

### 1.5 Outline

This section gives an overview about the remaining structure of this thesis. The tree visualized in Figure 1.2 shows the developed parallelization approaches and the corresponding sections describing them. In detail, the following content is described in this thesis:

**Chapter 2:** A survey of related work is presented in Chapter 2. The approaches selected for discussion are the most relevant ones for the work presented in this thesis. The presented publications are grouped into categories reflecting the different key concepts considered by the approaches of this thesis.

**Chapter 3:** The internal structure of the parallelization framework with all its sub-tools and its integration into larger projects, like, e.g., the MNEMEE European FP 7 project, is described in Chapter 3. Furthermore, the chapter also presents the target platforms used for evaluation purposes in the remainder of this thesis.

Chapter 4: This chapter presents the general idea and the techniques used to divide the large search space of the parallelization problem into manageable subproblems. These sub-problems can later be processed by the sophisticated parallelization approaches presented in Chapters 5-8. In more detail, the chapter defines the employed intermediate representation and gives an overview about the structure of the general parallelization algorithm.

**Chapter 5:** The first parallelization approaches developed within this thesis focus on the extraction of parallelism for homogeneous architectures. They are presented in Chapter 5 and extract task-level, loop-level and pipeline parallelism on basis of Integer Linear Programming (cf. Homogeneous Single-Objective Parallelization in

Figure 1.2). All approaches use high-level cost models to be able to evaluate and balance extracted tasks automatically.

Chapter 6: The parallelization techniques presented in Chapter 6 extract the different parallelization types in a multi-objective aware manner for homogeneous architectures (cf. Homogeneous Multi-Objective Parallelization in Figure 1.2). They are based on Genetic Algorithms and also employ high-level cost models to evaluate the different parallelization candidates.

Chapter 7: Heterogeneous architectures are first considered by the parallelization approaches presented in Chapter 7 (cf. Heterogeneous Single-Objective Parallelization in Figure 1.2). The presented ILP-based techniques are based on the ones presented in Chapter 5. However, the newly presented techniques are extended to, e.g., distinguish between different performance characteristics of the available processing units and to perform a pre-mapping of extracted task to processor classes.

Chapter 8: The parallelization approaches presented in Chapter 8 are a consequent combination of the techniques presented in Chapters 6 and 7. Multi-objective aware parallelization approaches, which are able to extract and balance tasks fully automatically for heterogeneous architectures, are presented there (cf. Heterogeneous Multi-Objective Parallelization in Figure 1.2).

**Chapter 9:** Finally, Chapter 9 concludes this thesis and provides possible directions for future research.

# Related Work

#### Contents

| 2.1 | Task-Level Parallelism                     | 14        |

|-----|--------------------------------------------|-----------|

| 2.2 | Data-Level Parallelism                     | 16        |

| 2.3 | Pipeline Parallelism                       | 19        |

| 2.4 | Multi-Objective Aware Extraction           | 22        |

| 2.5 | Extraction for Heterogeneous Architectures | 24        |

| 2.6 | Additional Approaches                      | <b>25</b> |

| 2.7 | Summary                                    | <b>26</b> |

|     |                                            |           |

Parallel architectures have been invented decades ago. As a consequence, a lot of research effort was invested to utilize those platforms efficiently. Even though many high-level programming languages or extensions to existing ones have been proposed, like PThreads [NBF96], MPI [SOHL+98], OpenMP [DM98], OpenCL [SGS10], X10 [CGS+05], StreamIt [TKA02], UPC [EGCS+03], Cilk [BJK+95], and many others, most of them are not prevalent to parallelize applications in the domain of embedded systems. A different strategy for implementing parallel embedded applications, suggested in the last years, was to model those applications by highlevel Models of Computation (MoCs). MoCs, like State Charts [Har87], Petri Nets [Pet66], Specification and Description Language (SDL) [RS82], Kahn Process Networks (KPNs) [Kah74], and Synchronous Data Flow (SDF) [LM87], to mention only some of them inherently express parallelism. However, most existing legacy code for embedded devices is written in sequential C code and most companies are not willing to invest a huge budget to rewrite existing, comprehensive application code in another programming language or to transform it to one of the mentioned MoCs. Hence, the demand for automatic parallelization frameworks was created and increased over the last decades in order to be able to reuse already existing functionality.

Since the research work of this thesis presents approaches which extract coarsegrained Thread-Level Parallelism (TLP) in an automatic fashion, this chapter gives a brief overview about related frameworks and critically discusses the approaches presented in this area. The primary objective of this chapter is to compare functionalities and limitations of existing approaches, which are most relevant to the techniques presented in this thesis. Therefore, those approaches are discussed in more detail instead of aspiring completeness over all presented approaches. The approaches are grouped into different categories in the following sections. Of course, some approaches may be mapped to more than one category since they extract different types of parallelism. In this case, they are placed into the category matching their main contribution.

The structure of this chapter is as follows: Section 2.1 presents approaches extracting coarse-grained task-level parallelism, followed by a discussion of finer grained data-level parallelization techniques in Section 2.2. Pipeline parallelism is highly effective for many embedded applications. Therefore, Section 2.3 opposes different approaches extracting this kind of parallelism. Parallelization techniques considering multiple objectives and heterogeneous architectures are rarely new research topics. Sections 2.4 and 2.5 give a brief overview about the work done in these areas. Finally, Section 2.6 discusses some approaches which go beyond the extraction of TLP before Section 2.7 summarizes features and limitations of existing approaches.

### 2.1 Task-Level Parallelism

Task-Level parallelism is a coarse-grained kind of Thread-Level Parallelism. Large independent blocks of an application are processed by concurrently executed tasks. These blocks may consist of functions, basic blocks or also single statements, depending on the desired level of granularity (for more details see Section 5.2). Task-Level parallelism can be employed in the context of embedded systems efficiently since in many cases only few data has to be communicated between the different tasks. Therefore, the approaches presented in Section 5.2, Section 6.2, Section 7.1 and Section 8.2.1 propose techniques extracting this kind of parallelism for homogeneous and heterogeneous embedded MPSoCs for one and also for multiple objectives. In the following, the most relevant existing approaches extracting this kind of parallelism are discussed.

Sarkar: The approaches presented by Sarkar et al. in [Sar91a] are most relevant to the task-level parallelization approaches presented in this thesis. They are based on the previous publications in [SH86] and [Sar89] and were integrated into IBM's PTRAN compiler [Sar91b]. Their approaches extract coarse-grained task-level parallelism combined with the extraction of DoAll loops (running independent loop iterations in parallel) from sequential applications written in Fortran. The employed Program Dependence Graph (PDG) is augmented with estimated execution times and transformed into a Forward Control Dependence Graph (FCDG) which is similar to the Augmented Hierarchical Task Graph (AHTG) used as central intermediate representation in this thesis. Both graph representations have in common that backward-dependence edges (pointing in the opposite direction of the regular control flow) are redirected to special exit (or communication-out) nodes. This ensures that the entire graph is cycle-free, enabling the calculation of execution times based on high-level models. Even though the employed intermediate representation and the calculation of estimated execution times are comparable to the ones used in

this thesis, Sarkar only exerts a simple greedy-based partitioning heuristic which is applied to one procedure at a time. The approaches presented in this thesis apply sophisticated Integer Linear Programming (ILP) and Genetic Algorithm (GA)-based approaches to extract task-level parallelism from sequential applications. This is only possible since the approaches divide an application into finer-grained chunks based on the hierarchical structure of the given source code. In this way, only a small portion of the application is considered at the same time which drastically reduces the vast solution space of the complex parallelization problem. The approaches presented in this thesis are able to balance the extracted tasks automatically, which is hard to achieve with the greedy heuristics proposed by Sarkar.

Polychronopoulos: Polychronopoulos and Girkar presented automatic scheduling techniques [Pol91] based on Hierarchical Task Graphs (HTGs) [GP94]. The approaches presented in this thesis are based on an Augmented Hierarchical Task Graph (AHTG) and differs from the original HTG representation published in [GP94] in three points. First, the approaches presented by Polychronopoulos et al. only create new hierarchical levels for nested loops of the original application. In contrast, the approaches presented in this thesis create new hierarchical nodes for all hierarchical levels present in the original application. Thus, the hierarchical structure of the graph directly correlates to the hierarchical structure of the application. In addition, the hierarchical granularity is more fine grained in the approach presented in this thesis which enables more sophisticated parallelization algorithms. The second difference to the original presentation in [Pol91] is that the approach presented here adds two new node types to the AHTG, namely communication inand communication out-nodes. These nodes encapsulate the communication in each hierarchical level. A third difference is that the approach presented in [Pol91] only deliberates about whether it makes sense to generate more tasks for the next hierarchical level based on architectural properties like the number of available processing units. Instead, the approaches presented in this thesis employ the AHTG as a layer to reduce the number of nodes which have to be processed at the same time while parallelizing the application. This means that the approach is also able to group some of the nodes on each hierarchical level to tasks instead of either executing all of them in parallel or executing all of them sequentially.

SUIF: Hall et al. presented coarse-grained thread-level parallelization techniques for C and Fortran applications in, e.g., [HAM+95] and [HAA+96], integrated in the Stanford University Intermediate Format Compiler Framework (SUIF) [WFW+94]. Their techniques employ interprocedural analyses to spawn threads spanning function boundaries. The presented framework is also able to apply analyses and optimization techniques, like, e.g., scalar privatization, reduction recognition, array analyses, and cache optimizations. As a target platform, Hall has chosen an eightcore Digital Alpha Server 8400 which was a high-performance architecture in 1995. Additional work on this framework was presented by, e.g., Sungdo et al. in [MSH00]

who evaluated the absent performance gain due to missing data-level parallelization support. Compared to the work presented in this thesis, Hall did not provide any information on cost models which are necessary to balance the created tasks. Moreover, the target architecture was a homogeneous high-performance one which is very different to embedded (heterogeneous) MPSoCs.

MAPS: A more recent task-level parallelization approach was presented by Ceng et al. in [CCS+08]. Their approach is integrated in the MPSoC Application Programming Studio (MAPS) and performs a semi-automatic parallelization technique in which the user can manually steer the granularity of the extracted parallelism. MAPS uses the Tightly-Coupled-Thread framework (TCT) [ZIU+08] as a backend for implementation and simulation of the extracted parallelism. MAPS combines static and dynamic profiling-based information to extract a Weighted Statement Control Data Flow Graph (WSCDFG) annotated with cost information. This cost information is based on a simple multiplication of a configurable execution cost with the number of executions per statement. Based on the WSCDFG, a heuristic clustering algorithm is applied to group statements subsequently to coarse-grained tasks. The heuristic of the original approach was further optimized in [LC10]. Later, C for Process Networks was presented in [CSL11] which allows an application designer to describe parallelism manually through Kahn Process Networks (KPNs) directly in C. Compared to the work presented in this thesis, MAPS extracts a similar kind of parallelism. In contrast to many other approaches, the authors use cost models to balance the extracted tasks. However, the precision of cost information is not very accurate, and the clustering algorithm is based on a simple heuristic compared to the novel sophisticated ILP-based approaches.

#### 2.2 Data-Level Parallelism

Data-level parallelism was not a main focus of this thesis. Only a simple approach is employed extracting data-level parallelism from loops without loop-carried dependencies. Therefore, a direct comparison to the approaches presented in this thesis is omitted in this section. However, many techniques that are able to extract fine-grained data-level parallelism from loops of sequentially written applications have been proposed in the past.

PIPS: The Parallélisation interprocédurale de programmes scientifiques project (PIPS) was first published in [IJT91] representing a modularly source-to-source parallelization framework. Initially, PIPS concentrated on DoAll parallelism by extracting tasks from loops of sequentially written Fortran 77 applications. PIPS's approach employs a Hierarchical Structured Control-Flow Graph (HSCG) as intermediate representation and was designed modular so that it could be extended by other parallelization approaches. Today, over 20 years later, the project is still active

and has been extended to, e.g., support the C language and polytope-based parallelization extraction techniques by various approaches like [KAC+96] and [KAI11].

Polaris: The Polaris parallelization compiler was presented in [BEF+95] targeting at the automatic extraction of DoAll parallelism in Fortran 77 applications. To be able to extract parallelism from loops with loop-carried dependencies, optimizations like, e.g., symbolic analysis, induction and reduction variable recognition and array privatization are applied to remove those dependencies. Polaris also contains speculative parallelization for loops whose dependencies could not be determined at compile time. However, such a parallelization technique is often unacceptable for embedded systems since predictability is important for many embedded devices. In addition, Polaris implements function inlining to circumvent inter-procedure analysis techniques. This is also not applicable for embedded devices since it increases the code size and the amount of available memory is often limited. The framework was also extended by other researchers in, e.g., [PE95] and [VE99].

Cetus: The Cetus parallelization compiler was presented in several publications, like, e.g., [LJE04] and [DBM+09]. The framework was written in Java and the source code was published as a freely available research compiler. The authors have taken the Polaris compiler as an inspiring example and tried to create a similar framework for C programs and other target languages instead of Fortran 77. The framework also contains several analysis and code optimization techniques, like, e.g., privatization, reduction variable recognition, and induction variable substitution. However, the framework focuses on data-level parallelism only, and does not apply any cost models to weigh the granularity of parallelism. This can also be seen in their evaluation, where the authors claim that their parallelization tool flow performs better than Intel's icc compiler and the COINS framework [SFF+05]. This comparison is only based on the number of successfully parallelized loops without measuring the performance gain. In reality, many loops may reduce the overall performance if the benefit from parallelization is lower than the required communication and task-creation costs. This is not considered or at least not mentioned in their publications.

Polytope-based approaches: Polytope-based parallelization approaches like the one presented in [Fea96] are favored for extracting data-level parallelism. The iteration space of sequential loop(-nest)s including data- and control flow dependencies is transformed into a form of linear inequalities. Based on this mathematical description, loops can be parallelized in an automated way. Another work in this area was presented in [VNS07] and is based on results of the Compaan project [BRD00; RDK00; TK04]. It extracts Process Networks (PNs) from sequential C applications and is integrated in the MADNESS project's tool flow [CDF+11]. Process Networks can then be efficiently mapped to multiprocessor platforms. Verdoolaege et al. also tried to optimize communication and to determine FIFO buffer sizes. However, their work does not evaluate the speedup of an extracted PN and is limited to static affine

nested loop programs so that it can, in general, not be applied to existing applications without manual transformations. Furthermore, no performance estimation is applied to deliberate about the granularity of the extracted parallelism. This may lead to an unbalanced execution behavior which drastically reduces the applications' performance. Their tool was also used in the Daedalus project [NTS+08] to extract the required KPNs for the succeeding optimizations for multiprocessor architectures. Additional polytope-based parallelization frameworks were, e.g., presented in LooPo [GL97] and PLUTO [BHR+08].

Franke: Franke et al. also aim at the extraction of data-level parallelism in [FO05]. The difference to the other presented approaches is that their work focuses on specific issues, which have to be solved if applications are parallelized for embedded multi-core Digital Signal Processor (DSP) platforms. Particular program recovery techniques like array recovery and modulo removal are applied before data-level parallelism is extracted. Moreover, their approach also performs memory optimizations, which use Direct Memory Access (DMA) transfers to optimize the overall performance further for DSP architectures.

Li: Li et al. presented an approach in [LPC12] which extracts data-flow threads from sequentially written imperative programming languages. Therefore, a Program Dependence Graph (PDG) is transformed into SSA form (SSA-PDG) to ease the definition of dependencies. This SSA-PDG is coarsened in the following by several coalescing techniques. The merged nodes of the final graph represent data-flow tasks, which are implemented by a GCC compiler [The13] extension. Unfortunately, the presented approach is only able to exploit data dependencies for scalar variables, which limits its applicability to real world applications. The approach was neither evaluated for embedded applications nor embedded devices.

Pouchet: Pouchet et al. published a framework combining different multi-dimensional loop optimization techniques in [PBC+08]. Their framework was later extended in [PBB+10] to support the extraction of loop-level parallelism. The complexity of their optimization problem as well as the employed optimization algorithms are comparable to the ones used in the context of this thesis. In both cases, a large optimization space is present so that smart optimization techniques had to be chosen. Therefore, Pouchet et al. used an iterative model-driven Genetic Algorithm-based approach in [PBC+08] with specialized mutation and cross-over operators. They have shown that this technique is able to find very good solution candidates in a short amount of time. Similar results could also be observed for the GA-based approaches presented later in the context of this thesis.

**Benoit:** The dissertation of Benoit [Ben11] describes a source-to-source parallelism adaption tool which is integrated into the GCC Compiler. It combines static and dynamic analysis techniques to detect and describe parallelism opportunities at

several hierarchical levels. However, the thesis concentrates on defining a suitable intermediate representation and does not focus on the extraction of parallelism in an automated way like done in this thesis.

### 2.3 Pipeline Parallelism

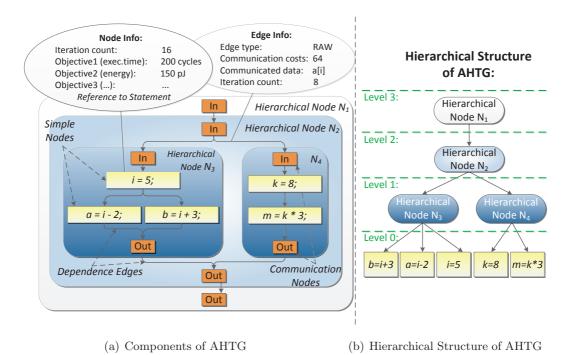

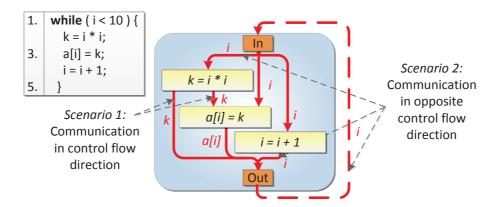

Pipeline parallelism is the third kind of thread-level parallelism discussed in this chapter. It can be used to extract efficient parallelism from many embedded applications, especially those which are written in a streaming-oriented structure. Pipeline parallelism can often be applied even if ordinary data-level parallelism (e.g. DoAll loops) cannot be extracted due to loop-carried dependencies. The statements contained in a loop's body are partitioned into disjunctive pipeline stages which execute in an overlapping, pipelined manner on different cores (for more details see Section 5.3). Since pipeline parallelism is often hidden in embedded applications, this thesis also presents different approaches in Section 5.3, 6.3, 7.2, and 8.2.2 which extract this kind of parallelism in an automated fashion for homogeneous and heterogeneous embedded MPSoCs. In the following, the most important existing approaches extracting pipeline parallelism are discussed.

Rangan: Decoupled Software Pipelining (DSWP) was first introduced by Rangan et al. in [RVV+04]. The proposed approach focuses on loops operating on recursive data structures. Rangan et al. manually extracted extremely fine-grained pipeline stages and recognized that the communication delay on a Pentium 4 Xeon Processor is too high to benefit from DSWP. Therefore, they proposed low-latency synchronization arrays for communication between different cores. Compared to the approaches presented in this thesis, Rangan et al. manually applied DSWP to the chosen benchmarks.

Ottoni: Ottoni et al. based their DSWP approach [ORS+05] on the one proposed by Rangan et al. in [RVV+04]. In contrast to the work of Rangan et al., Ottoni et al. extract DSWP fully automatically and integrated their approach into the IMPACT compiler back-end [ACM+98]. Moreover, they have shown that DSWP can be applied efficiently to various loops, even if they are not operating on recursive data structures. Ottoni's approach employs message passing to communicate data between producing and consuming tasks. The algorithm operates on a program dependence graph (PDG) [KA02] which is transformed into a directed acyclic graph (DAG) [Tar72] by clustering the strongly connected components formed by data-and control dependencies. The extracted pipeline stages are balanced by a greedy heuristic which merges the node with the highest estimated cycles (extracted by profiling in the compiler back-end) to the currently processed pipeline stage. This step is repeated until the estimated cycles of the current partition reaches the overall estimated cycles divided by the number of extracted stages. Compared to the approaches presented in this thesis, Ottoni's DSWP approach has some disadvan-

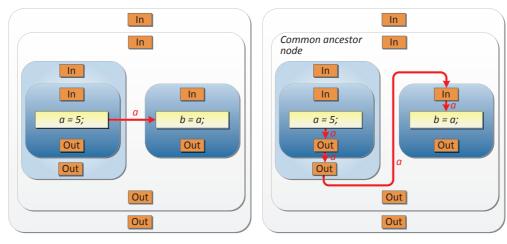

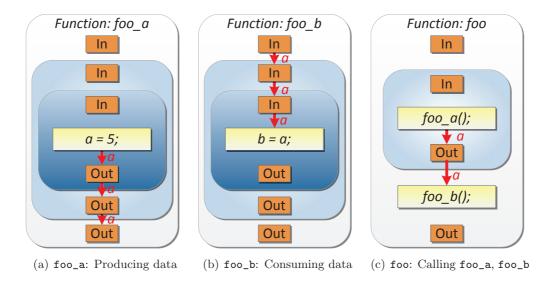

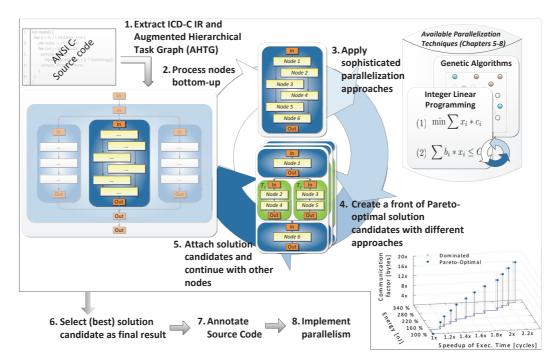

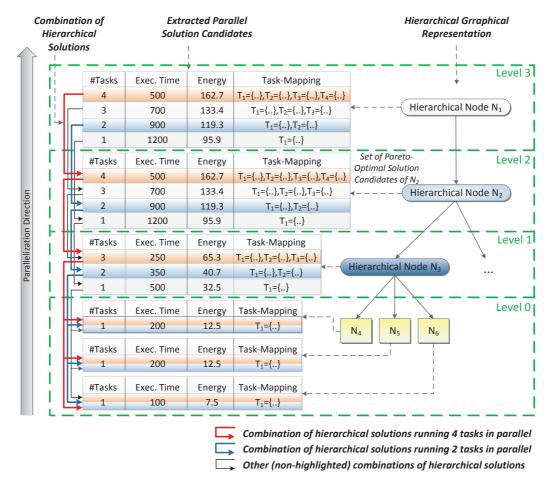

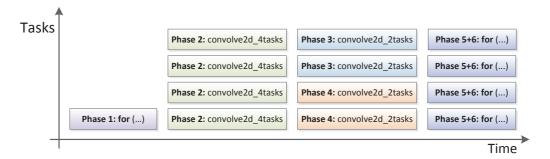

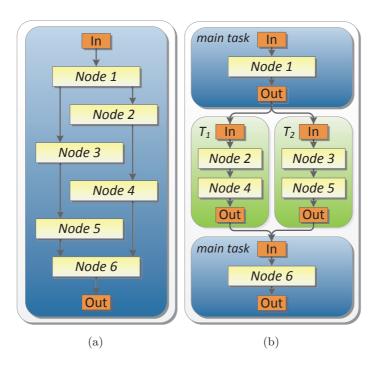

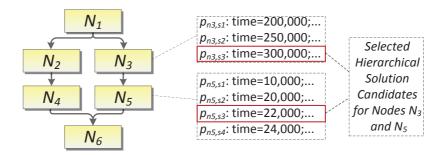

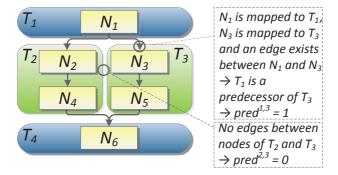

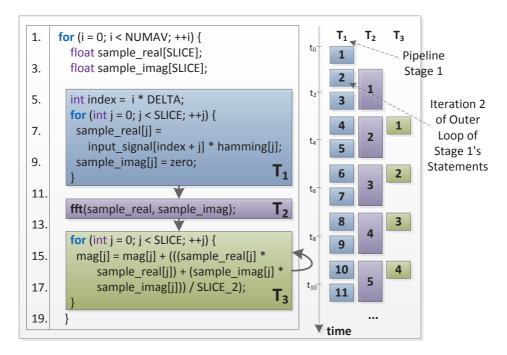

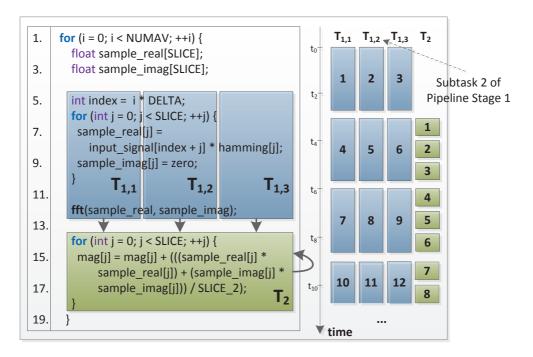

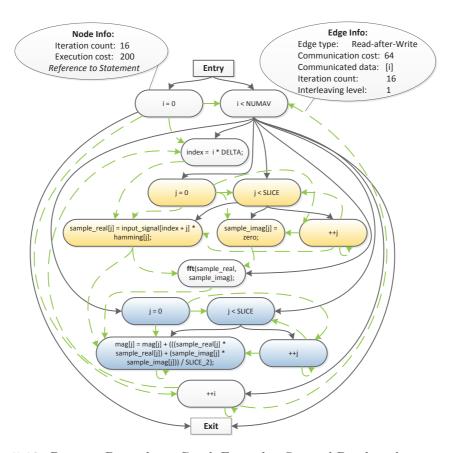

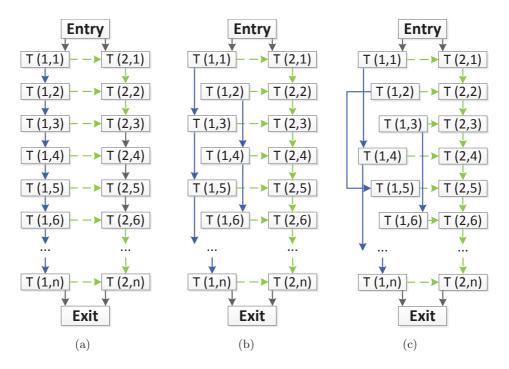

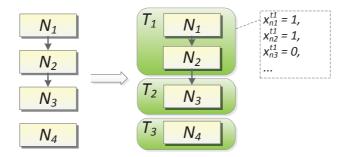

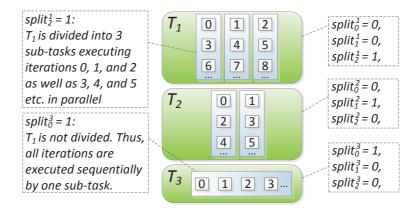

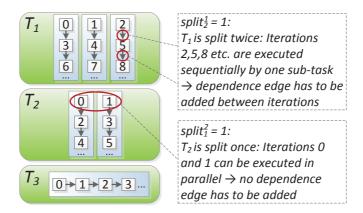

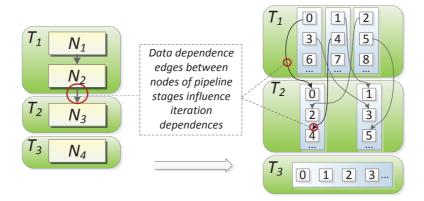

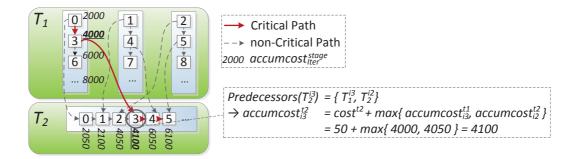

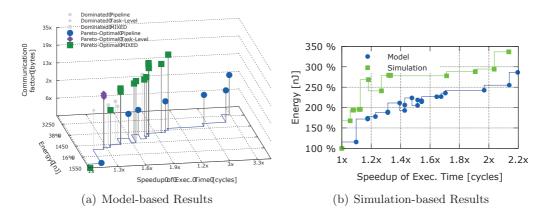

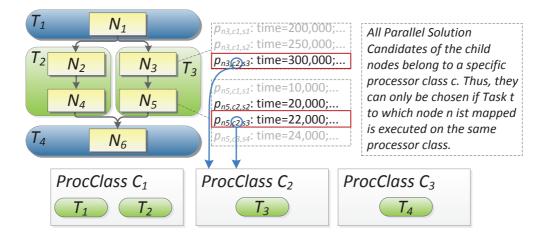

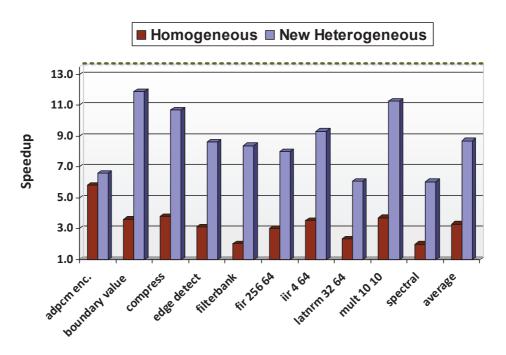

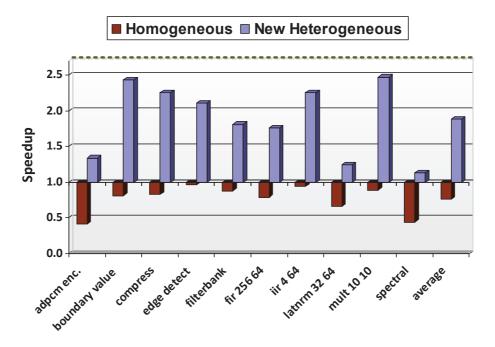

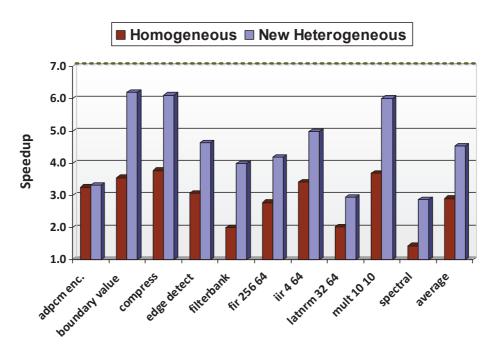

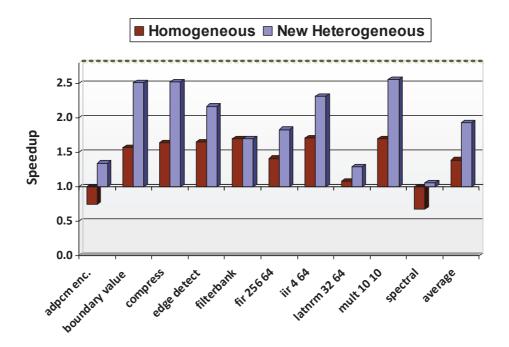

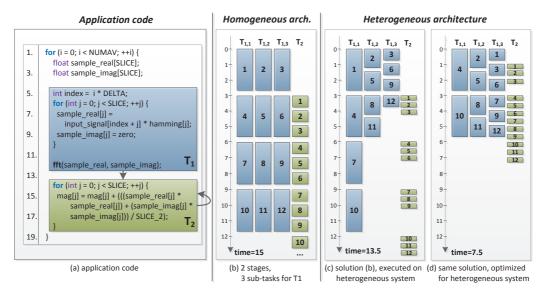

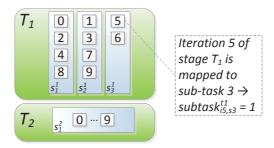

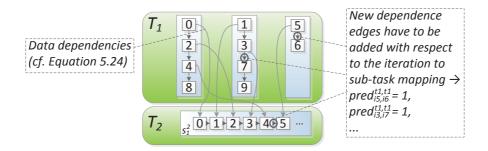

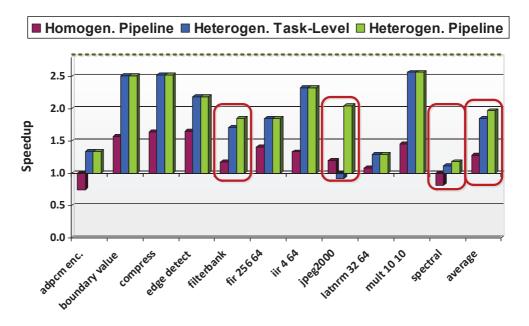

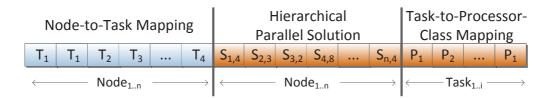

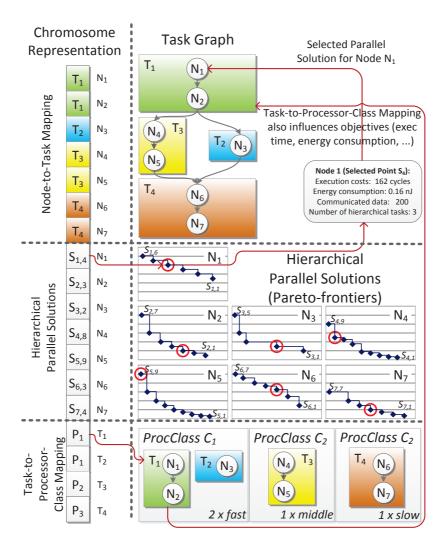

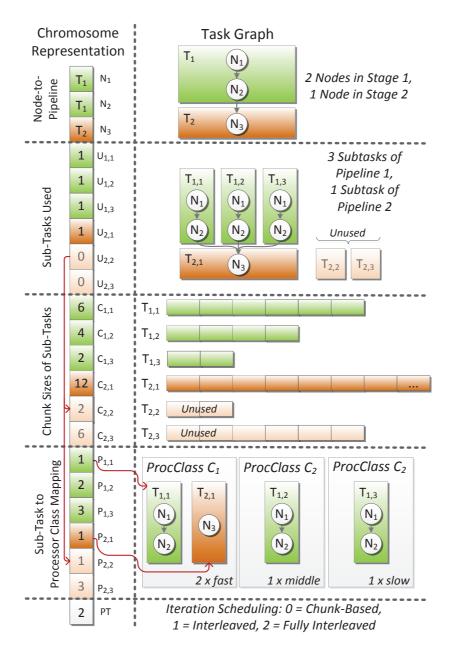

tages. First, even though it extracts pipeline parallelism – which is efficient for many embedded applications – the approach was not optimized nor evaluated for embedded or at least heterogeneous architectures. Second, their approach only extracts disjunctive pipeline stages which are not replicated to further increase the overall performance. And, finally, it operates on assembler level which drastically limits portability, readability and the possibility to present the extracted results to the application designer in a comprehensible form.