Alexander Gumprich

Fabrication of Steep Slope Carbon Nanotube Transistors on Novel Multi-Gate Substrates Cover images:

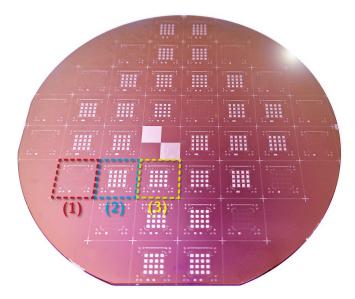

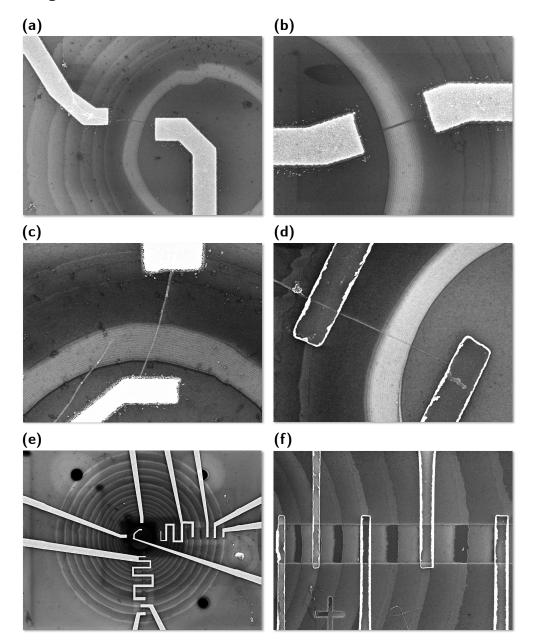

Boxes, left to right: (1) Micrograph of a buried graphene triple gate sample. (2) SEM Micrograph of a contacted carbon nanotube on a buried multi gate sample. (3) 80-degree SEM Micrograph of a buried graphene heterostructure. (4) Sample with five probing needles on a temperature controlled vacuum chuck.

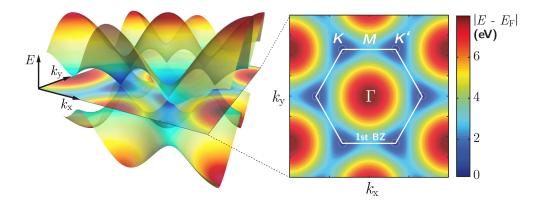

Background: 3D plot of the dispersion relation of graphene made with open source visualizer 3dmath

Cover design by A. Gumprich

Fabrication of Steep Slope Carbon Nanotube Transistors on Novel Multi-Gate Substrates

Dissertation - Technische Universität Dortmund, 2023 Alexander Gumprich

Diese Dissertation ist auf den Internetseiten der Universitätsbiblio<br/>thek online verfügbar:  $\rm https://ub.tu-dortmund.de$

Bibliografische Information der Deutschen Nationalbibliothek Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte Daten sind im Internet über http://dnb.ddb.de abrufbar.

Die Informationen in diesem Buch wurden mit großer Sorgfalt erarbeitet. Dennoch können Fehler nicht vollständig ausgeschlossen werden. Der Autor übernimmt keine juristische Verantwortung oder damit verbundene Haftung für eventuell verbliebene fehlerhafte Angaben und deren Folgen.

Alle Rechte, auch die des auszugsweisen Nachdrucks, der Vervielfältigung und Verbreitung in besonderen Verfahren wie fotomechanischer Nachdruck, Fotokopie, Mikrokopie, elektronische Datenaufzeichnung einschließlich Speicherung und Übertragung auf weitere Datenträger sowie Übersetzung in andere Sprachen, behält sich der Autor vor.

# FABRICATION OF STEEP SLOPE CARBON NANOTUBE TRANSISTORS ON NOVEL MULTI-GATE SUBSTRATES

von der

Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität Dortmund

genehmigte

## DISSERTATION

zur Erlangung des akademischen Grades Doktor der Ingenieurswissenschaften (Dr.-Ing.)

vorgelegt von

Master of Science (M.Sc.) ALEXANDER BENJAMIN GUMPRICH aus Werne an der Lippe

Referent:Prof. Dr.-Ing. STEFAN TAPPERTZHOFENKorreferent:Prof. Dr. rer. nat. JOACHIM KNOCH

Tag der mündlichen Prüfung: 25.09.2023

### **Vorwort / Preface**

Die Neugier ist eine der wertvollsten Eigenschaften in der Wissenschaft. Sie hilft uns Dinge zu verstehen und auch die schwierigsten Probleme zu lösen. Sie war immer die treibende Kraft in meiner gesamten Zeit in der experimentellen Forschung. Meine Dissertation hätte ich jedoch niemals nur allein durch meine eigene Motivation heraus bewältigen können. Es sind zudem die zahlreichen Menschen, die mich während des Entstehens dieser Arbeit am Lehrstuhl für Mikro- und Nanoelektronik an der Technischen Universität Dortmund so wunderbar begleitet und gefördert haben.

Mein ganz besonderer Dank gilt hierbei Prof. Dr.-Ing Stefan Tappertzhofen für seine großartige Unterstützung, die kompetente sowie vertrauensvolle Betreuung, den stetigen Erfahrungsaustausch und natürlich die Möglichkeit mit ihm als Doktorvater zu promovieren.

Darüber hinaus bedanke ich mich herzlich bei Prof. Dr. rer. nat. Joachim Knoch für die langjährige Zusammenarbeit und die vielen wegweisenden Gespräche und Ratschläge. Zudem hat er dankenswerterweise das Koreferat für diese Arbeit übernommen.

Zutiefst dankbar bin ich außerdem dem leider viel zu früh verstorbenen Dr.-Ing Klaus Kallis. Mit tiefer Trauer und höchster Bewunderung für die aufopfernde Unterstützung, die er jedem einzelnem zukommen ließ, blicke ich stets auf die gemeinsame Zeit zurück.

Für die unvergessliche Zeit am Lehrstuhl für Intelligente Mikrosysteme und am Lehrstuhl für Mikro- und Nanoelektronik bin ich meinen Kolleginnen und Kollegen Raphael Ahlmann, Sarah Beck, Marion Brünninghaus-Willmes, Philipp Czyba, Evelyn Drabiniok, Sven Ebschke, Friederike Giebel, Karola Kolander, André Kosak, Marko Kremer, Julian Liedtke, Ulrike Lippe, Andre Löchte, Ashutosh Loyalka, Ulrich Marggraf, Dominik Merten, Remigius Poloczek, Pongsak Sarapukdee, Achim Wiggershaus und Jakob Zimmermann unendlich dankbar. Es ist ein großes Privileg mit solch kompetenten und liebenswürdigen Menschen zusammen zu arbeiten.

Einige Teile meiner Forschung konnte ich am Institut für Halbleitertechnik der RWTH in Aachen durchführen. Dafür möchte ich mich an dieser Stelle bei Thomas Grap, Thorben Frahm, Birgit Hadam, Stefan Scholz und Benjamin Richstein herzlich bedanken.

Im Rahmen der von mir betreuten Abschlussarbeiten am Lehrstuhl für Mikro- und Nanoelektronik, möchte ich mich ganz herzlich bei Sarah Beck,

André Lauff, Julian Liedtke, Finja Münchenberger, Torben Pacholleck, und Danting Feng für ihr Beitragen, ihre Unterstützung und ihre tollen Ideen bedanken.

Auch meinem Mentor und Wegbereiter Marcel René Müller bin ich einen sehr besonderen Dank schuldig. Ich hätte ohne ihn niemals meine Reise in die Welt der Halbleiterphysik angetreten. Danke für die einzigartige Betreuung, die großartige Zusammenarbeit und das an mich weitergegebene Wissen.

Zu guter Letzt danke ich von Herzen meiner wundervollen Anita, meinen Freunden und meiner Familie, insbesondere meinen Geschwistern und meinen Eltern für ihren niemals endenden und unentbehrlichen Rückhalt.

Danke Euch Allen!

Dortmund, im September 2023 Alexander Gumprich

## Contents

| G             | lossa | $\mathbf{ry}$ |                                             | xi        |

|---------------|-------|---------------|---------------------------------------------|-----------|

| $\mathbf{Li}$ | st of | ' Figur       | res                                         | xv        |

| $\mathbf{Li}$ | st of | <b>Table</b>  | s                                           | xvii      |

| 1             | Inti  | roduct        | ion                                         | 1         |

| <b>2</b>      | Fun   | idamei        | ntals of Nanoscale Transistors              | 5         |

|               | 2.1   | The N         | MOSFET                                      | . 6       |

|               |       | 2.1.1         | Ideal Working Principle                     | . 6       |

|               |       | 2.1.2         | Limitations and non-ideal Characteristics   | . 9       |

|               |       | 2.1.3         | Impact of Short Channel Geometries          | . 12      |

|               | 2.2   | Novel         | Transistor Technologies                     | . 14      |

|               |       | 2.2.1         | Tunnel FETs                                 | . 15      |

|               |       | 2.2.2         | Energy Filtering FETs                       | . 19      |

|               |       | 2.2.3         | One-Dimensional Channel Geometries          | . 21      |

|               |       | 2.2.4         | Alternative Channel Materials               | . 22      |

| 3             | Car   | bon N         | Janotubes                                   | <b>25</b> |

|               | 3.1   | Funda         | amentals of Carbon Nanotubes                | . 26      |

|               |       | 3.1.1         | Structural Properties                       | . 26      |

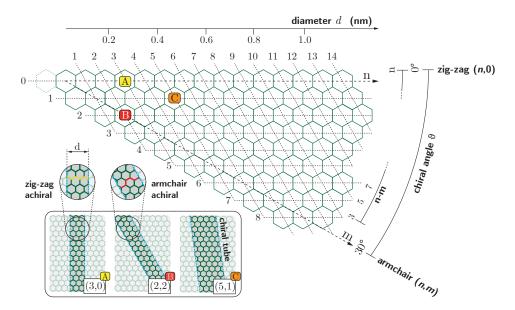

|               |       | 3.1.2         | Configurations and Chirality                | . 27      |

|               |       | 3.1.3         | Electronic Behavior Near the Fermi Level    | . 29      |

|               | 3.2   | The S         | Schottky Barrier at the CNT-Metal Interface | . 33      |

|               | 3.3   | Large         | Scale Synthesis                             | . 35      |

|               |       | 3.3.1         | Synthesis via CVD Processes                 | . 36      |

|               |       | 3.3.2         | Selective Growth Mechanisms                 | . 37      |

|               |       | 3.3.3         | Extraction and Purification                 | . 40      |

| 4             | Exp   | oerime        | ental Methodology                           | 43        |

|               | 4.1   | Depos         | sition Methods                              | . 44      |

|               |       | 4.1.1         | Thermal Evaporation                         | . 44      |

|               |       | 4.1.2         | Sputtering                                  | . 45      |

|               |       | 4.1.3         | Plasma Enhanced Chemical Vapor Deposition   | . 46      |

|               | 4.2   | Lithog        | graphy Processes                            | . 47      |

|               |       | 4.2.1         | Optical Lithography                         | . 47      |

|               |       | 4.2.2         | Electron Beam Lithography                   | . 48      |

|               | 4.3   | Electr        | rical Characterization                      |           |

| <b>5</b>     | Inti  | roducing Buried Gate Architectures                            | 51  |

|--------------|-------|---------------------------------------------------------------|-----|

|              | 5.1   | The Buried Triple Gate Substrates                             | 52  |

|              |       | 5.1.1 Design and Simulation of the new BTGs                   | 54  |

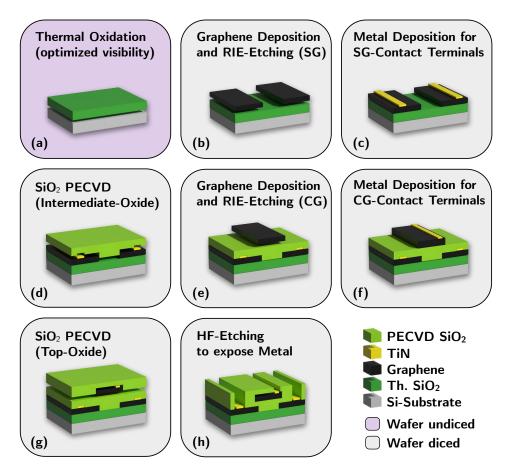

|              |       | 5.1.2 Fabrication of Triple Graphene Substrates               | 59  |

|              |       | 5.1.3 Fabrication of Graphene/Metal Heterostructures $\ldots$ | 61  |

|              |       | 5.1.4 Graphene Transfer from Copper                           | 63  |

|              |       | 5.1.5 Optimizing the Visibility of Graphene                   | 65  |

|              |       | 5.1.6 Optimizing the Oxide Deposition                         | 72  |

|              |       | 5.1.7 Substrate Analysis                                      | 74  |

|              | 5.2   | The Buried Multi Gate Substrates                              | 80  |

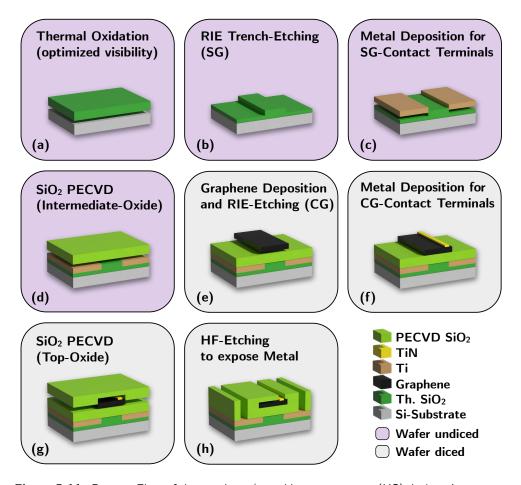

|              |       | 5.2.1 Substrate Fabrication                                   | 80  |

|              |       | 5.2.2 Substrate Analysis                                      | 82  |

| 6            | Fab   | rication of Carbon Nanotube Transistors                       | 85  |

|              | 6.1   | CNT Surface Application                                       | 86  |

|              |       | 6.1.1 Dielectrophoretic Alignment                             | 87  |

|              | 6.2   | E-beam Fabrication                                            | 90  |

|              |       | 6.2.1 Overlay Patterning                                      | 90  |

|              |       | 6.2.2 CSAR62 for Improved Lift-Off Conditions                 | 92  |

|              |       | 6.2.3 Fabrication of Alignment Marks and Contact Windows      | 95  |

|              |       | 6.2.4 Fabrication of Contact Terminals                        | 98  |

| 7            | Ele   | ctrical Measurements                                          | 103 |

|              | 7.1   | Measurement Setup                                             | 104 |

|              | 7.2   | Characterization of Schottky-Barrier-CNTFETs                  | 104 |

|              | 7.3   | Characterization of Tunnel-CNTFETs                            | 106 |

|              | 7.4   | Characterization of Energy Filtering CNTFETs                  | 109 |

| 8            | Cor   | nclusions                                                     | 113 |

|              | 8.1   | Summary                                                       | 114 |

|              | 8.2   | Outlook                                                       | 116 |

| 9            | Ap    | pendix                                                        | 119 |

|              | 9.1   | Process Specifications for the new BTG Substrates             | 120 |

|              | 9.2   | Process Specifications for the BMG Substrates                 | 122 |

|              | 9.3   | Process Recipes                                               | 122 |

|              | 9.4   | Extended WCD+ Simulations                                     | 125 |

|              | 9.5   | Miscellaneous                                                 | 126 |

| $\mathbf{R}$ | efere | ences                                                         | 129 |

| P            | ıblic | ations, Talks and Poster Contributions                        | 145 |

## Glossary (List of Acronyms)

| AFM       | Atomic Force Microscopy                                                 |

|-----------|-------------------------------------------------------------------------|

| ALD       | Atomic Layer Deposition                                                 |

| BJT       | Bipolar Junction Transistor                                             |

| BMG       | Buried Multi Gates                                                      |

| BTBT      | Band-to-band Tunneling                                                  |

| BTG       | Buried Triple Gates                                                     |

| CAD       | Computer Aided Drawing                                                  |

| CG        | Center Gate                                                             |

| CIE       | Commission Internationale De L'Éclairage                                |

| CMP       | Chemical Mechanical Polishing                                           |

| CNT       | Carbon Nanotube                                                         |

| CNTFET    | Carbon Nanotube Field Effect Transistor                                 |

| CSAR      | $Poly(\alpha$ -Methyl Styrene-Co- $\alpha$ -Chloroacrylate Methylester) |

| CVD       | Chemical Vapor Deposition                                               |

| DEP       | Dielectrophoresis                                                       |

| DIBL      | Drain Induced Barrier Lowering                                          |

| DI-Water  | De-Ionized Water                                                        |

| DSG       | Drain Side Gate                                                         |

| EBL       | Electron Beam Lithography                                               |

| eDIPS     | Enhanced Direct Injection pyrolytic Synthesis                           |

| EDX       | Energy-dispersive X-ray Spectroscopy                                    |

| EF-FET    | Energy Filtering Field Effect Transistor                                |

| FEM       | Finite Elements Method                                                  |

| HS        | Heterostructure                                                         |

| IC        | Integrated Circuit                                                      |

| IPA       | Isopropyl Alcohol                                                       |

| IRDS      | International Roadmap for Devices and Systems                           |

| LOCOS     | Local Oxidation Of Silicon                                              |

| MOSFET    | Metal Oxide Semiconductor Field Effect Transistor                       |

| MWCNT     | Multi-walled Carbon Nanotube                                            |

| NW        | Nanowire                                                                |

| OM        | Optical Microscope                                                      |

| PECVD     | Plasma Enhanced Chemical Vapor Deposition                               |

| PMMA      | Poly(Methyl Methacrylate)                                               |

| PVD       | Physical Vapor Deposition                                               |

| RIE       | Reactive Ion Etching                                                    |

| rPECVD    | Remote Plasma Enhanced Chemical Vapor Deposition                        |

| S/D       | Source/Drain                                                            |

| SB-MOSFET | Schottky Barrier Metal Oxide Semiconductor Field Effect Transistor      |

| SEM       | Scanning Electron Microscope                                            |

| SOI       | Silicon-on-insulator                                                    |

| SSG       | Source Side Gate                                                        |

| SST       | Steep Slope Transistor                                                  |

|           |                                                                         |

| SWCNT      | Single-walled Carbon Nanotube                  |

|------------|------------------------------------------------|

| TEM        | Transmission Electron Microscope               |

| TFET       | Tunnel Field Effect Transistor                 |

| TG         | Triple Graphene                                |

| TGA        | Thermo Gravimetric Analysis                    |

| TMAH       | Tetramethylammonium Hydroxide                  |

| TMD        | Transition Metal Dichalcogenide                |

| UV-vis-NIR | Ultraviolet Visible Near-infrared Spectroscopy |

| VLS        | Vapor-Liquid-Solid                             |

| VLSI       | Very Large Scale Integration                   |

| VSS        | Vapor-Solid-Solid                              |

| WCD        | Weighted Color Difference                      |

| WF         | Writefield                                     |

| WKB        | Wentzel-Kramers-Brillouin (approximation)      |

## Glossary (List of Molecular Formulae)

| Al                | Aluminum                  |

|-------------------|---------------------------|

| $Al_2O_3$         | Aluminum Oxide            |

| AlGaAs            | Aluminum Gallium Arsenide |

| Au                | Gold                      |

| $C_2H_2$          | Acetylene                 |

| $C_2H_4$          | Ethylene                  |

| $C_2H_6O$         | Ethanol                   |

| $CH_4$            | Methane                   |

| CO                | Carbon Monoxide           |

| FeCl <sub>3</sub> | Iron(III) Chloride        |

| GaAs              | Gallium Arsenide          |

| $H_2SO_4$         | Sulfuric Acid             |

| h-BN              | Hexagonal Boron Nitride   |

| HF                | Hydrofluoric Acid         |

| $HNO_3$           | Nitric Acid               |

| InAs              | Indium Arsenide           |

| $MoS_2$           | Molybdenum Disulfide      |

| $MoSe_2$          | Molybdenum Diselenide     |

| Si                | Silicon                   |

| $SiO_2$           | Silicon Dioxide           |

| Ti                | Titanium                  |

| TiN               | Titanium Nitride          |

| $WO_3$            | Tungsten Oxide            |

| $WS_2$            | Tungsten Disulfide        |

| $WSe_2$           | Tungsten Diselenide       |

|                   |                           |

## List of Figures

| 2.1  | Schematics of the <i>n</i> -channel MOSFET                                                  |  | • | . 6  |  |

|------|---------------------------------------------------------------------------------------------|--|---|------|--|

| 2.2  | Conduction band of the <i>n</i> -channel MOSFET $\ldots$                                    |  |   | . 7  |  |

| 2.3  | MOSFET I-V characteristic                                                                   |  |   | . 8  |  |

| 2.4  | Effective channel potential                                                                 |  |   | . 10 |  |

| 2.5  | Drain induced barrier lowering                                                              |  |   |      |  |

| 2.6  | SST Boltzmann Filter                                                                        |  |   | . 15 |  |

| 2.7  | TFET band configuration                                                                     |  |   | . 17 |  |

| 2.8  | TFET band structure for different source doping profiles                                    |  |   | . 18 |  |

| 2.9  | Conduction band of an EF-FET                                                                |  |   | . 20 |  |

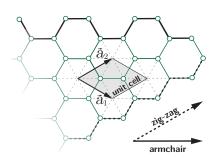

| 3.1  | Unit vectors of graphene                                                                    |  |   | . 26 |  |

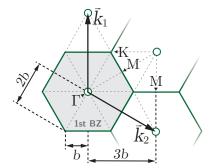

| 3.2  | Brillouin zone of graphene                                                                  |  |   | . 27 |  |

| 3.3  | Chirality pattern                                                                           |  |   | . 28 |  |

| 3.4  | 2D-dispersion relataion of graphene                                                         |  |   | . 29 |  |

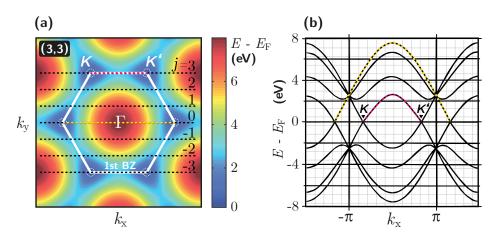

| 3.5  | Dispersion relation for a $(3,3)$ -CNT                                                      |  |   | . 30 |  |

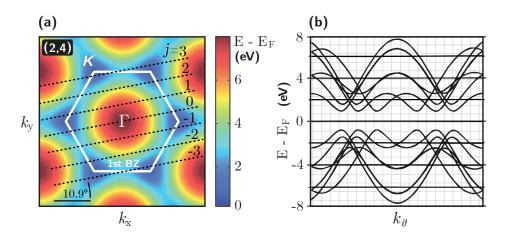

| 3.6  | Dispersion relation for a $(2, 4)$ -CNT                                                     |  |   | . 31 |  |

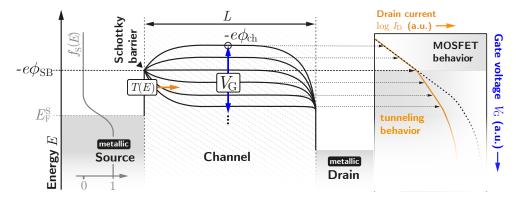

| 3.7  | Conduction band of the SB-MOSFET                                                            |  |   | . 35 |  |

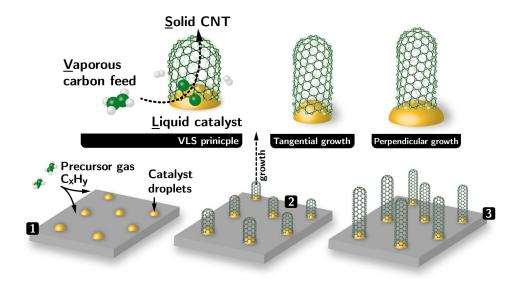

| 3.8  | CVD-VLS process to grow SWCNTs                                                              |  |   | . 36 |  |

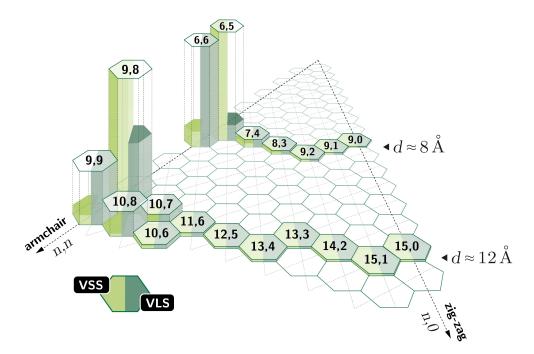

| 3.9  | Simulated chirality distribution                                                            |  |   | . 38 |  |

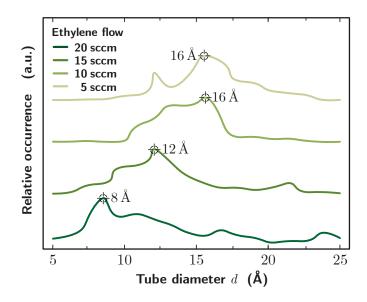

| 3.10 | Influence of ethylene flow                                                                  |  |   | . 40 |  |

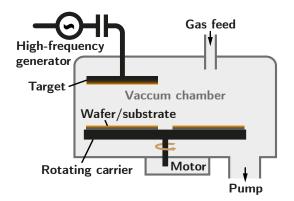

| 4.1  | Sketched layout of a sputtering system                                                      |  |   | . 45 |  |

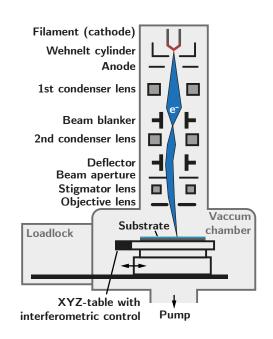

| 4.2  | Sketched layout of an e-beam system                                                         |  |   |      |  |

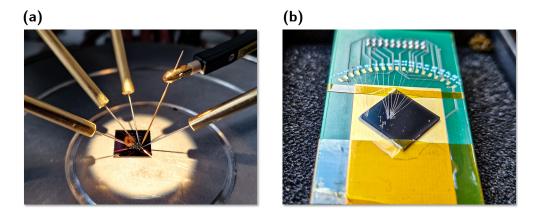

| 4.3  | Measurement setups                                                                          |  |   | . 49 |  |

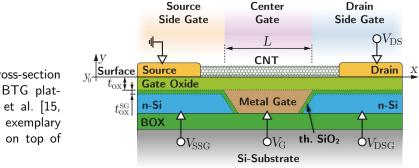

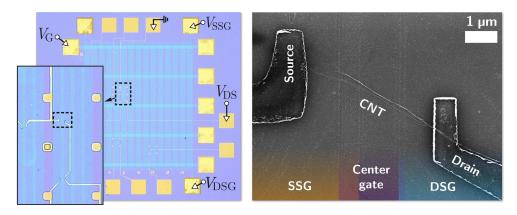

| 5.1  | Original BTG platform by Müller et al                                                       |  |   | . 52 |  |

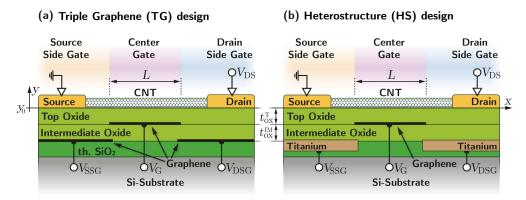

| 5.2  | New BTG platform (TG, HS)                                                                   |  |   | . 53 |  |

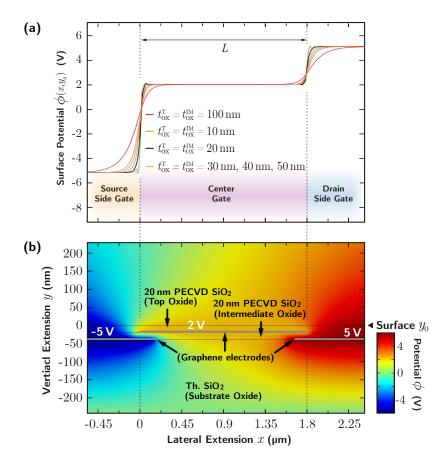

| 5.3  | Surface Potential - new BTG                                                                 |  |   | . 54 |  |

| 5.4  | Surface Potential and Alignment Gap - new BTG                                               |  |   | . 55 |  |

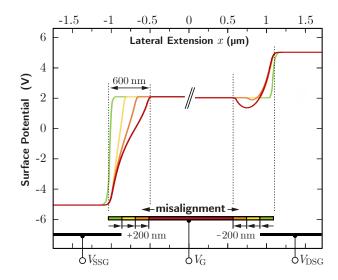

| 5.5  | Surface Potential - new and old BTG                                                         |  |   | . 56 |  |

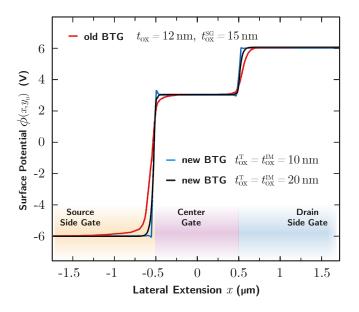

| 5.6  | Potential drop of the old BTG                                                               |  |   | . 57 |  |

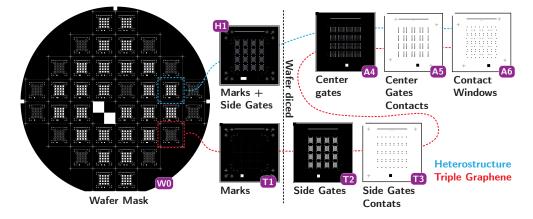

| 5.7  | UV-lithography mask layout of a BTG cell                                                    |  |   | . 58 |  |

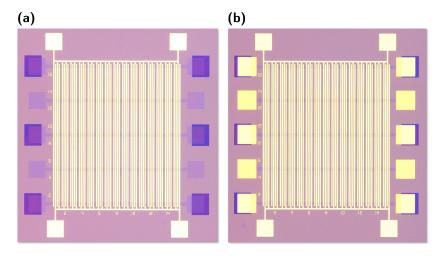

| 5.8  | Process flow of the new BTG (TG)                                                            |  | • | . 59 |  |

| 5.9  | Microscopy image of the new BTGs (TG) $\ldots \ldots \ldots$                                |  |   | . 60 |  |

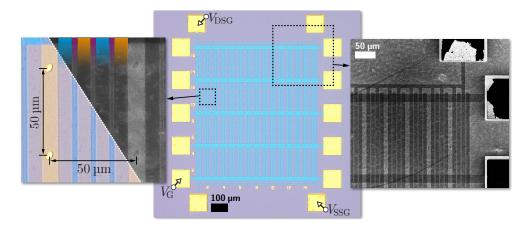

| 5.10 | Microscopy image of the new BTG (HS) $\ldots$                                               |  |   | . 61 |  |

| 5.11 | Process Flow of the new BTG (HS)                                                            |  | • | . 62 |  |

|      | 4-inch wafer before dicing $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ |  |   |      |  |

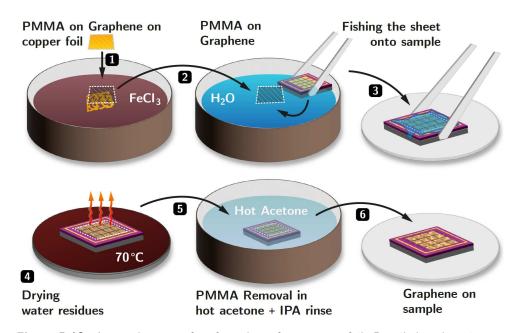

| 5.13 | A complete transfer of graphene from copper foil $\ . \ . \ .$ .                            |  | • | . 64 |  |

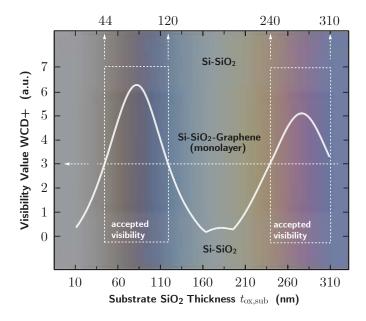

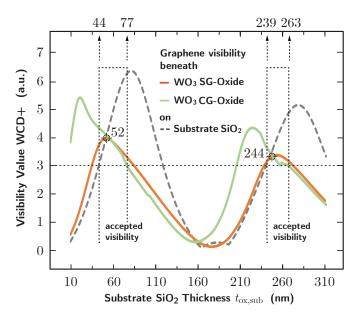

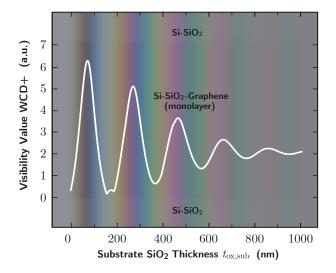

| 5.14 | WCD+ for a graphene monolayer on $\mathrm{Si}/\mathrm{SiO}_2$                               |  | • | . 68 |  |

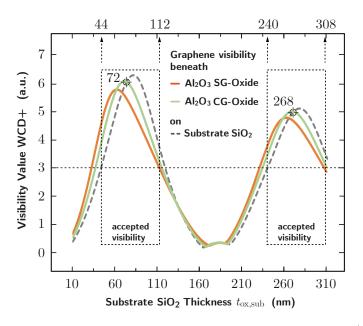

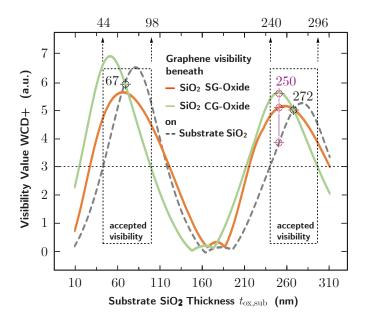

| 5.15 | WCD+ for a graphene monolayer and $\rm Si/SiO_2/Al_2O_3~$                                   |  | • | . 69 |  |

| 5.16 | WCD+ for a graphene monolayer and $\rm Si/SiO_2/WO_3~\ldots$ .                              |  |   | . 70 |  |

| 5.17 | WCD+ for a graphene monolayer and $\rm Si/SiO_2/PECVD\text{-}SiO_2$                         |  | • | . 71 |  |

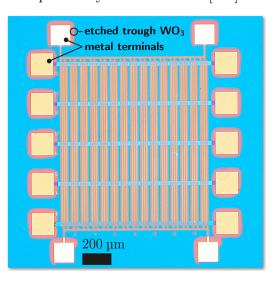

| 5.18 | Heterostructure with $WO_3 \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$         |  | • | . 72 |  |

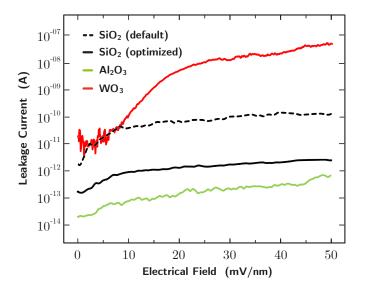

| 5.19 | Comparison of electrical integrity for different oxides $\ . \ . \ .$                       |  | • | . 73 |  |

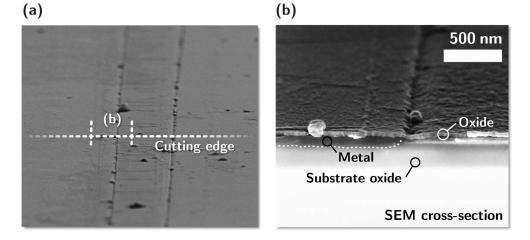

| 5.20 | SEM cross-section of the transition to a side gate                                          |  |   | . 74 |  |

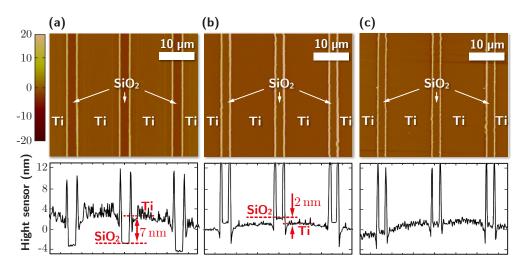

| 5.21 | AFM measurement of the heterostructure                    | 75  |

|------|-----------------------------------------------------------|-----|

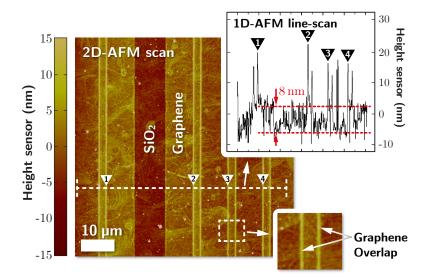

| 5.22 | AFM measurement of the triple graphene platform           | 76  |

| 5.23 | Valuation of the alignment precision after UV-lithography | 77  |

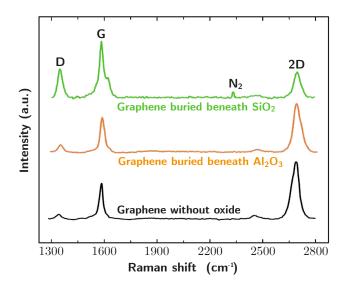

| 5.24 | Raman spectra of the transferred graphene                 | 78  |

| 5.25 | Double contact pads for the BTG heterostructure           | 79  |

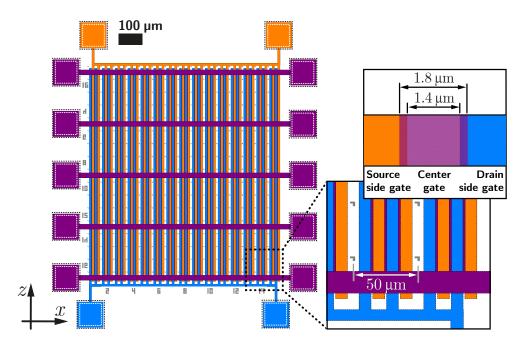

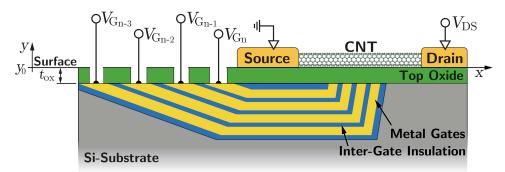

| 5.26 | The buried multi gate architecture schematics             | 80  |

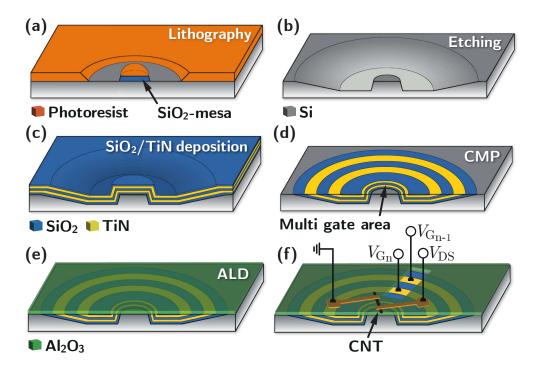

| 5.27 | Fabrication process of the BMG substrate                  | 81  |

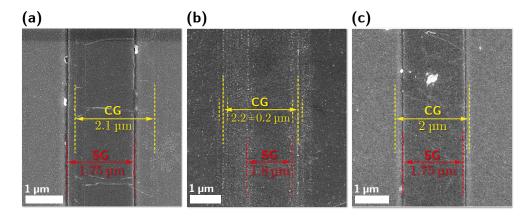

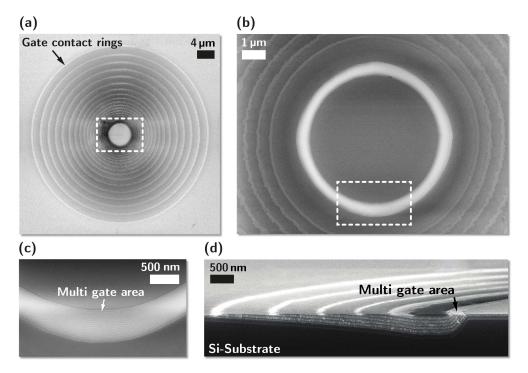

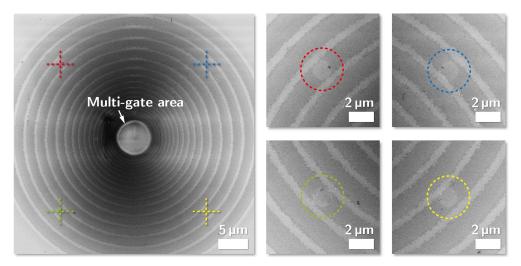

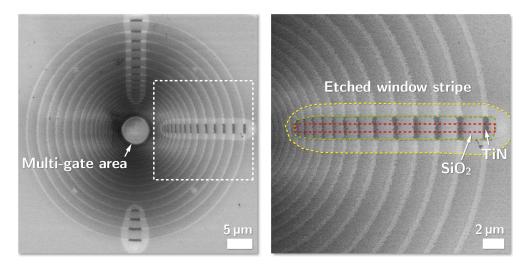

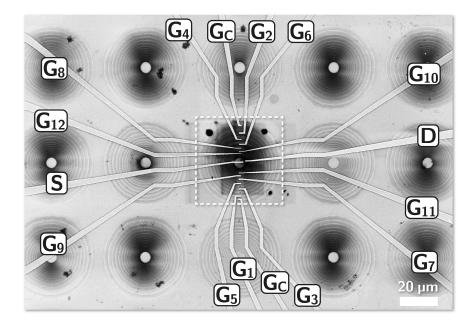

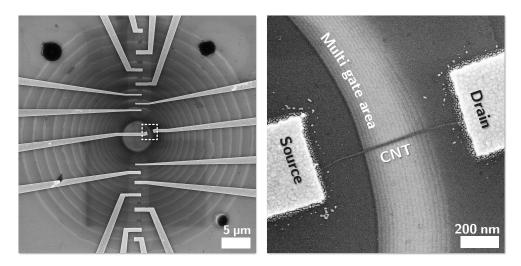

| 5.28 | SEM micrographs of a BMG substrate                        | 82  |

| 5.29 | AFM analysis of the BMG substrate                         | 83  |

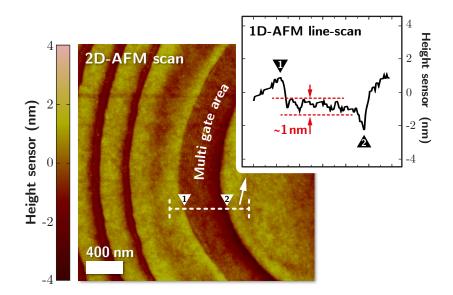

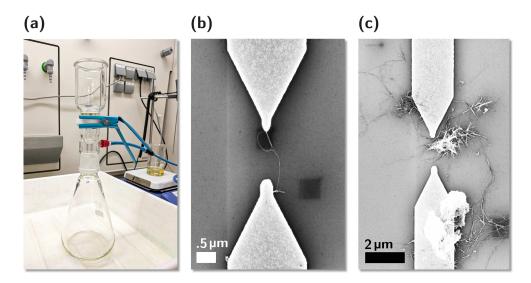

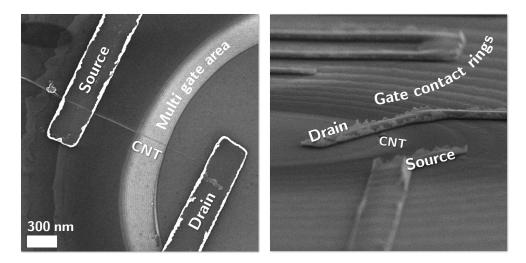

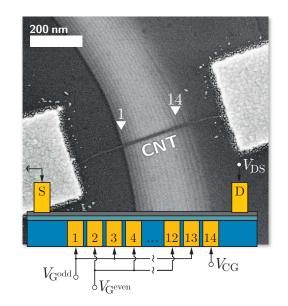

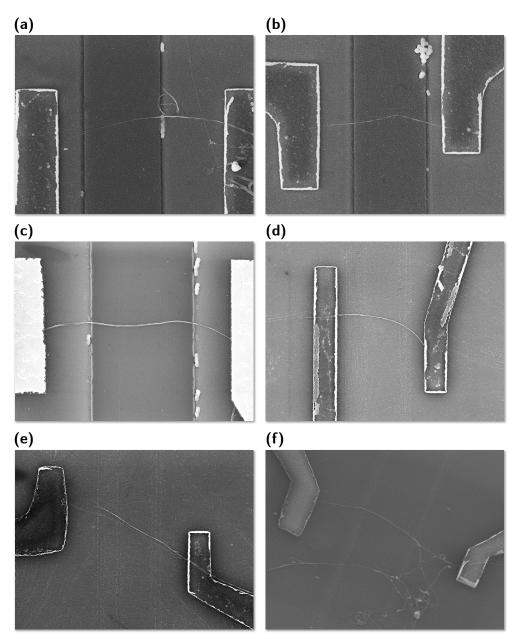

| 6.1  | BMG- and BTG-SEM micrographs of an aligned CNT            | 87  |

| 6.2  | SEM micrographs of InAs-nanowires after DEP experiments   | 88  |

| 6.3  | SEM micrographs of CNTs after DEP experiments             | 89  |

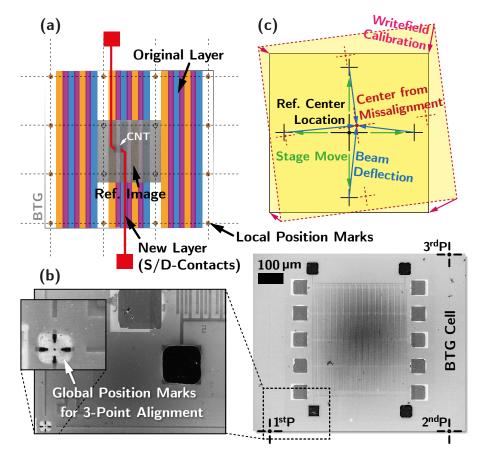

| 6.4  | Overlay EBL lithography                                   | 91  |

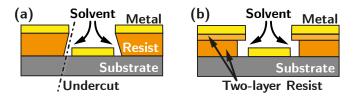

| 6.5  | Lift-Off Process for one- and two-layer resist            | 93  |

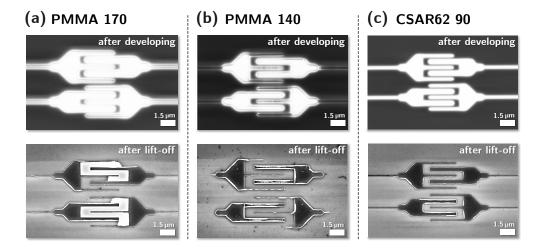

| 6.6  | EBL lithography resist comparison                         | 94  |

| 6.7  | BMG cell after alignment mark fabrication                 | 96  |

| 6.8  | BMG cell after contact window fabrication                 | 97  |

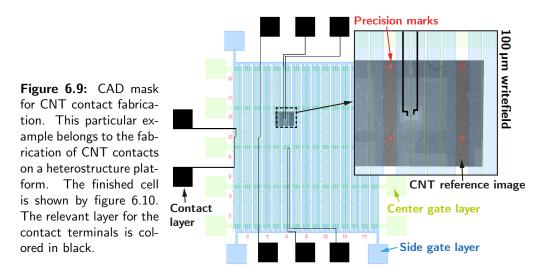

| 6.9  | CAD mask for CNT contact fabrication                      | 98  |

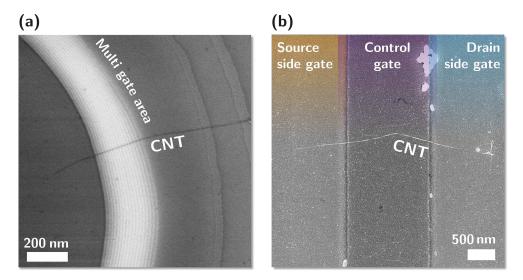

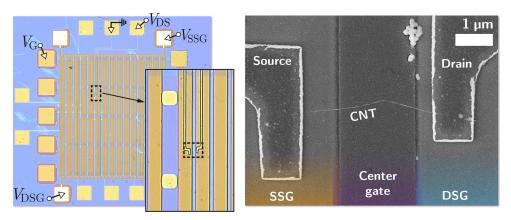

| 6.10 | BTG heterostructure with CNT contact terminals            | 99  |

| 6.11 | BTG triple graphene substrate with CNT contact terminals  | 99  |

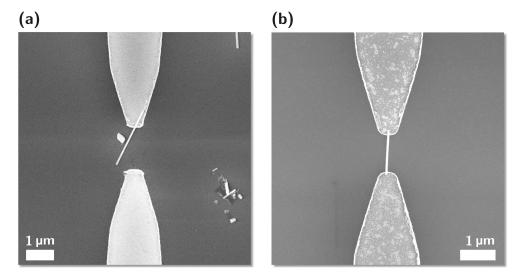

| 6.12 | SEM micrograph of the BMG with a completed CNT device     | 100 |

| 6.13 | SEM micrographs of the BMG with a completed CNT device    | 101 |

| 6.14 | Close-up of a completed CNT device on the BMGs            | 101 |

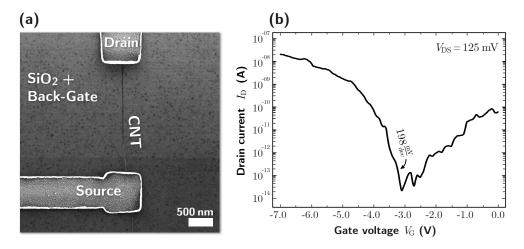

| 7.1  | Exemplary back-gate CNTFET                                | 104 |

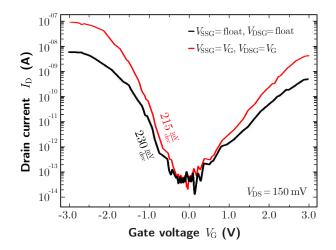

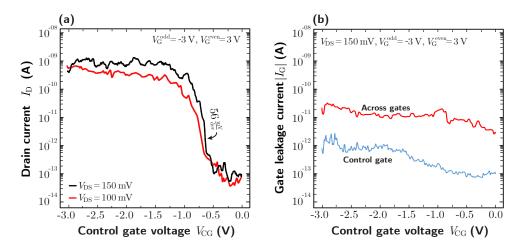

| 7.2  | SB-CNTFET transfer characteristic                         | 106 |

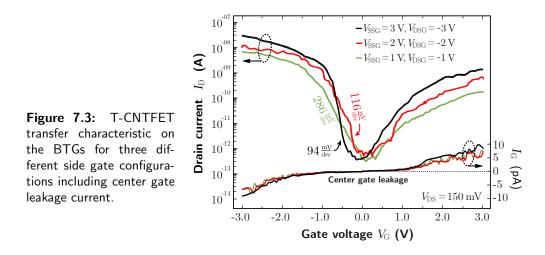

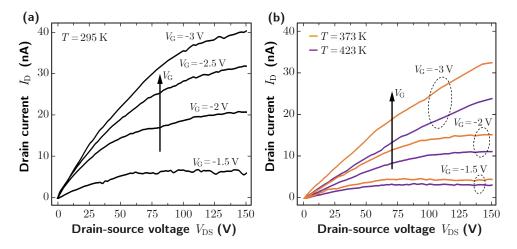

| 7.3  | T-CNTFET transfer characteristic                          | 106 |

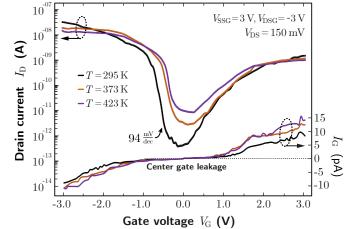

| 7.4  | T-CNTFET transfer characteristic at diff. temperatures    | 107 |

| 7.5  | T-CNTFET output characteristic at diff. temperatures      | 108 |

| 7.6  | EF-CNTFET interconnections on the BMG platform            | 109 |

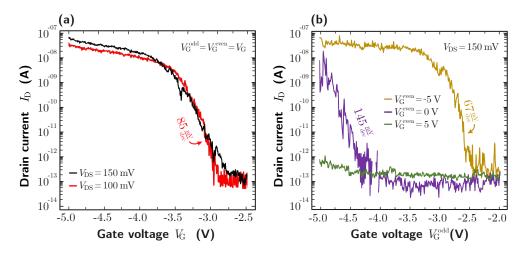

| 7.7  | BMG EF-CNTFET characteristics                             | 110 |

| 7.8  | BMG CNTFET characteristics w/o energy filtering           | 111 |

| 9.1  | Mask Layout UV-Lithography                                | 120 |

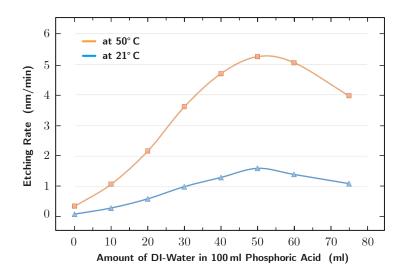

| 9.2  | Etching rates of aluminum oxide                           | 124 |

| 9.3  | Extended WCD+ simulations                                 | 125 |

| 9.4  | Completed CNTFET devices on the BTG platform              | 126 |

| 9.5  | Completed CNTFET devices on the BMG platform              | 127 |

|      |                                                           |     |

## List of Tables

| 2.1 | Alternative channel materials overview                                    | 23 |

|-----|---------------------------------------------------------------------------|----|

| 3.1 | Electrical properties of selected CNTs                                    | 33 |

| 3.2 | Temperature affecting CNT diameters                                       | 39 |

| 3.3 | Comparison of purification assessment tools                               | 41 |

| 5.1 | WCD+ values for 2D materials on the new BTG $\ldots \ldots \ldots \ldots$ | 71 |

# Chapter I Introduction

The assimilation of electronic circuits into every day life has been shaping modern civilization for many decades. From cars to refrigerators, from dishwashers to smartphones; today, almost everything is electronically enhanced and controlled. Naturally, this technological development did not appear over night. Instead, it is the result of an evolution that has been going on for nearly a century now. The idea to create logic gates from electrical switches is the fundamental base of computing in any manifestation. Although already invented in the 1920s, the field effect transistor had to surrender to electron tubes since actual manufacturing of transistors was not feasible at the time. Electron tubes managed to be used as the switch needed for logic gates for many years until, finally, in 1947 the bipolar junction transistor was invented. From there, the electronic evolution accelerated and instead of bulky tubes, extremely small semiconducting devices took over. Integrated circuits (ICs) containing thousands of transistors became the heart

of electronic computing. Almost two decades later, the field effect transistor eventually made its appearance as a device called the MOSFET which stands for metal-oxide-semiconductor field-effect transistor. The working principle of MOSFETs was the key to integrated low-power complementary logic called CMOS technology. In 1965, it was Gordon Moore, a co-founder of Intel Cooperation, who asserted that the density of transistors in integrated circuits will double every two years, which is commonly known as Moore's Law [1]. His famous prediction turned out to be astonishingly accurate and integration density in modern ICs surpassed  $10^{10}$  transistors/cm<sup>2</sup> as of This was possible due to one specific measure: Scaling the today [2]. geometry of the transistor and the supply voltage by a factor of  $1/\alpha$  leads to a higher density of transistors proportional to  $\alpha^2$  and an increase of computing speed proportional to  $\alpha$  while the power consumption stays constant. In the meantime, the semiconductor industry has grown in sales from \$1 billion in 1970 to \$20 billion in 1984 and to \$439 billion in 2020 [3]. Over the years, this long-term scaling reached tremendous difficulties due to quantum mechanical and short channel effects, such as drain induced barrier lowering [4]. One approach to mitigate these effects are FinFET devices [5], which were successfully scaled down in the sub 22 nm regime. As of 2022, leading semiconductor companies like IBM introduced 2nm technology nodes, with typical gate lengths of 14 nm and a 44 nm pitch, extensively pushing the limits for Moore's law. According to the International Roadmap for Devices and Systems (IRDS) the MOSFET has fully reached its limitations [6]. As a replacement for the MOSFET and for silicon based technology in general, the IRDS proposes a number of emerging research devices, such as spin based atomic switches and III-V semiconductor based transistors.

For several years now, the demand for mobile applications has significantly increased and has shifted transistor development towards a point where minimizing power dissipation is more important than maximizing performance. A simple solution is, of course, the further reduction of the supply voltage. However, bound to approximately 1 V in minimum supply voltage due to its limited inverse subthreshold slope, that is 60 mV/dec, the conventional MOSFET is rendered unfit for future demands in any aspect. In fact, every device which relies on injecting carriers from the thermally broadened Fermi distribution is bound by this so-called thermionic limit. Consequently, novel and redesigned low power devices are subject to industrial and academic research. Here, the key challenge is to maintain sufficient electrostatic gate control for small gate lengths while decreasing the power. The solution is to redesign device architecture inasmuch that the channel material and geometry are fundamentally different from state of the

art transistors [7–9]. Materials like nanowires (NWs) and carbon nanotubes (CNTs) exhibit extraordinary properties and offer new design opportunities [9–11]. These one-dimensional materials enable excellent gate control and extreme scalability. Examples of novel low power devices include steep slope transistors (SSTs), such as tunneling field effect transistors (TFETs) and superlattice energy-filtering transistors (EF-FETs) [12–18].

With awareness of the imminent end of Moore's law, the present thesis addresses the fabrication and characterization of TFET and EF-FET devices using CNTs. Since the operation of such transistors demands very different requirements than MOSFETs, the fabrication process is fundamentally different as well. For instance, a dynamic electrostatic doping landscape is required which becomes feasible by burying multiple gate electrodes into a substrate covered by a dielectric. The fabrication of such substrates is also part of this thesis. The so-called buried triple gate (BTG) architecture uses individually addressable and mutually insulated graphene films as integrated gate electrodes separated by an intermediate dielectric. In another variation a BTG heterostructure - a combination of thin metal layers and graphene films is deployed. As the name is suggesting, the presented BTG platform only provides three gate electrodes in order to fabricate TFET devices. However, the mentioned EF-FET is based on energy filtering through periodic potentials. Thus, an entire set of electrodes in close proximity is necessary in order to generate this potential pattern. On buried multi gate (BMG) substrates, provided by Thomas Grap of RWTH Aachen University, EF-FETs with carbon nanotubes were manufactured.

### Outline

Apart from introduction and summary, the thesis is divided into six main chapters: Chapter II introduces the fundamentals of transistors, from MOS-FET technology towards SSTs. Since only CNTs are used for the devices fabricated in this work, chapter III is dedicated entirely to their electrical and structural properties. Besides, the chapter elaborates the synthesis of CNTs and discusses Schottky-barriers at the interfaces. An overview of methodology for the fabrication process is given by chapter IV. Thereafter, the BTG and BMG platforms are introduced in chapter V. Including details about the design, manufacturing, assessment and finite element simulations of the architectures. The presented devices are completed after CNT deposition and the fabrication of contact terminals which is discussed in chapter VI. Finally, chapter VII reports on electrical measurements of the devices to ascertain their characteristics with regard to subthreshold slope and on-/off-currents.

# Chapter II

## Fundamentals of Nanoscale Transistors

$\mathbf{I}^{\mathrm{N}}$  order to understand steep slope nanoscale transistor research, the fundamentals of MOSFET devices should be discussed beforehand. The <u>metal-oxide-semiconductor field-effect transisitor</u> is the best example to show how transistors work and why improvement was feasible. Modern MOSFET architectures have been scaled down to a remarkable extent within only a few nanometers. In this chapter the basic working principle of the MOSFET will be introduced, as well as its properties and limits for modern computing. In addition, this chapter goes beyond MOSFET technologies, presenting alternatives and new developments concerning steep slope transistors and alternative channel materials.

### 2.1 The MOSFET

Since manufactured for the first time in the 1960s, the MOSFET has become the most commonly produced electronic device ever in history [19]. Simple in structure and inexpensive in production, it can be easily arranged in a complementary architecture. With all that, the MOSFET has a huge advantage over the bipolar junction transistor (BJT) which was state of the art at the time.<sup>1</sup> Progress in research and development eventually made it possible to implement the very large scale integration (VLSI), the foundation of modern electronics. For example, latest high-end microprocessors contain up to 114 billion MOSFETs on a single chip produced within a 5 nm technology node for very short channel lengths [2]. However, to explain how the MOSFET works, it is easier to focus on long channel devices first. Afterwards, section 2.1.3 describes how characteristics change if the channel length is reduced.

### 2.1.1 Ideal Working Principle

In microprocessors the MOSFET is generally used as a switch, thus being the building block of any logic circuit. In contrast to the BJT, the MOSFET's distinguished feature is the MOS capacitor, which controls the carrier transport. Thus, apart from the displacement current there is no secondary current necessary in order to control the primary current. Instead, the MOSFET can be switched on only by applying a gate voltage causing the capacitor to charge. Eventually, the resulting electric field manipulates a doped channel region at the substrate's surface [20]. For the sake of simplicity, in this section only the *n*-channel MOSFET will be explained as shown in Figure 2.1.

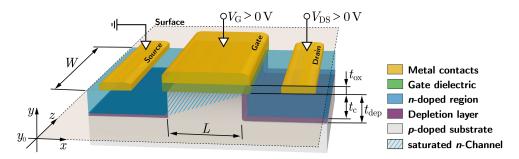

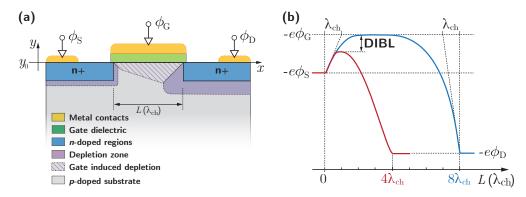

**Figure 2.1:** Schematics of the *n*-channel MOSFET: *L* is the channel length and *W* is the channel width. The thickness of the gate dielectric is given by  $t_{ox}$ . The full thickness of the channel is given by  $t_{ch}$ . Disregarding the depletion layer,  $t_c$  fits the depth of the *n*-region.  $V_G$  and  $V_{DS}$  relates to the source terminal which is usually grounded and/or connected to the bulk substrate.

<sup>&</sup>lt;sup>1</sup>Although the idea of field effect transistors is actually older, the BJT was the first to replace electron tubes since production of the MOSFET was not feasible at the time.

The highly n-doped source and drain regions are blue colored in the figure. Inbetween is a weakly *p*-doped channel region (colored in light gray), thus forming pn-junctions to source and drain. The gate electrode at the top of the channel is insulated by the gate dielectric. Applying a positive gate voltage  $V_{\rm G}$  creates an electrical field in y-direction moving both valence and conduction band towards source level. Therefore, a depletion of positive charge carriers occurs at the *p*-doped channel surface. Constantly increasing the gate voltage  $V_{\rm G}$  and going above the threshold voltage  $V_{\rm th}$ , moves the conduction band closer and the valence band further apart to the Fermi level. This reduces the barrier for negative charge carriers in the *n*-regions and leads to the injection of carriers into the channel in such a way that electrons now become majority carriers underneath the gate. An additional sufficiently high voltage  $V_{\rm DS}$  between the source and drain region will move the Fermi level at the drain  $E_{\rm F}^{\rm D}$  far away from the Fermi level at source  $E_{\rm F}^{\rm S}$ . The probability for electrons occupying free states in the channel increases drastically. Now, charge carrier transport from source to drain eventually emerges in x-direction. Figure 2.2 shows the band structure depending on the gate and drain-source voltage in an ideal scenario. The characteristics can be best described by the so-called Gradual Channel Approximation [21]: Initially, when the drain-source voltage  $V_{\rm DS}$  is lower than  $V_{\rm G} - V_{\rm th}$ , the drain current almost increases linearly within the first half of a parabola given by

$$I_{\rm D} = \mu_{\rm eff} C_{\rm ox} \frac{W}{L} \left[ (V_{\rm G} - V_{\rm th}) V_{\rm DS} - \frac{V_{\rm DS}^2}{2} \right] \quad {}^{\rm for \ V_{\rm G}}_{\rm (linear \ regime)} [3].$$

(2.1)

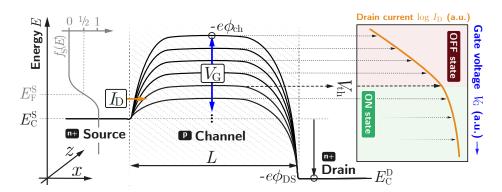

**Figure 2.2:** Illustration of the ideal *n*-channel MOSFET's conduction band as a function of  $V_{\rm G}$  with static  $V_{\rm DS}$  [22]: Initially, the high barrier of the *p*-channel does not allow any carrier transport from source to drain. The conduction band (same applies to the valence band) bends down by applying a gate voltage  $V_{\rm G}$  lowering the barrier. Exceeding  $(V_{\rm G} > V_{\rm th})$  leads to carrier injection from source into the channel. By applying a sufficiently high drain-source voltage  $V_{\rm DS}$ , carriers eventually flow from source to drain. Note that the band structure refers to ideal conditions at the interface between channel and gate oxide.

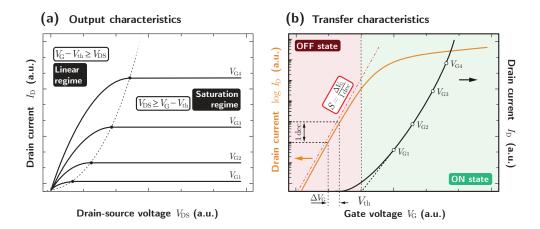

Besides the already known parameters, equation 2.1 contains the effective carrier mobility  $\mu_{\text{eff}}$  and the gate capacitance  $C_{\text{ox}}$  (or the MOS capacitor for that matter). After exceeding the gate voltage by  $V_{\text{DS}} > V_{\text{G}}$ , superposition of both voltages comes into effect.  $V_{\text{DS}}$  increases along the *x*-direction and decreases the effective gate voltage  $V_{\text{G}}$  at the channel region. Therefore, the length of the active channel varies along its expanse. Eventually, the channel will be pinched off and ideally any further increase of the drain current  $I_{\text{D}}$ stops [22]. This behavior can be observed in the output characteristics illustrated in figure 2.3a. The drain current  $I_{\text{D}}$  rises within the linear regime and stays unchanged in the saturation regime after  $V_{\text{DS}}$  exceeds  $V_{\text{G}} - V_{\text{th}}$ . At this point,  $I_{\text{D}}$  does not depend on changes in  $V_{\text{DS}}$  any more:

$$I_{\rm D} = \mu_{\rm eff} C_{\rm ox} \frac{W}{2L} (V_{\rm G} - V_{\rm th})^2 \quad {}^{\rm for \ V_{\rm DS} \ge V_{\rm G} - V_{\rm th}}_{\rm (saturation \ regime)} [3].$$

(2.2)

Figure 2.3b shows the transfer characteristic describing the drain current  $I_{\rm D}$  as a function of the gate voltage  $V_{\rm G}$ . The log scale depiction of an arbitrary MOSFET characteristic visualizes how the the on-state is delimited from the off-state by the threshold voltage  $V_{\rm th}$ . The off-state is defined by the electric potential barrier of the channel for  $V_{\rm G} < V_{\rm th}$ . Moving the barrier towards the thermally broadened Fermi distribution, the maximum slope of the current is restricted below  $V_{\rm th}$  at the so-called thermionic limit. The steeper the slope, the faster the transition to the on-state can be enforced.

**Figure 2.3:** *I*-*V* characteristic of the ideal *n*-channel MOSFET: (a) Output characteristics for the drain current  $I_D$  as a function of the drain-source voltage  $V_{DS}$  with four arbitrary incrementing gate voltages  $V_{G,1-4}$ . The dashed line marks the transition from the linear (ohmic) regime to the saturation regime. (b) Transfer characteristic with logarithmic (left) and linear axis (right) for the drain current  $I_D$  as a function of the gate voltage  $V_{G}$ . The threshold voltage  $V_{th}$  separates the on-state from the off-state. Below  $V_{th}$  the (subthreshold) slope is only graphically visible on the logarithmic scale.

### 2.1.2 Limitations and non-ideal Characteristics

Beyond the ideal description, one will find a lot of research on alternatives to the MOSFET implying that there must be some limitations in its use. As mentioned at the end of the previous section, the slope of  $I_{\rm D}$  is restricted below the threshold  $V_{\rm th}$ . This off-state limitation is particularly interesting, because it determines how abrupt the transition to the on-state will be. Consequently, the sharper the transition, the lower the operating voltage has to be. This characteristic is known as the subthreshold slope and is also illustrated in figure 2.3b. More commonly used though is the inverse subthreshold slope S to stress the required voltage in relation to the log-scale current, which is defined as

$$S\left[\mathrm{mV/dec}\right] = \left(\frac{\partial \log I_{\mathrm{D}}}{\partial V_{\mathrm{G}}}\right)^{-1} = \ln 10 \left(\frac{\partial I_{\mathrm{D}}}{\partial V_{\mathrm{G}}}\frac{1}{I_{\mathrm{D}}}\right)^{-1} \quad [3, 21].$$

(2.3)

In the interest of finding a more meaningful expression for S and with the assumption that the drain-source potential  $\phi_{\rm DS}$  is constant, the drain-current can then be expressed by<sup>2</sup>

$$I_{\rm D} = \frac{4}{\pi \hbar} \int_{-e\phi_{\rm ch}}^{\infty} f_{\rm S}(E) \mathrm{d}E \ [21].$$

(2.4)

As discussed in section 2.1.1, the gate potential - or more specific the channel potential - is still far away from the Fermi level of the source region  $E_{\rm F}^{\rm S}$  for the off-state. This allows replacing the Fermi distribution by the simpler Boltzmann approximation<sup>3</sup>  $f_{\rm S}(E) \approx \exp\left(\frac{(E_{\rm F}^{\rm S}-E)/k_{\rm B}T}{k_{\rm B}T}\right)$ , where  $k_{\rm B}$  is the Boltzmann constant and T the temperature [21]. Doing so, the integral from 2.4 is approximated to

$$I_{\rm D} \approx \frac{4}{\pi\hbar} \int_{-e\phi_{\rm ch}}^{\infty} \exp\left(\frac{E_{\rm F}^{\rm S} - E}{k_{\rm B}T}\right) \mathrm{d}E = \frac{4k_{\rm B}T}{\pi\hbar} \cdot \exp\left(\frac{E_{\rm F}^{\rm S} + e\phi_{\rm ch}}{k_{\rm B}T}\right).$$

(2.5)

Inserting  $I_{\rm D}$  from equation 2.5, the partial derivative  $\partial I_{\rm D}/\partial V_{\rm G}$  in equation 2.3 is solved by applying the chain rule and yields

$$\frac{\partial I_{\rm D}}{\partial V_{\rm G}} = e \cdot \frac{I_{\rm D}}{k_{\rm B}T} \cdot \frac{\partial \phi_{\rm ch}}{\partial \phi_{\rm G}} \,. \tag{2.6}$$

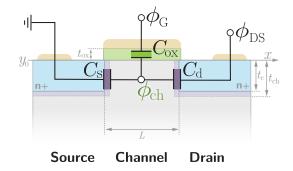

Next, to find a solution for the partial derivative  $\partial \phi_{ch} / \partial \phi_{G}$  an equivalent circuit will be of help [24]. This way the junctions at the source-channel transition and the drain-channel transition can be interpreted as capacitors  $C_{s}$  and  $C_{d}$ ,

$<sup>^{2}</sup>$ To avoid exceeding the scope of the thesis, the complete deduction of  $I_{\rm D}$  was dismissed. It can be found in [21] and [23].

<sup>&</sup>lt;sup>3</sup>Because the Boltzmann approximation applies to the high-energetic part of the Fermi distribution, it is usually called the *Boltzmann tail*.

respectively (which they basically are). They both are connected to the channel which in turn is connected to the gate capacitor  $C_{\text{ox}}$ . At this node, they all share the same channel potential  $\phi_{\text{ch}}$  (cf. figure 2.4).

From an ideal perspective, the gate potential  $\phi_{\rm G}$  and the channel potential  $\phi_{\rm ch}$  should be nearly identical, which is synonymous to perfect gate control. In reality, the channel potential also depends on the drain-source potential  $\phi_{\rm DS}$ and additional non-ideal capacitances, namely the inversion capacitance  $C_{inv}$ , the depletion capacitance  $C_{dep}$ , the dielectric interface capacitance  $C_{\rm if}$ , and obviously  $C_{\rm d}$  and  $C_{\rm s}$ . However, since the source terminal is usually set to ground,  $C_{\rm s}$  can be neglected.

**Figure 2.4:** For the ideal MOSFET the energy bands within the channel will exactly follow the gate potential  $\phi_{\rm G}$ . However, the real perspective reveals that the channel potential  $\phi_{\rm ch}$  differs from the gate potential  $\phi_{\rm G}$  and is shared amongst the three capacitors  $C_{\rm ox}$ ,  $C_{\rm s}$  and  $C_{\rm d}$ .

With that in mind, the relative change of  $\phi_{ch}$  can then be written as a potential divider:

$$\partial \phi_{\rm ch} = \partial \phi_{\rm G} \frac{C_{\rm ox}}{\Sigma C_{\Box}} + \partial \phi_{\rm DS} \frac{C_{\rm d}}{\Sigma C_{\Box}}$$

[21], (2.7)

with  $\Sigma C_{\Box} = C_{\text{ox}} + C_{\text{inv}} + C_{\text{dep}} + C_{\text{if}} + C_{\text{d}}$ . For the sake of simplicity,  $C_{\text{inv}}$ ,  $C_{\text{dep}}$ ,  $C_{\text{if}}$ and  $C_{\text{d}}$  are condensed to  $C_{\text{non-ideal}}$  for now. The partial derivative  $\partial \phi_{\text{ch}} / \partial \phi_{\text{G}}$  in equation 2.6 can then be extracted from equation 2.7. Knowing that the drainsource potential is constant, hence  $\partial \phi_{\text{DS}} = 0$ , equation 2.7 is simplified to

$$\frac{\partial \phi_{\rm ch}}{\partial \phi_{\rm G}} = \frac{C_{\rm ox}}{C_{\rm ox} + C_{\rm non-ideal}} \,. \tag{2.8}$$

Using equation 2.8, the inverse subthreshold slope may be written as

$$S = \ln 10 \left(\frac{\partial I_{\rm D}}{\partial V_{\rm G}} \frac{1}{I_{\rm D}}\right)^{-1} = \frac{k_{\rm B}T}{e} \ln 10 \cdot \left(\frac{C_{\rm ox} + C_{\rm non-ideal}}{C_{\rm ox}}\right) \quad [3, 21].$$

(2.9)

Assuming that  $C_{\text{ox}} \gg C_{\text{non-ideal}}$ , the lowest achievable inverse subthreshold slope is 60 mV/dec at room temperature (T = 300 K). This very specific value marks the limit in performance for every conventional MOSFET at this temperature. Besides that, the on-/off-ratio is also an important criteria for favorable switching behavior. The difference in current between those two states should be as high as possible. As a recommendation by the International Roadmap for Devices and Systems (IRDS) a MOSFET should maintain an on-/off-ratio of at least six decades  $(10^6)$  [6]. Therefore, a slope limitation of 60 mV/dec implies that a gate voltage of at least 360 mV will be necessary in order to switch from the off-state to the on-state. However, this is of course the most optimistic switching behavior possible. In reality, gate control is far from optimum and all parts of  $C_{\text{non-ideal}}$  contribute to a bigger inverse subthreshold slope, demanding for a much higher gate voltage. Unfortunately, a higher gate voltage also implies a higher supply voltage. Equation 2.10 shows how the dynamic and static power dissipates from the MOSFET:

$$P \propto f C_{\rm ox} V_{\rm DD}^2 + I_{\rm leak} V_{\rm DD} \ [23]. \tag{2.10}$$

$I_{\text{leak}}$  is the off-state leakage current and  $V_{\text{DD}}$  is the supply voltage. The gate charging frequency or the circuit clock frequency f for that matter is defined by the gate delay  $\tau$  as

$$\tau \le \frac{1}{f} := \frac{C_{\rm ox} W L V_{\rm G}}{I_{\rm D}} = \frac{2L^2}{\mu} \cdot \frac{V_{\rm G}}{(V_{\rm G} - V_{\rm th})^2} \ [23], \tag{2.11}$$

where  $I_{\rm D}$  is the on-state drain current within the saturation regime from equation 2.2. Considering that the gate voltage can only be as high as the supply voltage  $V_{\rm DD}$ ,  $V_{\rm G}$  might as well as be replaced by  $V_{\rm DD}$ . In general, the gate delay  $\tau$  serves as a good criteria for the on-state performance of the MOSFET. Obviously, it is desirable to increase the frequency while simultaneously reducing power losses. Equation 2.11 offers four approaches to do so: Reducing the channel length L. Increasing the carrier mobility  $\mu$ . Decreasing the supply voltage  $V_{\rm DD}$ . Reducing the threshold voltage  $V_{\rm th}$ . By looking closer to those options, the MOSFET again does reveal its limitations: Decreasing  $V_{\rm th}$  is actually not an option, because it would massively increase the off-state leakage current as exemplified in [21]. The carrier mobility is practically a constant of the material and is therefore set by silicon and the dopant concentration. Aggressively reducing the supply voltage would be an option, however, the mentioned limit in S requires for at least 360 mV.<sup>4</sup> The only option left is to reduce the channel length while maximizing gate control. To accomplish this it is necessary to reevaluate equation 2.7. Considering the case that the MOSFET is in the on-state, i.e.  $\partial \phi_{\rm DS} \neq 0$ , the drain-source potential must be somehow detached from equation 2.7. This is achieved by assuming  $C_{\rm ox} \gg C_{\rm d}$  and that the donor

<sup>&</sup>lt;sup>4</sup>Note that in real applications a so-called overdrive voltage adds to the 360 mV, which is usually around  $\times$  1-2 the threshold voltage, ultimately limiting the supply voltage to  $\sim$ 1 V.

concentration is usually very high which results in very thin depletion layers around the *n*-regions. It follows that the channel thickness  $t_{\rm ch}$  can be roughly considered being equal to the depth of the *n*-regions  $t_{\rm c}$  (cf. figure 2.1). Next, dismembering  $C_{\rm ox}$  and  $C_{\rm d}$  yields:

$$\underbrace{\epsilon_{0}\epsilon_{\mathrm{ox}}}_{C_{\mathrm{ox}}} \underbrace{WL}_{C_{\mathrm{ox}}} \gg \underbrace{\epsilon_{0}\epsilon_{\mathrm{ch}}}_{C_{\mathrm{d}}} \underbrace{W \cdot t_{\mathrm{ch}}}_{C_{\mathrm{d}}} \quad [23].$$

Now, condition 2.12 can finally be rearranged for L, resulting in:

$$L \gg \sqrt{\frac{\epsilon_{\rm ch}}{\epsilon_{\rm ox}} t_{\rm ox} t_{\rm ch}} \equiv \lambda_{\rm ch} \ [23].$$

(2.13)

Here, the right term of statement 2.13 can be interpreted as the gate geometry factor  $\lambda_{\rm ch}$ . In general, this factor can be considered as a screening length for the electrical field inside the channel.<sup>5</sup> Evidently, a channel length L much longer than  $\lambda_{\rm ch}$  will sufficiently screen the channel potential from the drain-source potential [21]. This is of course inconsistent to the first mentioned option of maximizing performance, that is reducing the channel length L. Nevertheless, changing the MOSFET's geometry, i.e. reducing L, is still the only option left. The implications are discussed next.<sup>6</sup>

### 2.1.3 Impact of Short Channel Geometries

So far, the focus primarily lied on the so-called long channel MOSFET. Over the last decades however, the demand for highly integrated and also highly performing transistors has vastly increased. As a consequence, the geometry has been scaled down far below sub-100 nm dimensions [25]. Unfortunately, the steady reduction of the MOSFET's channel prompted new problems.

Although the basic working principle has not changed, a much shorter channel will make the device more elaborate and difficult to control. The primary reason for this are the depletion zones around source and drain. Their relative expanse in comparison to the channel cannot be neglected anymore. Since the drain-source voltage  $V_{\rm DS}$  usually refers to ground potential of source, it is the depletion zone around the drain region which is expanding with rising  $V_{\rm DS}$ . If the expanse takes up significantly more space within the relatively short channel, the gate potential will be shielded and effectively reduced (cf. equation 2.13). A more general approach is described

<sup>&</sup>lt;sup>5</sup>Comparable to the Debey-length  $\lambda_{\rm D}$  in doped semiconductors.

<sup>&</sup>lt;sup>6</sup>Note that for MOSFETs the channel is made from silicon ( $\epsilon_{ch} = \epsilon_{Si}$ ). However, this approach is valid for all gate-controlled devices and is not unique to silicon. Further references on that matter are therefore addressed just as "channel material".

#### 2.1 The MOSFET

by Yan et al. [26] using the channel's electrostatics: Starting with Poisson's differential equation, Yan et al. simplify the potential of the channel  $\phi(x, y)$  by applying three boundary conditions so that the equation is left with the sole potential at the surface:  $\phi(x, y_0) := \phi(x)$ :

$$\frac{\mathrm{d}^2\phi(x)}{\mathrm{d}x^2} - \frac{\phi(x) - \phi_{\mathrm{G}}}{\lambda_{\mathrm{ch}}^2} = \frac{eN_{\mathrm{A}}}{\epsilon_0\epsilon_{\mathrm{ch}}} \quad [26].$$

The equation contains the gate potential  $\phi_{\rm G}$ , the doping concentration inside the channel region  $N_{\rm A}$  (*p*-substrate) and the permittivity of the channel material  $\epsilon_0 \epsilon_{\rm ch}$ . The key value is the channel geometry factor  $\lambda_{\rm ch}$ , because it determines the solution for  $\phi(x)$  which is proportional to  $\exp(\pm x/\lambda_{\rm ch})$ . As a reminder,  $\lambda_{\rm ch}$  can be considered as a screening length for the potential inside the channel. For planar gate geometries like the MOSFET,  $\lambda_{\rm ch} = \sqrt{\frac{\epsilon_{\rm ch}}{\epsilon_{\rm ox}} t_{\rm ox} t_{\rm ch}}$ . In case of impurity doping,  $\lambda_{\rm ch}$  will be influenced by the depletion zones of source and drain, because their expanse determines the channel thickness  $t_{\rm ch}$ .

Figure 2.5a illustrates the problem of the expanding depletion zone from the drain region into the channel. The length of the channel L can be expressed by units of  $\lambda_{\rm ch}$ . For  $L \leq \lambda_{\rm ch}$  the depletion zones will overlap and there is no way to pinch off the channel any more. The energy bands at the surface for  $L = 4\lambda_{\rm ch}$  and  $L = 8\lambda_{\rm ch}$  are shown in figure 2.5b: The closer the channel length is to  $\lambda_{\rm ch}$ , the less influence the gate potential has and the energy barrier towards the channel is lowered, implying that more electrons will be

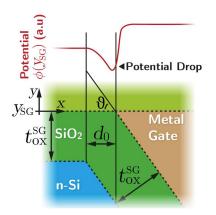

**Figure 2.5:** The length of the channel L can be described by using the gate geometry factor  $\lambda_{ch}$  as a natural scale of screening. The cross-section in (a) illustrates how the depletion zones of the source, drain and channel region interact with each other. (b) depicts the energy bands at the surface  $y_0$  for their respective electric potentials as a function of  $\lambda_{ch}$ . As an example, for  $L = 4\lambda_{ch}$  the barrier from source towards the channel is lowered and DIBL occurs. Increasing L to  $8\lambda_{ch}$  the gate potential gains more influence and DIBL can be avoided [27, 28]. For simplicity ratios for L have been chosen arbitrarily.

injected into the channel region. This effect is called drain induced barrier lowering (DIBL) and has a negative impact on the transfer characteristic of the transistor, because it results in higher leakage currents.<sup>7</sup> The inverse subthreshold slope increases and it is more difficult to control the device. An analytical expression of DIBL affecting S is given by:

$$S \approx \frac{k_{\rm B}T}{e} \ln 10 \cdot \left[ 1 - 2 \cdot \exp(-\frac{L}{2\lambda_{\rm ch}}) \right]^{-1}, \quad \text{DIBL} = \frac{\partial \phi_{\rm ch}}{\partial \phi_{\rm DS}} \approx \exp(\frac{-L}{2\lambda_{\rm ch}}) \quad [21].$$

(2.15)

Note that the expanse of the depletion zones of source and drain into the channel  $\lambda_{\rm S}$  and  $\lambda_{\rm D}$ , respectively, are omitted, because they only depend on the doping concentrations  $(\lambda_{\rm S}, \lambda_{\rm D} \propto (N_{\rm A,D})^{-1/2})$ , which should to be very low in order to maintain control over the channel via the gate.

After all, if DIBL has to be avoided but L is desired to be extremely short anyway,  $\lambda_{ch}$  has to be minimized. The most practical way to do so is by using very thin gate dielectrics with high relative permittivity<sup>8</sup>. Provided the channel thickness  $t_{ch}$  is independent from impurity doping, a thin body layout will also work in favor. Additionally, the device layout can be implemented as a double gate or even as a cylindrical gate-all-around geometry to increase control over the channel [30–32]. For the latter  $\lambda_{ch}$  changes to

$$\lambda_{\rm ch} = \sqrt{\frac{1}{8} \frac{\epsilon_{\rm ch}}{\epsilon_{\rm ox}} t_{\rm ch}^2 \cdot \ln\left(1 + \frac{t_{\rm ox}}{t_{\rm ch}}\right)} \quad [31], \qquad (2.16)$$

yielding much smaller values for  $\lambda_{ch}$  when compared to equation 2.13. Siliconon-insulator (SOI)- and nanowire-MOSFET technologies with gate-all-around geometry yield an inverse subthreshold slope very close to 60 mV/dec [30, 32-35].

### 2.2 Novel Transistor Technologies

Although, the mentioned gate-all-around MOSFETs show improved gate control, they still cannot overcome the limit of S = 60 mV/dec. In fact, every field effect transistor which relies on injecting carriers from the thermally broadened Fermi distribution is bound by that thermionic limit. Of course technological development did not stop there. The need for denser integration and lesser power consumption motivated research and boosted inventions. Extremely sophisticated fabrication technologies enabled new possibilities and

$<sup>^{7}</sup>$ Note that besides DIBL there are numerous other short channel effects [29], such as channel length modulation or hot carrier degradation which are omitted here.

<sup>&</sup>lt;sup>8</sup>In common literature the term high- $\kappa$  dielectric is used very often. Note that in this thesis the symbol for the relative permittivity in a mathematical context is always  $\epsilon_{\text{ox}}$ .

gave birth to new transistor architectures, that are indeed able to overcome the limit of S = 60 mV/dec. [36–43]. Motivated by this growing field of new transistor research, the main subject of this thesis is the fabrication and characterization of transistors having silicon replaced by carbon nanotubes. To justify this choice, three criteria have to be fulfilled: First, the device should obviously exhibit an inverse subthreshold slope below 60 mV/dec(subsections 2.2.1 and 2.2.2). Second, the device geometry must be designed in a way to achieve maximum gate control (subsection 2.2.3). And third, the properties of alternative channel materials must show distinct advantages over silicon (subsection 2.2.4). The next sections cover all of the three requirements, showing how they actually contribute to the development of transistors being superior to the MOSFET.

### 2.2.1 Tunnel FETs

As mentioned before, every field effect transistor which relies on injecting carriers from the Boltzmann tail of the Fermi distribution has a limited inverse subthreshold slope of 60 mV/dec at 300 K. Being able to go steeper than this natural limitation is the sought objective of modern transistor research, hence the term steep slope transistor (SST).

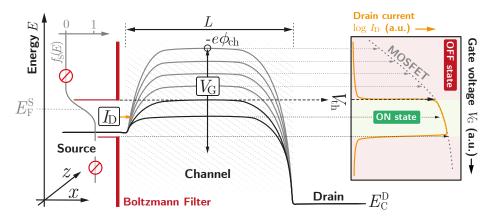

Basically, the objective of any SST is to inhibit the carrier injection from the Boltzmann tail thus suppressing the thermal leakage current. Figure 2.6 supplements the MOSFET energy bands by an imaginary Boltzmann filter. Consequently, the drain current only increases from injection of the low energetic part of the Fermi distribution with an incredibly steep slope far below  $60 \,\mathrm{mV/dec}$ . The question at hand is how to realize this filtering. One prominent way is the so-called Tunnel-FET or TFET for short.

**Figure 2.6:** Principle of SSTs: Preventing thermal injection from the Boltzmann tail leads to an extremely steep transition from the off-state to the on-state.

A TFET device is based on band-to-band tunneling (BTBT). By using either asymmetrical n-i-p impurity or electrostatic doping, the valence band in the intrinsic channel can be positioned very close to and also above the conduction band of the n-doped source region. The probability for quantum tunneling between the two bands then vastly rises. Naturally, BTBT is not bound to occur only at the source-channel transition. If the channel conduction band drops below the valence band in drain, tunneling also starts to occur at the channel-drain transition (unfortunately, this ambipolarity gives room for more off-state current leakage [28], which is omitted for now).

Figure 2.7 shows the valence and conduction band of a TFET device. The Fermi levels are fully aligned with the respective bands of source and drain. This is actually the ideal case, because in this scenario the conduction band of the source is nearly empty (this matter will be discussed later in this section). Since source and drain are of opposite doping and the channel is kept intrinsic, the channel potential  $\phi_{ch}$  can push the channel valence band above the conduction band of the source [44]. At the transition BTBT with the probability T(E) occurs. The resulting drain current is

$$I_{\rm D} = \frac{e}{\pi\hbar} \int_{-\infty}^{\infty} T(E) (f_{\rm S}(E) - f_{\rm D}(E)) \,\mathrm{d}E \quad [21], \qquad (2.17)$$

where  $f_{\rm S}(E)$  and  $f_{\rm D}(E)$  are the Fermi distributions of source and drain region, respectively. The energy difference from the conduction band of source to the valence band of the channel  $E_{\rm C}^{\rm S} - E_{\rm V}^{\rm ch}$  determines the energetic window in which BTBT becomes possible (light green strip). Under the assumption that  $E_{\rm C}^{\rm S} = 0$ , the window's height matches the channel valence band at  $-e\phi_{\rm ch}$ . Thus, the limits for the integral in equation 2.17 can be chosen accordingly, i.e. from 0 to  $-e\phi_{\rm ch}$ .<sup>9</sup> The difference of  $f_{\rm S}(E)$  and  $f_{\rm D}(E)$  is visualized on the left side in figure 2.7 (hatched green area). When solving the integral within the given limits, the resulting function F will only depend on the channel potential  $\phi_{\rm ch}$ . For the ideal scenario of perfect gate control ( $\phi_{\rm G} = \phi_{\rm ch}$ ), F might as well be expressed as a function of the gate potential  $F(\phi_{\rm G})$ . The energetic window for BTBT can therefore be manipulated by the external gate voltage. A helpful tool to solve the tunnel probability T(E) is linearizing the band curvature at the transition and using the Wentzel-Kramers-Brillouin (WKB) approximation. By applying this method, T(E) can be expressed as

$$T(E) \approx T_{\rm WKB}(E) = \exp\left(\frac{-4(\lambda_{\rm S} + \lambda_{\rm ch})\sqrt{2m^*} E_{\rm g}^{3/2}}{3\hbar(E + E_{\rm g})}\right)$$

[45], (2.18)

<sup>&</sup>lt;sup>9</sup>Note that in this simple approach off-state current leakage due to minor thermal carrier injection from above the conduction band and also from below the valence band is omitted.

#### 2.2 Novel Transistor Technologies

with  $\lambda = \lambda_{\rm S} + \lambda_{\rm ch}$  being equal to the tunnel barrier distance. The band gap  $E_{\rm g}$  and the effective carrier mass  $m^*$  are given by the channel material and the maximum energy E is equal to  $-e\phi_{\rm ch}$ , deducing  $T_{\rm WKB}(E)$  also becomes a function of the gate potential:  $T_{\rm WKB}(\phi_{\rm G})$ . By using  $F(\phi_{\rm G})$  and  $T_{\rm WKB}(\phi_{\rm G})$  equation 2.17 can be approximated as:

$$I_{\rm D} \approx \frac{-e}{\pi\hbar} T_{\rm WKB}(\phi_{\rm G}) F(\phi_{\rm G})$$

[45]. (2.19)

Based on equation 2.3, the inverse subthreshold slope can be calculated by inserting the drain current for the TFET from equation 2.19, which gives

$$S = \ln(10) \frac{1}{e} \left( \frac{\partial T_{\rm WKB}(\phi_{\rm G})}{\partial \phi_{\rm G} \cdot T_{\rm WKB}(\phi_{\rm G})} + \frac{\partial F(\phi_{\rm G})}{\partial \phi_{\rm G} \cdot F(\phi_{\rm G})} \right)^{-1} \quad [21, 23]. \tag{2.20}$$

Two cases have to be considered here: First, if the tunnel probability  $T_{\text{WKB}}(\phi_{\text{G}})$  is low but rapidly changes as a function of the gate potential, the inverse subthreshold slope breaks down to

$$S \approx \ln(10) \frac{1}{e} \cdot \frac{3\hbar(-e\phi_{\rm G} + E_{\rm g})}{4(\lambda_{\rm ch} + \lambda_{\rm S})\sqrt{2m^*} E_{\rm g}^{3/2}} \quad [21].$$

Second, if  $T_{\text{WKB}}(\phi_{\text{G}})$  is very high (i.e. close to one) but does not change as a function of the gate potential, it will no longer be important and S will become a simple function of the gate potential only:

$$S \approx \ln(10) \cdot \phi_{\rm G} \quad [21]. \tag{2.22}$$

**Figure 2.7:** Band configuration of a TFET device for the on-state: The mutual proximity of the valence band of the channel and the conduction band of the source region enables BTBT. The blue triangles represent the potential barrier approximating the WKB tunneling probability  $T_{\text{WKB}}(E)$ .  $F(\phi_{\text{ch}})$  is illustrated on the left as a result of the integral of  $f_{\text{S}}(E) - f_{\text{D}}(E)$  from equation 2.17 (hatched green area). Note that in this illustration the Fermi level of source is equal to the hight of the conduction band.

In both cases S becomes independent from thermal carrier injection offering the possibility of much steeper slopes. Carrier injection into the channel can only occur within the energetic tunneling window applied on the Fermi distribution. The Boltzmann tails at both ends of the function are almost cut off, so that the window is in fact operating as band-pass filter. [21]

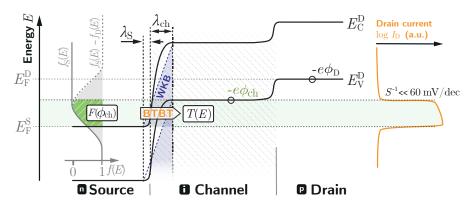

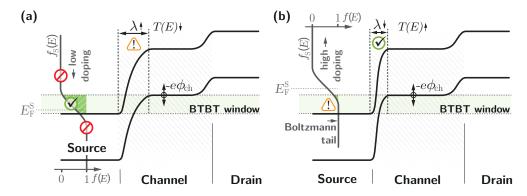

To enforce the case in which equation 2.22 is dominant, two criteria have to be met for obtaining a very steep subtreshold slope: First, the BTBT probability  $T_{\rm WKB}(\phi_{\rm G})$  must come as close to one as possible. When considering equation 2.18 it is obvious that the expanse of the depletion zone of the source and the channel geometry factor  $\lambda_{ch} + \lambda_{S}$  must be rather small in order to get  $T_{\rm WKB}(\phi_{\rm G})$  towards one. This can be achieved by applying the same optimization methods for  $\lambda_{ch}$  as discussed in subsection 2.1.3.  $\lambda_{s}$  can be decreased by an extremely high doping concentration in the source region. The higher the concentration, the smaller the expanse of the depletion zone. Furthermore, a material with a very low effective carrier mass  $m^*$  is of help as well as a small band gap. Although, a (too) small band gap may increase leakage current. Second, the doping of the source region must be kept low, which is of course contradicting to the just mentioned statement. However, a lower doping concentration leads to a source conduction band being almost empty, allowing all electrons to tunnel from the channel valence band to the vacant states in the source conduction band. Only then the Fermi level lies at the conduction band edge and the Boltzmann tails will be cut off (cf. figure 2.8a). However, as mentioned earlier, a low doping concentration increases

**Figure 2.8:** Electronic band structure of a TFET device for different source doping profiles. (a) A low doping concentration leads to band-pass filtering of the Fermi distribution and the Boltzmann tail gets cut off. At the same time  $\lambda = \lambda_{S} + \lambda_{ch}$  becomes larger, thus increasing the tunneling distance which also decreases the BTBT probability T(E). (b) A high doping concentration has the reverse effect. T(E) will be closer to one while on the downside the energetic BTBT window applies partially or entirely on the Boltzmann tail of the Fermi distribution. [23, 46]

the expanse of the depletion zone, that in turn will again decrease  $T_{\text{WKB}}(\phi_{\text{G}})$ . On the other hand, a too high doping concentration moves the Fermi level away from the conduction band leading to a low  $F(\phi_{\text{G}})$  and to an energetic window being applied to the Boltzmann tail of the Fermi distribution (instead of cutting off the Boltzmann tail, cf. figure 2.8b). In this case the device does not behave like a TFET but rather like a conventional transistor not being able to overcome the limit of 60 mV/dec. [21,23,46]

Fabricating a TFET requires the channel to be split up into three different gates. One gate is needed for device control (main gate) and two additional gates for implementing the doping. Adjusted individually, these gates allow for different band configurations along the channel region satisfying the mentioned conditions in order to configure a TFET device. Obviously, standard doping by implanting impurities will not provide the necessary scope for dynamically adjusting gate potentials, therefore the gates must be implemented as mutually insulated electrodes [11]. In this case, the energy bands will be controlled by the electrical field from each electrode.<sup>10</sup> Chapter V elaborates on the so-called buried triple gate (BTG) architecture, which was fabricated within the scope of this thesis. Its purpose is to provide the necessary electrostatic doping landscape for TFET devices.

# 2.2.2 Energy Filtering FETs

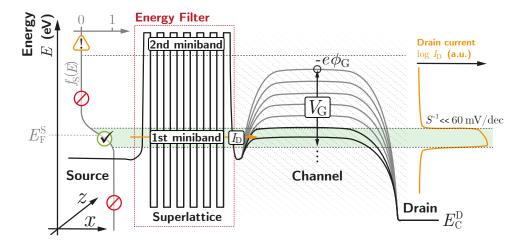

Despite its name, the part being responsible for the steep slope of a TFET is not the tunneling per se. However, the band-to-band tunneling determines the filtering function and is not easy to control. In fact, not being able to setup the configuration properly the TFET will operate even worse than latest MOSFET designs. Only by achieving energy filtering, the TFET exhibits a very steep subthreshold slope. Nonetheless, this major downside can be bypassed by creating an actual energy filter without the involvement of BTBT. One exemplary application is the Superlattice-FET or simply energy filtering FET (EF-FET).

Similar to the TFET architecture multiple gates can be used to control the EF-FET: Implementing a certain setup of a reconfigurable gate landscape can work as a bandpass filter, too. The gates must be switched in alternating sequence in order to create periodic potential barriers. If the physical distance between the potential barriers is small enough, an energetic superlattice emerges, comparable to the periodic potentials in solid state crystals. Within the superlattice, injection through the barriers becomes possible and

$<sup>^{10}</sup>$  Noteworthy theoretical and experimental research on TFET architectures can be found in [12, 13, 28, 31, 43, 47].

generates a cosine-shaped miniband. Therefore, a specific energetic window with a non-zero density of states enables carrier transport inside this window. When applied on the low energy part of the source Fermi distribution, the miniband is able to function as a band-pass filter for the high energetic Boltzmann tail. The distance between the potential barriers generating the superlattice is anti-proportional to the miniband's width. To reach sufficiently high currents, the tunneling distance must be very small. Unfortunately, for higher energies additional minibands will develop. If the barrier distance will be too small, not only the first miniband will grow larger but the second miniband, too, increasing mutual proximity. Obviously, the energetically higher placed second miniband will contribute to thermal leakage current due to carrier injection from the Boltzmann tail. This way, the EF-FET cannot yield an inverse subthreshold slope below  $60 \,\mathrm{mV/dec}$ . The only way to avoid unfavorable minibands - while still yielding sufficient carrier transport - is by finding a trade-off solution with appropriate barrier lengths. In order to function as a transistor, the energy filter has to be combined with a FET channel (cf. figure 2.9). For a current-less off-state, the channel potential  $\phi_{\rm ch}$ must be carefully placed above the first miniband but still below the second miniband to avoid injection from the Boltzmann tail. Only the filter within the first miniband prevents carrier injection from the Boltzmann tail. Eventually, when the channel potential energetically drops below the filter itself, carrier injection quickly rises for a steep transition to the on-state.

**Figure 2.9:** Conduction band of an EF-FET [21, 48]: The alternating potentials at the gates create a superlattice which leads to a miniband along the gate cluster. The carrier injection from source into the channel comes from the non-thermally broadened part of the Fermi function, thus only within a filtering window. Injected carriers can then tunnel throughout the tunable miniband. If the band in the FET channel will be pushed inside the filtering window, the device can transit to the on-state with *S* far below 60 mV/dec.

Once the on-current has been reached, the current is restricted and its density j stays constant even with further lowering of the channel potential. This is due to the continuity equation, in which the density of carriers n decreases for lower channel potentials but at the same time carrier velocity  $\nu$  must increase  $(j = en \cdot \nu = \text{const.})$  [21]. Note that this transistor architecture also comes with a major disadvantage: By deploying multiple gates in a lateral system, scaling down the device becomes quiet difficult. Thus, possible applications will focus on low-power devices rather than on increased integration density.<sup>11</sup> The buried multi gate (BMG) architecture fabricated by Grap et al. [16, 48] is designed for such energy filter applications (providing up to 17 gates for each device in the latest version). Alongside the buried triple gates, the buried multi gates serve as a fundamental platform for developing steep slope transistors in this thesis and will be introduced in chapter V.

### 2.2.3 One-Dimensional Channel Geometries

Section 2.1.3 describes how gate control can be increased by deploying small values for  $\lambda_{ch}$ . Wrapping the gate around the channel i.e. having a concentric cylinder capacitor for  $C_{ox}$ ,  $\lambda_{ch}$  can be minimized even further (eq. 2.16). The equation for  $\lambda_{ch}$  derived from the condition  $C_{ox} \gg C_d$ , ignoring the non-ideal capacitances inside the FET channel  $C_{inv}$ ,  $C_{dep}$  and  $C_{if}$  as seen in equation 2.7 and 2.8. However, for the overall desire for perfect gate control, <u>all</u> non-ideal capacitors have to be decisively smaller than  $C_{ox}$ , so that the channel potential eventually can be expressed by this linear term:

$$\phi_{\rm ch}(\phi_{\rm G}) = \phi_{\rm G} + {\rm const.}$$

[48]. (2.23)

This state is called the quantum capacitance limit and allows for the channel potential to linearly change with the gate potential without any losses, i.e. perfect gate control. [8,21,48]

To be brief, a superior field effect transistor must be designed to minimize the non-ideal capacitors, so that  $C_{\text{ox}} \gg C_{\text{non-ideal}}$ . Condition  $C_{\text{ox}} \gg C_{\text{dep}}$  can be achieved by decreasing the channel thickness or the depletion length, respectively.  $C_{\text{ox}} \gg C_{\text{if}}$  is satisfied when incorporating extremely high quality dielectrics with low interface states, which of course demands for a native oxide or extraordinary deposition techniques. Both of the mentioned criteria are important and complex in their own way, but the last condition  $C_{\text{ox}} \gg C_{\text{inv}}$  deserves some attention in particular: For an increasing channel potential, 2D sub-energy bands begin to develop inside the inversion layer

$<sup>^{11}\</sup>mathrm{Noteworthy}$  theoretical and experimental research on superlattice architectures can be found in [17, 18, 49–52].

below the gate dielectric, in turn increasing the carrier density at this point. Inside the channel region, the 2D density of states effectively becomes a 3D density of states being proportional to

$$D_{\rm 3D}(E) \propto \sqrt{E_{\rm F} - e\phi_{\rm ch}}$$

[53]. (2.24)