## Software Exploitation of Traditional Interfaces for Modern Technologies

Dissertation

zur Erlangung des Grades eines

Doktors der Ingenieurwissenschaften

der Technischen Universität Dortmund an der Fakultät für Informatik

von

Christian Hakert

Dortmund 2024

| Tag der mündlichen Prüfung: | 18. Juli 2024                    |

|-----------------------------|----------------------------------|

| Dekan/Dekanin:              | Prof. DrIng. Gernot A. Fink      |

| Gutachter/Gutachterinnen:   | Prof. DrIng. Jian-Jia Chen       |

|                             | Prof. DrIng. Jeronimo Castrillon |

## Acknowledgments

In the first place, I would like to express my deep gratitude to my advisor (Doktorvater) Prof. Jian-Jia Chen. Besides his great supervision during my studies, he was always open for new and unconventional ideas. He always supported me in following my ideas, motivated me to continue specific topics and supported bringing results to a publishable status. Beyond this, I have to express my appreciation for his support in involving me in the writing of new project proposals, which lead to two successfully accepted research projects, which stem from topical areas of this dissertation. Furthermore, I would like to thank my second examiner, Prof. Jeronimo Castrillon, to commit to review my dissertation.

Next, I express my deep appreciation to my colleagues, who collaborated with me for my studies and co-authored my published papers. Most important, I would like to thank my colleague Kuan-Hsun Chen for accompanying me during my entire study and working on many topics with me. I further would like to thank my other colleagues, who collaborated with me throughout my different studies. From the DAES group of the LS12 at TU Dortmund University, these are Nils Hölscher, Mario Günzel, Georg von der Brüggen and Daniel Biebert. From the CES group from KIT, these are Lars Bauer, Paul Genssler and Prof. Jörg Henkel. Beyond my colleagues, my studies have been supported by different research projects. These include the DFG project OneMemory(405422836), the DFG special priority program 2377(460954224) and the DFG project MemoryDiplomat(502384507). I would like to express special appreciation to the collaborators of the OneMemory project in Taiwan. Furthermore, I have to express my deep gratitude to my non-scientific colleagues and to the people who collaborated with me in teaching and administration. Without their help and support, I would not have been able to conduct my studies in the way I did. Special appreciation goes to the secretary of the LS12, namely Claudia Graute.

Finally, but nevertheless important, I would like to express my deepest gratitude to my family and friends for their unbreakable support. Especially, I would like to thank my parents for making my academic career so far possible at all and never stopped in supporting me on my way. I further want to express my appreciation to all of my friends for supporting me all along.

## Abstract

Modern computer Technologies are skyrocketing to spheres, which frequently seemed unimaginable years ago. Quantum effect petabyte-sized storage devices or deep cache hierarchies, acting within nanoseconds, make only a few examples. At the same time, interfaces to communicate with such technologies are settled and remain largely unaffected by the technology development. While loading and storing a word to a given memory address was the standard interface to communicate with memory devices in very early stages of computer systems, it still features a similar shape nowadays. Unsurprisingly, modern computing technologies come with increasing demand of management, such as lifetime management for NON-VOLATILE MEMORY (NVM) or prefetching and eviction strategies for cache hierarchies. Leaving this management to the hardware solely provides a limited design space and space for optimization. Consequently, software has to find ways, which allow an either direct or indirect management of the technologies over the traditional interfaces.

This dissertation picks up this need and studies selected modern technologies and their need for management. Methods are presented in this thesis, which systematically exploit existing traditional interfaces in order to provide extended functionalities for the management of modern technologies. The exploitations in this thesis are solely conducted on a software level and do not require any actions in the available hardware. In a first part, memory technologies are picked up as a target technology. In greater detail, NON-VOLATILE MEMORY (NVM) is studied. This thesis discusses the lifetime issue of these technologies and the resulting need for wear-leveling. Various approaches are introduced, which allow different forms of wear-leveling on different levels of the software. This ranges from wear-leveling procedures inside the operating system and the system software towards direct application integration to extend the memory lifetime. Apart from the lifetime issue, the latency and energy property of a specific type of emerging memory, namely RACETRACK MEMORY (RTM), is considered. Dedicated to the application of RANDOM FOREST (RF) models, the access properties are optimized in the application level directly.

In the last part of this thesis, the focus is moved from memories to arithemtic compution. RANDOM FOREST (RF) models are kept as a target application and their execution on modern computation technologies is considered. The usage of floating-point numbers is put to a major focus and the memory behavior of floating-point numbers is optimized. By proposing alternative computation schemes for floating-point numbers, which are entirely realized in software and leave the hardware untouched, significant performance improvement is gained.

## **Publications**

The topical contributions of this thesis are published for major parts in the form of peer-reviewed articles in journals and conferences. The following publications form the topical contributions of this thesis:

- [HCC22a] C. Hakert, K.-H. Chen, and J.-J. Chen. "FLInt: Exploiting Floating Point Enabled Integer Arithmetic for Efficient Random Forest Inference". In: arXiv preprint arXiv:2209.04181 (2022) (Cited on pages 16, 148).

- [HCC22b] C. Hakert, K.-H. Chen, and J.-J. Chen. "Immediate Split Trees: Immediate Encoding of Floating Point Split Values in RandomForests". In: *European Conference* on Machine Learning and Principles and Practice of Knowledge Discovery in Databases (2022) (Cited on pages 16, 136).

- [HCC24] C. Hakert, K.-H. Chen, and J.-J. Chen. "FLInt: Exploiting Floating Point Enabled Integer Arithmetic for Efficient Random Forest Inference". In: *Design, Automation* and Test in Europe Conference (2024) (Cited on page 148).

- [HCK+20] C. Hakert, K.-H. Chen, S. Kuenzer, S. Santhanam, S.-H. Chen, Y.-H. Chang, F. Huici, and J.-J. Chen. "Splitn Trace NVM: Leveraging Library OSes for Semantic Memory Tracing". In: *9th Non-Volatile Memory Systems and Applications Symposium (NVMSA)*. 2020 (Cited on pages 16, 41, 71).

- [HCS+21] C. Hakert, K.-H. Chen, H. Schirmeier, L. Bauer, P. R. Genssler, G. von der Brüggen, H. Amrouch, J. Henkel, and J.-J. Chen. "Software-Managed Read and Write Wear-Leveling for Non-Volatile Main Memory". In: ACM Transactions on Embedded Computing Systems Special Issue on Memory and Storage Systems for Embedded and IoT Applications. 2021 (Cited on pages 16, 58).

- [HKC+21a] C. Hakert, A. A. Khan, K.-H. Chen, F. Hameed, J. Castrillon, and J.-J. Chen. "BLOwing Trees to the Ground: Layout Optimization of Decision Trees on Racetrack Memory". In: 58th ACM/IEEE Design Automation Conference (DAC), accepted. 2021 (Cited on pages 16, 104).

- [HKC+21b] C. Hakert, R. Kühn, K.-H. Chen, J.-J. Chen, and J. Teubner. "OCTO+: Optimized Checkpointing of B+Trees for Non-Volatile Main Memory Wear-Leveling". In: *The* 10th IEEE Non-Volatile Memory Systems and Applications Symposium (NVMSA). IEEE, 2021 (Cited on pages 16, 90).

- [HKC+22] C. Hakert, A. A. Khan, K.-H. Chen, F. Hameed, J. Castrillon, and J.-J. Chen. "ROLLED: Racetrack Memory Optimized Linear Layout and Efficient Decomposition of Decision Trees". In: *IEEE Transactions on Computers* (2022) (Cited on pages 16, 116).

- [HYC+19] C. Hakert, M. Yayla, K.-H. Chen, G. v. d. Brüggen, J.-J. Chen, S. Buschjäger, K. Morik, P. R. Genssler, L. Bauer, H. Amrouch, and J. Henkel. "Stack Usage Analysis for Efficient Wear Leveling in Non-Volatile Main Memory Systems". In: 1st ACM/IEEE Workshop on Machine Learning for CAD (MLCAD). Alberta, Canada, 2019 (Cited on pages 16, 83).

# Contents

| 1 | Intro | oductio | on                                                            | 1  |

|---|-------|---------|---------------------------------------------------------------|----|

|   | 1.1   | Exploi  | iting Traditional Interfaces                                  | 3  |

|   |       | 1.1.1   | Relevance to the Research Community                           | 4  |

|   |       | 1.1.2   | Interface Exploitation for NON-VOLATILE MEMORY (NVM) Lifetime | 5  |

|   |       | 1.1.3   | Interface Exploitation for RACETRACK MEMORY (RTM) Properties  | 6  |

|   |       | 1.1.4   | Interface Exploitation for Immediate Arithmetic               | 6  |

|   | 1.2   | Contri  | ibution of this Work                                          | 7  |

|   |       | 1.2.1   | Application Transparent NVM Wear-Leveling                     | 8  |

|   |       | 1.2.2   | Application Cooperative NVM Wear-Leveling                     | 9  |

|   |       | 1.2.3   | Memory Optimization for Random Forests                        | 11 |

|   |       | 1.2.4   | CPU Optimization for Random Forests                           | 13 |

|   | 1.3   | Organ   | nization of the Thesis                                        | 15 |

|   | 1.4   | Author  | r's Contribution to this Thesis                               | 15 |

| 2 | Bac   | karour  | nd and Related Work                                           | 17 |

|   | 2.1   | •       |                                                               | 18 |

|   |       | 2.1.1   | 5 5                                                           | 18 |

|   |       | 2.1.2   |                                                               | 23 |

|   |       | 2.1.3   |                                                               | 25 |

|   |       | 2.1.4   |                                                               | 26 |

|   | 2.2   | Relate  |                                                               | 28 |

|   |       | 2.2.1   |                                                               | 28 |

|   |       | 2.2.2   | RTM Optimization                                              | 32 |

|   |       | 2.2.3   | •                                                             | 33 |

| 3 | Svs   | tem Mo  | odel                                                          | 35 |

| • | 3.1   |         |                                                               | 36 |

|   |       | 3.1.1   |                                                               | 36 |

|   |       | 3.1.2   |                                                               | 38 |

|   |       | 3.1.3   |                                                               | 39 |

|   |       | 3.1.4   | •                                                             | 40 |

|   |       | 3.1.5   |                                                               | 41 |

|   |       | 3.1.6   | •                                                             | 43 |

|   | 3.2   | Rando   | -                                                             | 44 |

|   |       | 3.2.1   |                                                               | 45 |

|   |       | 3.2.2   |                                                               | 46 |

|   |       | 3.2.3   | -                                                             | 48 |

|   |       | 3.2.4   |                                                               | 48 |

|   |       | 3.2.5   | Tooling                                                       | 49 |

|   | 3.3 | CPU I   | Model                                      | 50       |

|---|-----|---------|--------------------------------------------|----------|

|   |     | 3.3.1   | Memory Hierarchy                           | 50       |

|   |     | 3.3.2   |                                            | 51       |

| 4 | ۵nn | licatio | n-Transparent NVM Wear-Leveling            | 53       |

| 7 | 4.1 |         |                                            | 54       |

|   | 4.2 |         |                                            | 55       |

|   | 7.2 |         |                                            | 55       |

|   |     | 4.2.2   |                                            | 56       |

|   |     | 4.2.2   |                                            | 57       |

|   | 4.3 |         | 5                                          | 57       |

|   | 4.3 | 4.3.1   | 5                                          | 57       |

|   |     | 4.3.1   | •                                          | 50<br>58 |

|   |     |         |                                            |          |

|   |     | 4.3.3   | 5                                          | 59       |

|   |     | 4.3.4   | 5                                          | 63       |

|   |     | 4.3.5   |                                            | 66       |

|   |     | 4.3.6   |                                            | 70       |

|   | 4.4 |         | , 3                                        | 70       |

|   |     | 4.4.1   |                                            | 71       |

|   |     | 4.4.2   |                                            | 71       |

|   |     | 4.4.3   |                                            | 72       |

|   |     | 4.4.4   |                                            | 74       |

|   |     | 4.4.5   |                                            | 78       |

|   | 4.5 | Concl   | uding Interface Exploitation               | 78       |

| 5 | Арр | licatio | n-Cooperative NVM Wear-Leveling            | 79       |

|   | 5.1 | Mode    | rn Technologies and Traditional Interfaces | 80       |

|   | 5.2 | Overv   | 'iew                                       | 80       |

|   |     | 5.2.1   | Application-Cooperative Decisions          | 81       |

|   |     | 5.2.2   | Application-Cooperative Actions            | 82       |

|   | 5.3 |         |                                            | 82       |

|   |     |         |                                            | 83       |

|   |     | 5.3.2   |                                            | 83       |

|   |     | 5.3.3   |                                            | 84       |

|   |     | 5.3.4   |                                            | 85       |

|   |     | 5.3.5   | 5                                          | 86       |

|   |     | 5.3.6   |                                            | 89       |

|   | 5.4 |         |                                            | 90       |

|   |     | 5.4.1   |                                            | 90       |

|   |     | 5.4.2   |                                            | 91       |

|   |     | 5.4.3   |                                            | 92       |

|   |     | 5.4.4   | -                                          | 92       |

|   |     | 5.4.5   |                                            | 95       |

|   |                                               | 5.4.6                                                                                                                                | Wrap-Up                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 98                                                                                      |

|---|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|   | 5.5                                           |                                                                                                                                      | uding Software-Based Wear-Leveling                                                                                                                                                                                                                                                                                                                                                                                                                        | 98                                                                                      |

| 6 | Men                                           | nory O                                                                                                                               | ptimization for Random Forests                                                                                                                                                                                                                                                                                                                                                                                                                            | 101                                                                                     |

|   | 6.1                                           | Mode                                                                                                                                 | rn Technologies and Traditional Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                | 102                                                                                     |

|   | 6.2                                           | Overv                                                                                                                                | iew                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 103                                                                                     |

|   | 6.3                                           | Unifie                                                                                                                               | d Layout Optimization of DECISION TREES (DTs) on Racetrack                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                         |

|   |                                               | Memo                                                                                                                                 | ry                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 104                                                                                     |

|   |                                               | 6.3.1                                                                                                                                | Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 104                                                                                     |

|   |                                               | 6.3.2                                                                                                                                | Problem Analysis and Statement                                                                                                                                                                                                                                                                                                                                                                                                                            | 105                                                                                     |

|   |                                               | 6.3.3                                                                                                                                | BLOwing Trees                                                                                                                                                                                                                                                                                                                                                                                                                                             | 106                                                                                     |

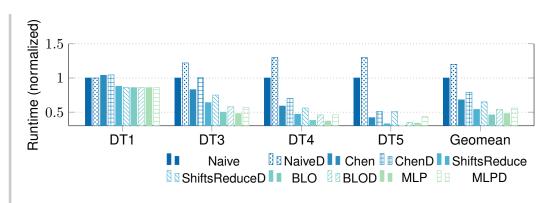

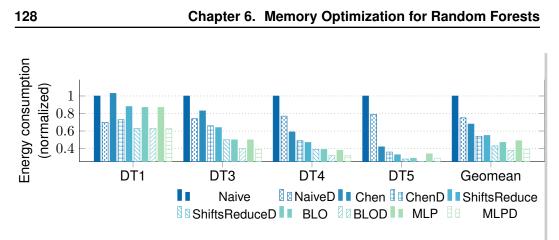

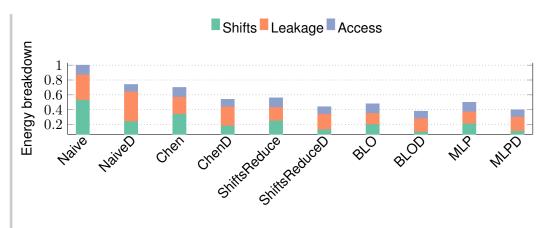

|   |                                               | 6.3.4                                                                                                                                | Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                | 112                                                                                     |

|   |                                               | 6.3.5                                                                                                                                | Wrap-Up                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 115                                                                                     |

|   | 6.4                                           |                                                                                                                                      | nposed Layout Optimization of DTs on Racetrack Memory                                                                                                                                                                                                                                                                                                                                                                                                     | 115                                                                                     |

|   |                                               | 6.4.1                                                                                                                                | Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 116                                                                                     |

|   |                                               | 6.4.2                                                                                                                                | Problem Analysis and Statement                                                                                                                                                                                                                                                                                                                                                                                                                            | 116                                                                                     |

|   |                                               | 6.4.3                                                                                                                                | Decomposed Tree Optimization                                                                                                                                                                                                                                                                                                                                                                                                                              | 118                                                                                     |

|   |                                               | 6.4.4                                                                                                                                | Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                | 124                                                                                     |

|   |                                               | 6.4.5                                                                                                                                | Wrap-Up                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 129                                                                                     |

|   | 6.5                                           | Concl                                                                                                                                | uding Memory Optimization of Random Forests                                                                                                                                                                                                                                                                                                                                                                                                               | 130                                                                                     |

|   |                                               |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                         |

| 7 | CPU                                           | J Optin                                                                                                                              | nization for Random Forests                                                                                                                                                                                                                                                                                                                                                                                                                               | 131                                                                                     |

| 7 | 7.1                                           | Mode                                                                                                                                 | rn Technologies and Traditional Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                | 132                                                                                     |

| 7 |                                               | Mode                                                                                                                                 | rn Technologies and Traditional Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                | 132<br>133                                                                              |

| 7 | 7.1                                           | Mode                                                                                                                                 | rn Technologies and Traditional Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                | 132<br>133<br>133                                                                       |

| 7 | 7.1<br>7.2                                    | Moder<br>Overv<br>7.2.1<br>7.2.2                                                                                                     | rn Technologies and Traditional Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                | 132<br>133<br>133<br>134                                                                |

| 7 | 7.1                                           | Moder<br>Overv<br>7.2.1<br>7.2.2<br>Immed                                                                                            | rn Technologies and Traditional Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                | 132<br>133<br>133<br>134<br>136                                                         |

| 7 | 7.1<br>7.2                                    | Moder<br>Overv<br>7.2.1<br>7.2.2<br>Immed<br>7.3.1                                                                                   | rn Technologies and Traditional Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                | 132<br>133<br>133<br>134<br>136<br>136                                                  |

| 7 | 7.1<br>7.2                                    | Moder<br>Overv<br>7.2.1<br>7.2.2<br>Immed<br>7.3.1<br>7.3.2                                                                          | rn Technologies and Traditional Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                | 132<br>133<br>133<br>134<br>136<br>136<br>136                                           |

| 7 | 7.1<br>7.2                                    | Moder<br>Overv<br>7.2.1<br>7.2.2<br>Immed<br>7.3.1<br>7.3.2<br>7.3.3                                                                 | rn Technologies and Traditional Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                | 132<br>133<br>133<br>134<br>136<br>136<br>136<br>136<br>140                             |

| 7 | 7.1<br>7.2                                    | Moder<br>Overv<br>7.2.1<br>7.2.2<br>Immed<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4                                                        | rn Technologies and Traditional Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                | 132<br>133<br>134<br>136<br>136<br>136<br>136<br>140<br>142                             |

| 7 | <ul><li>7.1</li><li>7.2</li><li>7.3</li></ul> | Moder<br>Overv<br>7.2.1<br>7.2.2<br>Immed<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5                                               | rn Technologies and Traditional Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                | 132<br>133<br>133<br>134<br>136<br>136<br>136<br>136<br>140                             |

| 7 | 7.1<br>7.2                                    | Moder<br>Overv<br>7.2.1<br>7.2.2<br>Immed<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>FLInt:                                     | rn Technologies and Traditional Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                | 132<br>133<br>134<br>136<br>136<br>136<br>140<br>142<br>147                             |

| 7 | <ul><li>7.1</li><li>7.2</li><li>7.3</li></ul> | Moder<br>Overv<br>7.2.1<br>7.2.2<br>Immed<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>FLInt:<br>Rando                            | rn Technologies and Traditional Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                | 132<br>133<br>134<br>136<br>136<br>136<br>140<br>142<br>147                             |

| 7 | <ul><li>7.1</li><li>7.2</li><li>7.3</li></ul> | Moder<br>Overv<br>7.2.1<br>7.2.2<br>Immed<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>FLInt:<br>Rando<br>7.4.1                   | rn Technologies and Traditional Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                | 132<br>133<br>134<br>136<br>136<br>136<br>140<br>142<br>147<br>148<br>148               |

| 7 | <ul><li>7.1</li><li>7.2</li><li>7.3</li></ul> | Moder<br>Overv<br>7.2.1<br>7.2.2<br>Immed<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>FLInt:<br>Rando<br>7.4.1<br>7.4.2          | rn Technologies and Traditional Interfaces<br>iew                                                                                                                                                                                                                                                                                                                                                                                                         | 132<br>133<br>134<br>136<br>136<br>136<br>140<br>142<br>147                             |

| 7 | <ul><li>7.1</li><li>7.2</li><li>7.3</li></ul> | Moder<br>Overv<br>7.2.1<br>7.2.2<br>Immed<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>FLInt:<br>Rando<br>7.4.1                   | rn Technologies and Traditional Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                | 132<br>133<br>134<br>136<br>136<br>136<br>140<br>142<br>147<br>148<br>148               |

| 7 | <ul><li>7.1</li><li>7.2</li><li>7.3</li></ul> | Moder<br>Overv<br>7.2.1<br>7.2.2<br>Immed<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>FLInt:<br>Rando<br>7.4.1<br>7.4.2          | rn Technologies and Traditional Interfaces         iew         Numeric Formats         Memory Encoding and Hierarchy         diate Encoding of Floating-Point Split Values         Scope         Problem Analysis and Statement         Immediate Encoding         Evaluation         Wrap-Up         Exploiting Floating-Point Enabled Integer Arithmetic for Efficient         om Forest Inference         Scope         Problem Analysis and Statement | 132<br>133<br>134<br>136<br>136<br>136<br>140<br>142<br>147<br>148<br>148<br>148<br>149 |

| 7 | <ul><li>7.1</li><li>7.2</li><li>7.3</li></ul> | Moder<br>Overv<br>7.2.1<br>7.2.2<br>Immed<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>FLInt:<br>Rando<br>7.4.1<br>7.4.2<br>7.4.3 | rn Technologies and Traditional Interfaces<br>iew                                                                                                                                                                                                                                                                                                                                                                                                         | 132<br>133<br>134<br>136<br>136<br>136<br>140<br>142<br>147<br>148<br>148<br>149<br>149 |

ix

| 8  | Con          | clusion | and Fu | utur | e١ | No  | rk |  |   |   |     |   |   |   |     |   |   |   |   |     |   |   |   |       |   |   |   | 165 |

|----|--------------|---------|--------|------|----|-----|----|--|---|---|-----|---|---|---|-----|---|---|---|---|-----|---|---|---|-------|---|---|---|-----|

|    | 8.1          | Conclu  | sion   |      |    |     |    |  |   |   |     |   |   |   |     |   |   |   |   |     |   |   |   |       |   |   |   | 166 |

|    |              | 8.1.1   | Summa  | ary  |    |     |    |  |   |   |     | • |   |   |     |   |   |   |   |     |   |   |   |       |   |   |   | 166 |

|    |              | 8.1.2   | Outrea | ch.  |    |     |    |  |   |   |     |   |   |   |     |   |   |   |   |     |   |   |   |       |   |   |   | 167 |

|    | 8.2          | Future  | Work . | •••  | •  | • • | •  |  | • | • | • • | • | • | • | • • | • | • | • | • | • • | • | • | • | <br>• | • | • | • | 168 |

| Ac | rony         | ms      |        |      |    |     |    |  |   |   |     |   |   |   |     |   |   |   |   |     |   |   |   |       |   |   |   | 171 |

| Bi | Bibliography |         |        |      |    |     |    |  |   |   | 173 |   |   |   |     |   |   |   |   |     |   |   |   |       |   |   |   |     |

# CHAPTER 1 Introduction

### Contents

| 1.1 | Explo | iting Traditional Interfaces                                  | 3  |

|-----|-------|---------------------------------------------------------------|----|

|     | 1.1.1 | Relevance to the Research Community                           | 4  |

|     | 1.1.2 | Interface Exploitation for NON-VOLATILE MEMORY (NVM) Lifetime | 5  |

|     | 1.1.3 | Interface Exploitation for RACETRACK MEMORY (RTM) Properties  | 6  |

|     | 1.1.4 | Interface Exploitation for Immediate Arithmetic               | 6  |

| 1.2 | Contr | ibution of this Work                                          | 7  |

|     | 1.2.1 | Application Transparent NVM Wear-Leveling                     | 8  |

|     | 1.2.2 | Application Cooperative NVM Wear-Leveling                     | 9  |

|     | 1.2.3 | Memory Optimization for Random Forests                        | 11 |

|     | 1.2.4 | CPU Optimization for Random Forests                           | 13 |

| 1.3 | Orgar | nization of the Thesis                                        | 15 |

| 1.4 | Autho | r's Contribution to this Thesis                               | 15 |

## "

We're on the cusp of another Golden Age that will significantly improve cost, performance, energy, and security. [...] We've identified areas that are critical to this new age: 1) Hardware/Software Co-Design for High-Level and Domain-Specific Languages [...]

"

#### John Hennessy and David Patterson [HP18]

Computer Science as a domain features multiple properties, which are unique to this discipline. Two of these properties are 1) the rapid and disruptive development of modern technologies [LR03] and 2) the extensive use of traditional abstractions in order to allow managing the complexity of the evolving computer systems [CS07].

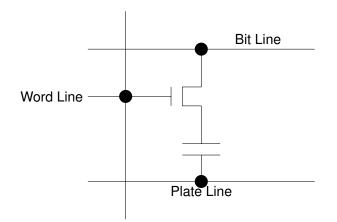

While tens of years ago, tape drives, spinning hard disks and megabyte-sized main memory without deep cache hierarchies formed the standard of the memory subsystem of a computer system, as of the time of this thesis, terabyte-sized, complex main memory with hundreds of megabytes sized cache hierarchies, quantum effect storage devices and mass data backup facilities in the form of SOLID STATE DRIVE (SSD) clusters are a standard to computing applications. Active research interest promises disruptive technology changes in a similar scope in the future. Integration densities, which would have been considered impossible a few years ago, in memory and even in memory material computing, even larger memory capacities and amounts of computing cores are promising to show up within the next years. Also shifting the focus away from the development in hardware technologies towards modern software technologies, disruptive changes are visible over the recent years. While algorithmic research, complexity analysis and the design of efficient problem-solving strategies belong together with computers since their beginning of existence, other application types, such as resource-demanding machine-learning estimators, error-tolerant algorithms and even complex management schemes inside operating systems belong to the standard set of applications nowadays.

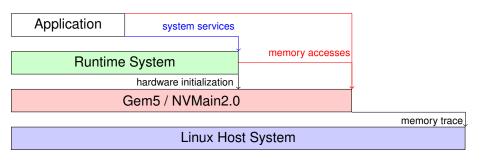

On the other hand, studying abstractions and the creation of interfaces of computing systems, reveals a contrary development speed, compared to disrupting technologies. Consider, for instance, the memory interface of computers. In the Von-Neumann architecture, memory plays a central role to store code and data memory. Consequently, INSTRUCTION SET ARCHITECTURES (ISAs) formed a simple abstraction of memory accesses years ago. They provide load and store instructions, which specify a memory location to load from or store to. Modern computers offer still the same interface for software to access the memory. On both sides of this interface, modern technologies are applied by introducing further levels of abstractions. For instance, considering memory hierarchies, memory accesses caused by the application are not redirected to the memory device directly, but rather go through the various levels of caches upfront. Also,

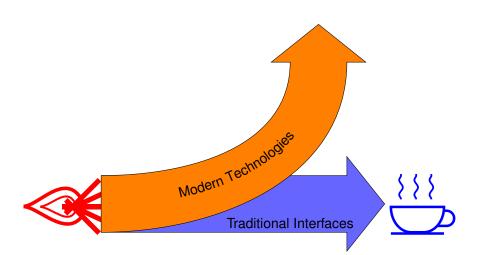

Figure 1.1: Development of Technologies and Interfaces

from the perspective of applications, neural networks are seldom implemented directly by computing memory addresses and doing load and store operations to these addresses. Instead, levels of abstraction are put on top of the basic software interface, which allow implementation in object-oriented or scripting based languages. As highlighted in the opening quote of this section, Hennessy and Patterson identify the co-design between hardware and software innovations as one core challenge of the current "golden age" [HP18].

From the previously mentioned aspects, it can be noted that the development of modern technologies, including hardware and software development, is skyrocketing into new spheres in the past and most probably also in the near future. The basic interfaces, however, which connect modern technologies with each other and probably also with not that modern technologies, keep crawling on the ground and remain largely unaffected by the technological development. Bringing both worlds together remains as an open challenge. It should be clarified, that this thesis does not focus on methods against this uneven development, but rather studies the need to effectively make use of the existing interfaces, in other words to exploit traditional interfaces in order to operate modern technologies in computer systems.

### 1.1 Exploiting Traditional Interfaces

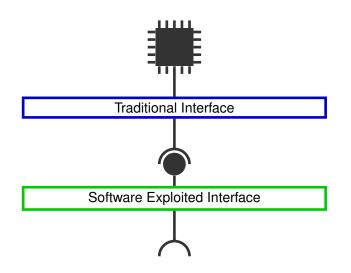

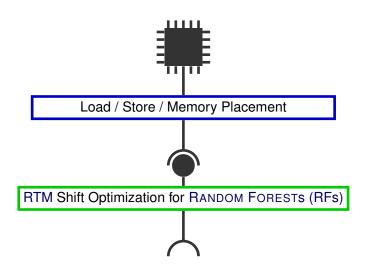

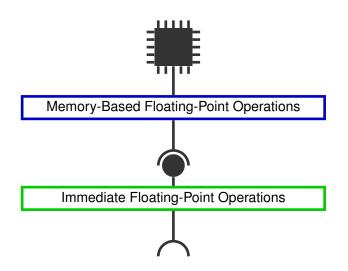

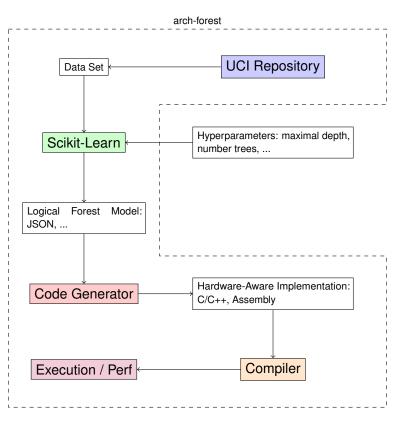

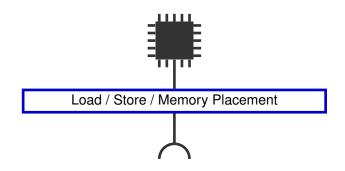

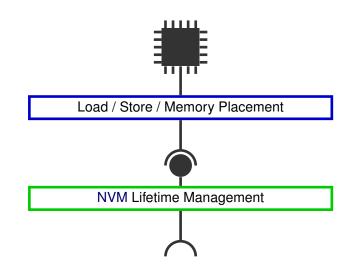

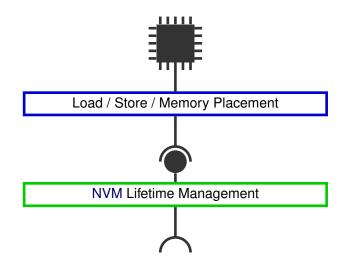

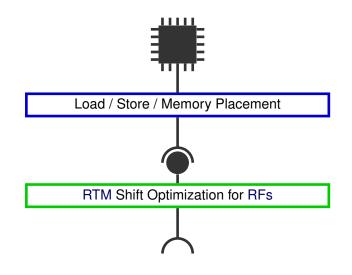

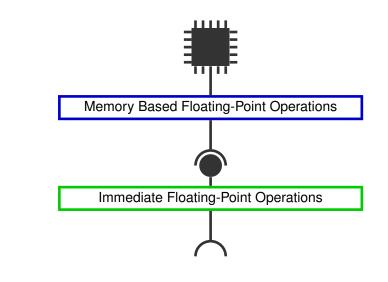

As the landscape of technology is massively large, this thesis does not aim to provide universal solutions, but rather focuses on specific technologies and specific interfaces and contributes methods for the explicit exploitation of the relevant interfaces. The following illustration highlights the basic principle behind every contribution of this thesis and can be found in a more specific version in the corresponding chapters.

Given that certain technologies are available, indicated by the illustration of a chip with pins, traditional interfaces exist to use these technologies. In order to properly operate the technologies, a broader interface is required. One way to provide such an extended interface is to employ special software solutions, which exploit the existing interface and on their own provide a broadened, software exploited interface. This then can be used by target applications to operate the modern technology.

#### 1.1.1 Relevance to the Research Community

As of the time of this thesis, research efforts are actively conducted explicitly into the direction of software exploitation of interfaces for modern technologies. This thesis puts a major focus on disruptive memory technologies and the required management to operate them efficiently and effectively. In a more specific scope, this is a defined target of the DFG (Deutsche Forschungsgemeinschaft) Project Design and Optimization of Non-Volatile One-Memory Architecture (NVM-OMA)<sup>1</sup>. The concept behind this project is to develop solutions for a unified memory landscape, consisting of NVM only, which is one type of disruptive memory. This project aims to provide software based solutions and hence enable the software management of NVMs. Beyond specific software management of NVMs, there is active research interest in disruptive memory technologies itself. In the scope of a special priority program, the DFG conducts a number of research projects to actively pursue research on disruptive memory. This program can be found under the number SPP 2377<sup>2</sup>. Specifically, the project Memory Diplomat<sup>3</sup> is dedicated to the development of extended technology interfaces. The core idea of this project is to develop a central software instance, the so-called memory diplomat, which has knowledge about applications and the hardware and can negotiate required management strategies. The memory diplomat further contains extension and exploitation means

<sup>&</sup>lt;sup>1</sup>https://gepris.dfg.de/gepris/projekt/405422836

<sup>&</sup>lt;sup>2</sup>https://gepris.dfg.de/gepris/projekt/460954224

<sup>&</sup>lt;sup>3</sup>https://gepris.dfg.de/gepris/projekt/502384507

to manage the hardware. These extensions in this project are entirely achieved by a central software instance. In consequence, the contributions from this thesis align with the declared target of such existing research efforts.

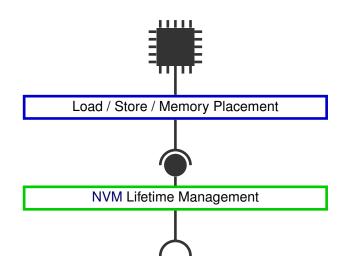

#### 1.1.2 Interface Exploitation for NVM Lifetime

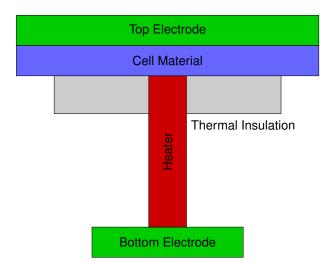

Bringing a clearer focus to the technologies and topics, addressed by this thesis, one relevant technology is NON-VOLATILE MEMORY (NVM). Although many different hardware technologies behind NVM exist and also many special characteristics are caused by these technologies, this thesis picks up a central issue, which is common to many of these technologies, namely the lifetime issue. Due to technical properties of different memory materials used for NVM, they can break after a comparably low amount of memory accesses. Without active lifetime maintenance, the memory would endure for a few months only. This is mainly caused by the fact that executing software tends to use some memory portions more often than other portions. Hence, although the total volume of accesses may not be very high, the intensively used memory portions can break early. On the other hand, this behavior allows a significant extension of NVM lifetime, when the memory accesses are well distributed. The process of achieving such a distribution is called wear-leveling.

From the perspective of interfaces used for emerging NVM technologies, the basic memory interface has to be considered as a baseline. In order to properly operate the process of wear-leveling, two extensions to the interface should be considered: 1) the possibility to determine current memory wear-out and 2) the possibility to redirect memory accesses to other portions. Although it is not crucially necessary to know the current state of the memory and how much lifetime is left per memory portion, it can help to pursue a further optimized utilization of the memory. Extracting information about the current memory aging over the traditional memory interface is not possible due to its focus of loading and storing memory requests. If software aims to exploit this interface and keep track of the memory lifetime internally, a straightforward approach is to hook into memory accesses directly from a software level and maintain an internal model of the aging of memory portions. Hooking into memory accesses by software is challenging, since the default design of computers does not provide standard means to achieve this. Consequently, appropriate solutions are required. Either a combination of other available technologies and interfaces is used in order to achieve the required goal, or the application is modified in order to hook into memory accesses. Both directions are explored in this thesis.

The interface extensions of being able to redirect the target of memory accesses can be approached from similar directions. Either, other existing means and interfaces are combined in a creative way to redirect memory accesses, or the application is again modified in order to achieve this. Both directions are explored, partially in an overlay manner in this thesis. It should be noted that of course a large research community explores possibilities to directly change the traditional memory interface in order to achieve the management of NVM regarding their lifetime. Such approaches can usually gain a high efficiency, especially when additional hardware controllers are introduced into the system. This thesis, however, aims for another research direction and aims to provide alternatives, namely the software exploitation of interfaces. Following both of these research directions opens a larger design space for creation of future computing systems.

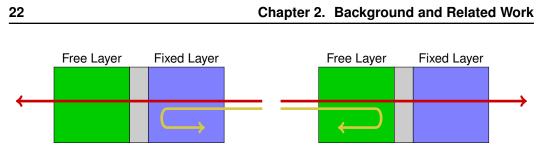

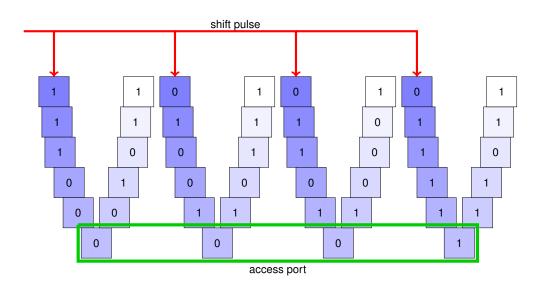

#### 1.1.3 Interface Exploitation for RTM Properties

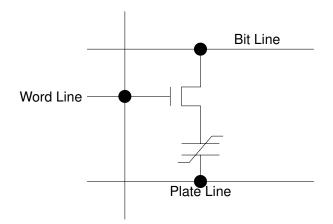

One special type of NVM, which comes with unique shift properties, is RACETRACK MEMORY (RTM) [BKF+20]. RTM is organized in a way, that memory contents are stored at adjacent physical locations, but only one of the locations can be read or written. When a specific element of the memory should be accessed, the memory positions have to be moved towards the access port first. This operation is called *shift*. Naturally, shifts take time and also cause an impact on the energy consumption of the memory. These effects correlate to the distance of a shift. That is, the more memory positions have to be skipped upfront to an access, the more latency and energy overhead is caused. The previous position of the memory depends on the previous access. Hence, the latency and energy consumption of RTM is access sequence dependent.

Towards interface extensions, the caused overhead for shift operations requires a mechanism to be controlled by the running software. This can be achieved by offering interface extensions to specify the location of memory elements, which essentially allows gaining control over the memory access sequence. Broadening the traditional memory interface towards such a behavior by software can be potentially achieved in applications themselves. For example, applications can utilize data structures, which are constructed by pointers between single elements of the data structure. This allows to change the actual physical location of single data structure elements and keeping the view from the application on the logical correctness of the data structure untouched. In this thesis, tree-based data structures are considered as such a controllable data structure. In addition to the action space of controlling the memory access sequence, a second extension to the interface is required, i.e. an extension allowing to decide for a good reordering of the memory access sequence. One possible approach is to formulate a cost model for the cause latency and energy overhead. This cost model then can be used as an objective function for optimization. Execution-specific behavior, i.e. knowing which memory elements are accessed subsequently, are crucial to create such a cost model. Since this thesis focuses on an application-specific interface extension, an application-specific cost model is derived for DECISION TREE (DT) applications.

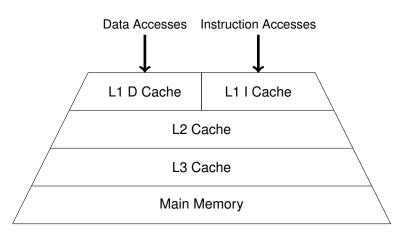

#### 1.1.4 Interface Exploitation for Immediate Arithmetic

Beyond concrete NVM technologies, considering a generic concept of memory hierarchies and the efficient utilization of system caches, immediate arithmetic becomes an interesting aspect. In modern memory hierarchies, instruction memory and data memory can be separated in the high cache levels. That means, instruction memory accesses, i.e. accesses to encoded instructions target a different portion from the system cache than data memory accesses. If applications now explicitly want to optimize their cache behavior, controlling the amount of accessed to data and instruction memory can be a desirable mechanism. Immediate encoding of constants, i.e. storing numeric values directly in the immediate field of instructions offers a mechanism to move stored values from data memory to instruction memory and vice versa. Traditional ISAs, however, only offer such a possibility for integer numeric values.

With the rise of MACHINE LEARNING (ML) applications into various classes of computing systems, spanning a range from embedded low-power systems up to higher performance systems, also the need to intensive floating-point arithmetic arises in these systems. If a target data set is provided with floating-point numeric values, the MACHINE LEARNING (ML) model has to include floating-point arithmetic at a certain level to properly reflect this data set. Consequently, ML models can be forced to rely on intensive floating-point arithmetic. It is also a desirable target to optimize the cache utilization of ML models, which can be assisted by the option for immediate encoding. Consequently, in order to broaden the traditional interface for this case, immediate encoding for floating-point arithmetic should be enabled. Achieving this in a software extension of the interface is not entirely intuitive, since floating-point arithmetic is usually hardware based. Hence, this thesis explicitly studies the comparison operation of floating-points (e.g.  $\geq$ ), which is the only operation required for DECISION TREE (DT) models and ensembles and provides software based solutions to offer immediate encoding.

### 1.2 Contribution of this Work

This thesis addresses the problem of software exploitation of traditional interfaces for specific modern technologies and applications. For concrete cases, methods are proposed, studied, and evaluated, which can offer an extended interface to allow an effective operation of the considered technology. As highlighted before, these methods do not aim to be universally applied or to dominate other solutions, but rather to provide alternative options, which are based on a software exploitation of the interface. The first two topical chapters of this thesis (Chapter 4 and Chapter 5) pick up the lifetime issue of NVM. The basic extensions, which need to be added to the memory interface, follow the purpose to handle lifetime issues. The third topical chapter (Chapter 6) picks up RTM as a specific technology and discusses interface extensions for effective latency and energy management of this memory technology. The last topical chapter (Chapter 7) picks up the possibility for immediate encoding for floating-point values.

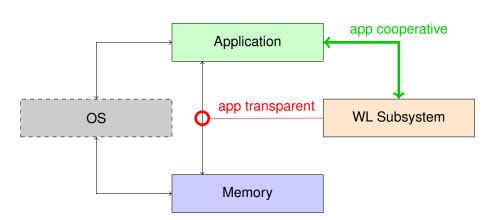

#### 1.2.1 Application Transparent NVM Wear-Leveling

The first type of NVM lifetime management, considered in this thesis is application transparent wear-leveling (Chapter 4). In this scope, applications remain untouched and the required steps for wear-leveling are conducted in a software-based manner outside the applications. The suitable target, consequently, is the operating system and the system software in order to realize wear-leveling functionality:

Wear-leveling requires two basic components: 1) extracting information about the remaining lifetime of certain memory portions and 2) redirecting the physical target location of memory accesses in order to level the utilization of lifetime across the entire memory space.

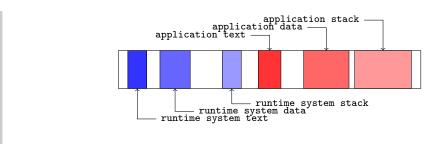

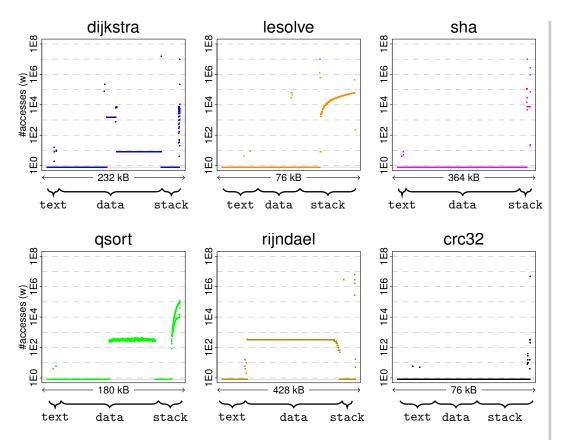

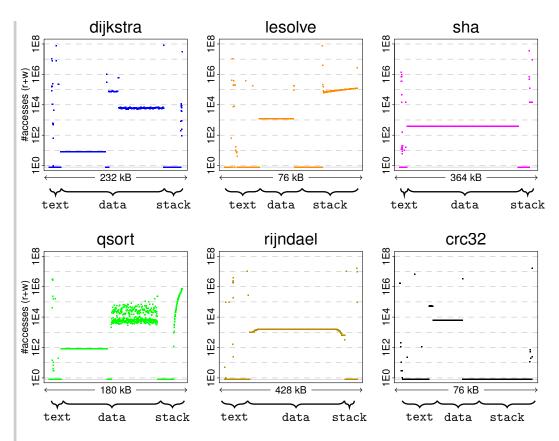

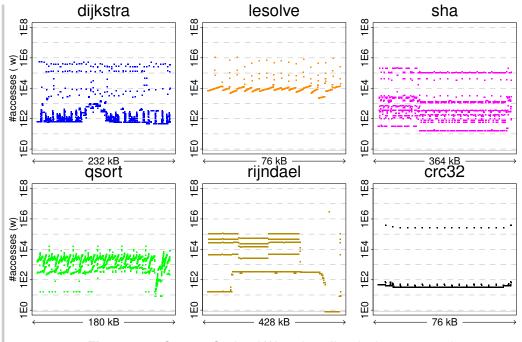

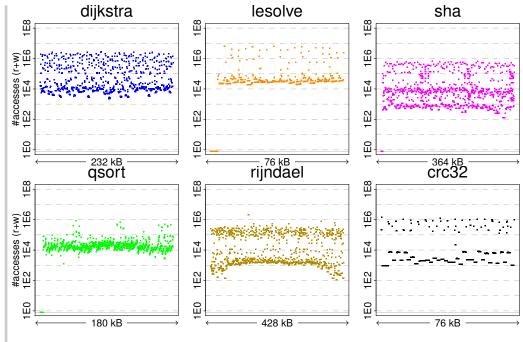

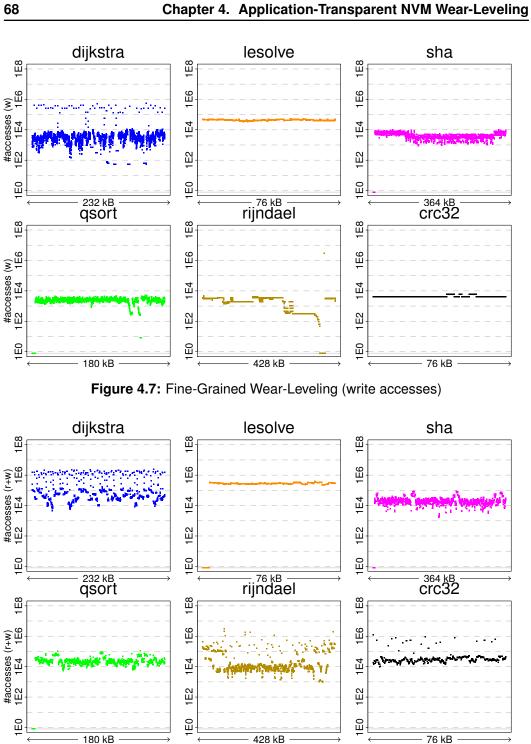

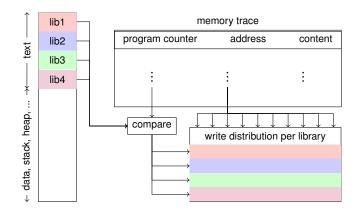

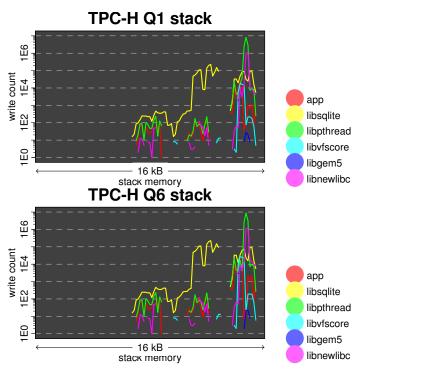

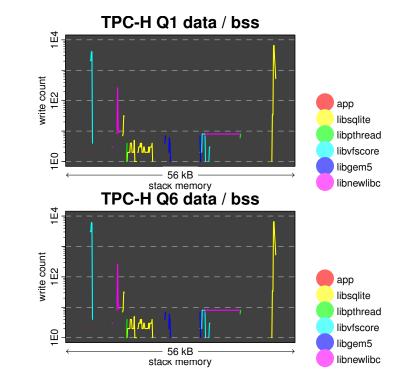

Towards the component of extracting information, this thesis introduces two orthogonal approaches. In the first approach, existing functionality of modern CPUs is creatively reused. Performance counters, which can count certain hardware events, are used to count the number of read and write accesses in the system. An interrupt mechanism is used to trigger a system interrupt after a specified number of memory accesses. With the help of memory access permissions in the MEMORY MANAGEMENT UNIT (MMU), the target of the next memory access is recorded. This is achieved by forbidding access to the entire memory, such that the subsequent access causes a memory access violation, which delivers the violated address to the interrupt handler. Afterwards, the default state is restored. In consequence, this method provides a sampled histogram of memory accesses, which serves as an estimation of the memory wear-out, caused by the running software. Accumulating the histogram over time provides an estimation about the remaining memory lifetime. In addition to this methodology, the thesis introduces semantic enrichment of the collected information. The target application is deployed to a modular unikernel, which allows extraction of the relation of the binary layout to single components of the unikernel. This can then be used to enrich the previously collected memory access information with knowledge about the unikernel component. Wear-leveling can then be targeted to specific components. The semantic enrichment is achieved with a static tracing methods, which analyzes the binary memory layout of the entire kernel instance and a dynamic tracing method, which checks the current PROGRAM COUNTER (PC) during the execution of a memory access to determine the corresponding component.

Towards the redirection of memory accesses, this thesis also introduces two orthogonal approaches. These two approaches operate on a different target granularity, making them naturally combinable. For coarse granularities, MMU page tables are modified in order to redirect memory accesses to the virtual address space to other physical locations. By copying the data also to the corresponding new physical location, application transparency is achieved. For fine granularities, the text and stack segments of the running program are modified. Both are moved in fine-grained steps through the memory and therefore the accesses to these segments are distributed across the physical memory space. Position-independent code ensures the application transparency for the text segment. Stack pointer relative addressing ensures the application transparency for the stack segment.

The combination of both components is also implemented in the form of an intuitive wear-leveling algorithm in this thesis. It should be, however, noted that the design of a wear-leveling strategy is not within the scope of this thesis. The focus of this work is on providing methods in software to exploit the existing memory interface for wear-leveling strategies. In short, the contributions for application-transparent wear-leveling are summarized in the following:

#### Contributions: Applications Transparent NVM Wear-Leveling

- Online read and write approximation with performance counters and the MMU in order to derive a statistically approximated trace of real read and write accesses of the application during runtime.

- Coarse-grained aging-aware wear-leveling, utilizing the approximate read and write trace to execute replacement operations with the virtual to physical memory mapping of the MMU.

- Fine-grained non aging-aware wear-leveling, operating on the stack memory for read and write accesses and on the text memory for read accesses.

- Static memory tracing, utilizing compiler information from a unikernel to map the binary layout of the compiled unikernel to the single included libraries.

- Dynamic memory tracing to further provide a semantic association of memory regions in the dynamically allocated memory segments to the corresponding library of the unikernel.

#### 1.2.2 Application Cooperative NVM Wear-Leveling

Based on the methods for application-transparent NVM wear-leveling, this thesis contributes with design approaches towards application-cooperative wear-leveling. The

interface extension targets the same functionality, but the methods to achieve this shift from the operating system and the system software into the application directly:

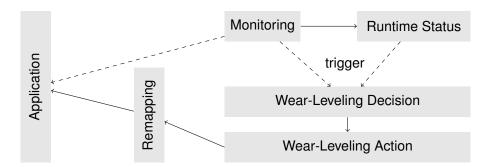

The advantage of achieving wear-leveling mechanisms in the application directly can be efficiency and effectiveness. However, this comes with the cost of tailoring the wear-leveling scheme specifically to a certain target application. This thesis follows two approaches, an application-cooperative wear-leveling scheme, which is not directly tied to any specific application, and the other approach specifically proposes a wear-leveling scheme for B<sup>+</sup> trees.

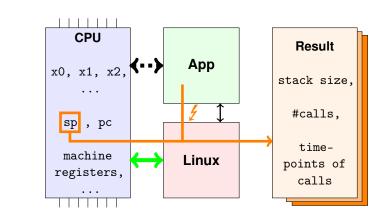

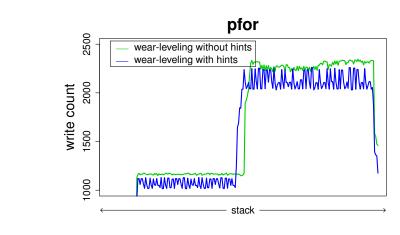

For the first approach of application-cooperative wear-leveling, without targeting specific applications, the focus is put on the stack memory. Stack memory, due to its usage for intermediate data, can be a significant driver for memory wear-out. Consequently, it is specifically focused. When deciding to move the target location of stack memory in application-transparent wear-leveling schemes, a certain overhead is caused for moving the relevant memory contents to a new position. This overhead can be not only noticed in the form of a time overhead, but also in the form of a lifetime overhead, since additional memory accesses are caused. Consequently, the amount of memory to be moved when the stack position is relocated should be minimized. The proposed method in this thesis employs a GENETIC ALGORITHM (GA) on offline-profiled stack behavior of a target application in order to identify optimized parts in the application code, to trigger a relocation of the stack memory. The determined relocation points are then fed back into the application source code in the form of special annotation, which notify the underlying operating system and the application transparent wear-leveling subsystem to cause a stack relocation.

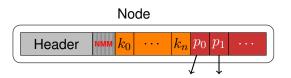

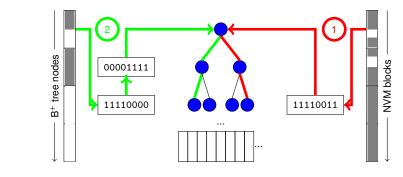

For the second approach for application-cooperative wear-leveling, this thesis proposes a wear-leveling scheme, dedicated for B<sup>+</sup> trees, which are used as an important component of database management systems. The collection of information about the memory usage and the impact on the lifetime of memory portions is directly performed in the tree operations themselves. Whenever the tree implementation touches a node, an access histogram is updated and maintained to keep track of memory modifications. In order to effectively utilize this histogram for wear-leveling, a checkpointing mechanism is explored in this thesis, where an entire checkpoint of the tree is written from volatile memory to NVM at the time of a checkpoint. The histogram is used to decide for a mapping of tree nodes to memory portions in the checkpoint. An efficient search algorithm is directly integrated to provide a fast heuristic solution to optimize the mapping for the checkpoint memory. In short, the contributions for application cooperative wear-leveling can be summarized as follows:

#### **Contributions: Application Cooperative NVM Wear-Leveling**

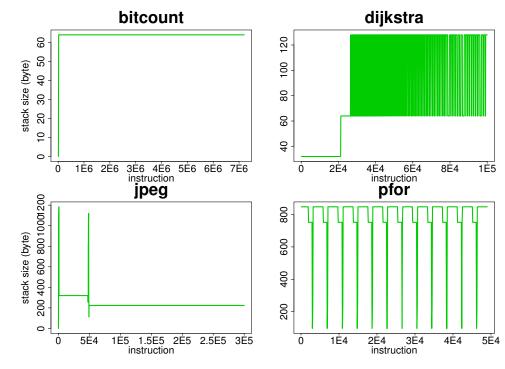

- A ptrace-based stack analysis-framework for stack-size recording of single instructions.

- A GENETIC ALGORITHM (GA) for finding instructions with low stack sizes.

- An annotation mechanism to trigger stack wear-leveling at specific instructions.

- A modified B<sup>+</sup>-tree implementation, which maintains modification information within tree nodes, which are updated in a lightweight manner during updates and inserts.

- A wear-leveling implementation, utilizing the collected modification information during checkpoints to apply a wear optimized mapping.

#### 1.2.3 Memory Optimization for Random Forests

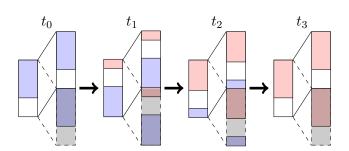

The third topical chapter of this thesis (Chapter 6) shifts the focus from the common property reduced lifetime for NVM memories towards a special type of NVM, namely RACETRACK MEMORY (RTM). RTMs feature a unique property of an access-dependent latency and energy consumption. The reason is that memory contents are stored in adjacent positions, but read and write operations can only be performed at the position of the access head. Contents, consequently need to be shifted to this access head upon an access first. The introduced overhead for latency and energy should be minimized in order to properly operate RTM memory. In the context of the exploitation of the memory interface, this requires gaining explicit control over the shift behavior in RTM:

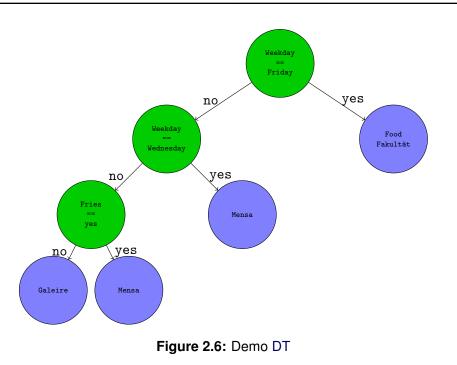

This interface exploitation requires two components: 1) the possibility to change locations of memory elements in order to influence the shift cost for access to this memory element and 2) the formulation of a cost model in order to apply an optimization algorithm. In this thesis, these two exploitation are realized as an application-specific solution for RANDOM FOREST (RF) ensembles.

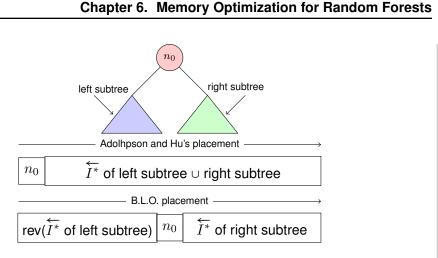

In the application-specific context of RANDOM FOREST (RF) ensembles, mainly focusing on the internal DTs, modifications of the memory positions of single elements can be achieved straightforward. Towards this, the implementation as native trees is considered, where DT nodes are realized as array elements and the child nodes are indicated by an index to the node array. When a node is mapped to an arbitrary position in the array, only the child pointers need to be adjusted accordingly. In this thesis, the RTM optimized layouting is done during the implementation time of the ensemble; hence the corresponding code can be generated directly.

The contribution of this chapter then focuses on deriving the cost model and the optimization of the layout with respect to this cost model. Towards the cost model, empirical branching probabilities are collected during the training time of the single DTs. Since ML applications in general assume the test data to stem from a similar distribution as the training data, the probabilities are considered to be accurate also during productive use. Starting from the relative branching probabilities, an absolute probability model is created, which indicates the probability to visit a node from its parent node. Together with the shifting distance from the parent to the node, this forms a cost model of the expected amount of shifts during inference of a DT. Leaving the position of each node as the solution space, the cost model can be interpreted as an optimization problem. This optimization problem can be formulated an instance of the quadratic assignment problem or an instance of the optimal linear order problem, which is NP hard and infeasible to be solved for larger DTs in tolerable time.

Due to the specific focus on DT models, a reduction of the problem complexity is possible. The optimal linear ordering problem can be solved in  $O(n \cdot \log n)$  for rooted tree models. The cost model for DTs on RTM is not exactly transferable to

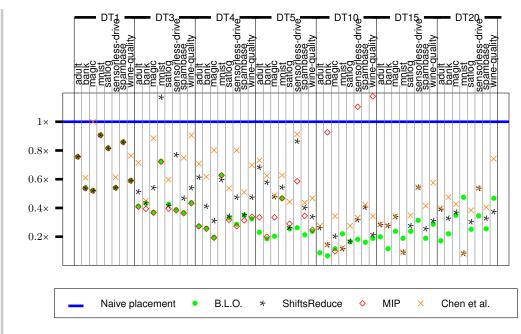

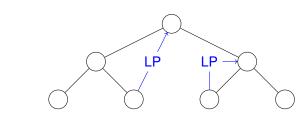

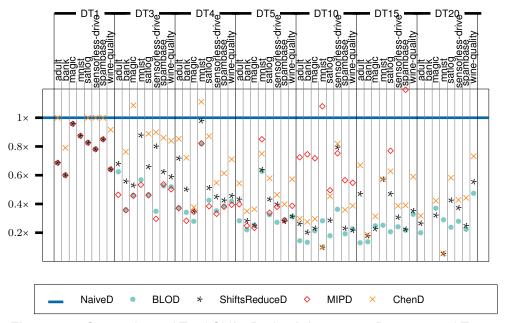

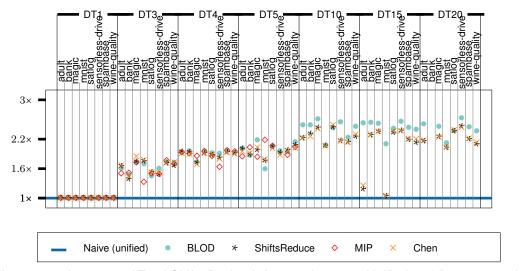

the rooted tree problem, but comes somewhat close. This thesis contributes a slightly modified version of the fast optimization algorithm and contributes a formal proof about the relation to the optimal solution. Towards this, two organization approaches are proposed: 1) tree nodes are entirely stored at one RTM position and 2) tree nodes are decomposed in three subcomponents and stored in individual clusters of the RTM. The formal proof guarantees an upper bound of  $4\times$  for the unified organization and  $12\times$  for the decomposed organization. Experimental evaluation even indicates that these upper bounds are pessimistic in most cases. In short, the contributions can be summarized as follows:

#### **Contributions: Memory Optimization for Random Forests**

- A formal cost model for shift overhead of racetrack memory in a unified and decomposed organization with respect to a probabilistic execution model is specified. This model is expressed as an INTEGER LINEAR PROGRAM (ILP), which allows for deriving the optimal solution, if the required time is spent.

- A fast optimization algorithm, which reduces the problem of DT layouting in RTM to an efficient solvable optimization problem. The algorithm is further modified for the specific characteristics of the studied problem.

- A formal proof of the upper bound of  $4\times$  for the unified organization and  $12\times$  for the decomposed organization for the fast optimization algorithm compared to the optimal solution.

#### 1.2.4 CPU Optimization for Random Forests

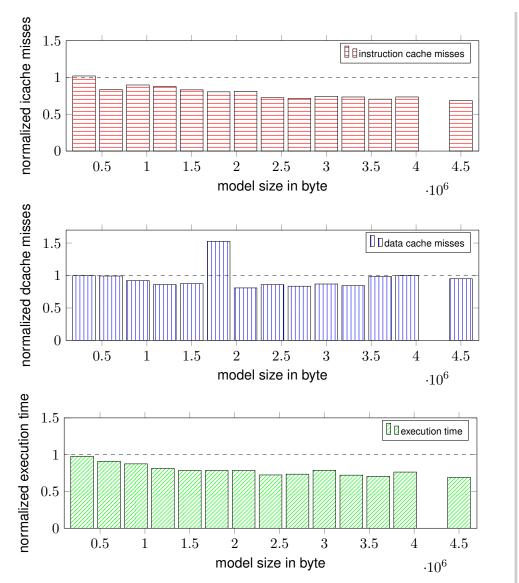

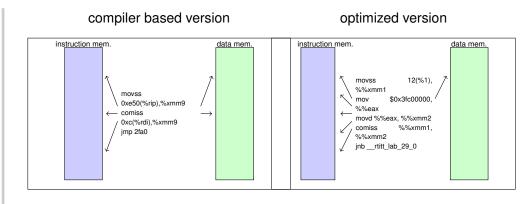

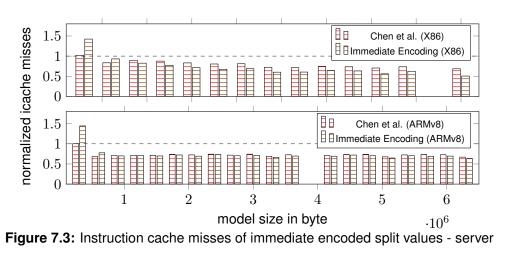

The last topical chapter of this thesis (Chapter 7) leaves the area of disruptive memory technologies and puts a focus on the design of the memory subsystem itself. The organization into memory hierarchies allows applications to optimize their memory behavior for performance optimization in a given memory hierarchy. As described above, distinguishing data and instruction memory can be an important knob to control the behavior in caches, since they are distributed into instruction and data caches usually in the highest cache levels. One way of gaining active control over this is to encode numeric values either in data memory or in the immediate field of instructions directly. For floating-point numerical values, this is not possible, consequently the software exploitation to enable this is considered here:

In this thesis, again specific solutions for RF ensembles are considered since cache optimization is a known desirable target for them. In addition, the arithmetic structure of DTs is very simple, allowing for creative solutions. This thesis follows two approaches in order to exploit existing immediate encoding to achieve immediate arithmetic for floating-point values. Firstly, a generic method is discussed, which is not directly bound to DTs. Secondly, a specific method is presented, which only enables the comparison operation for immediate floating-point numbers in a more effective manner.

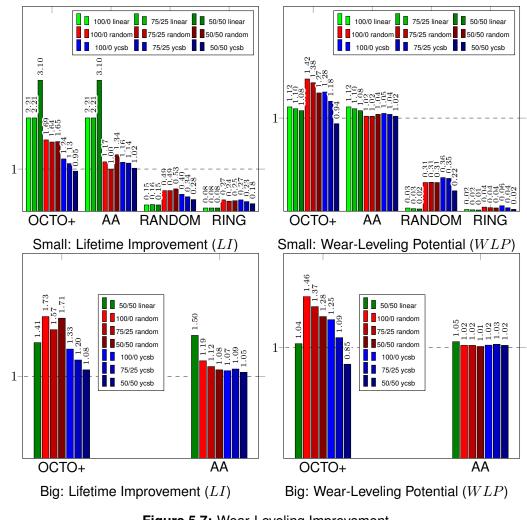

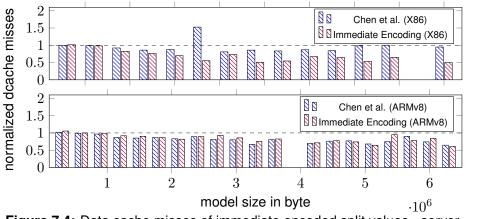

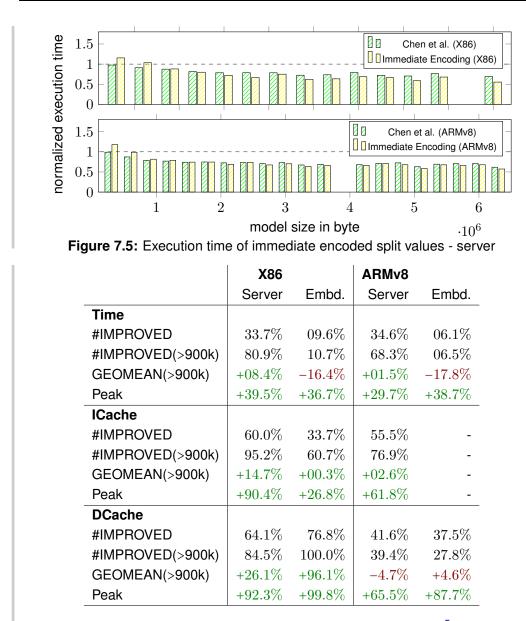

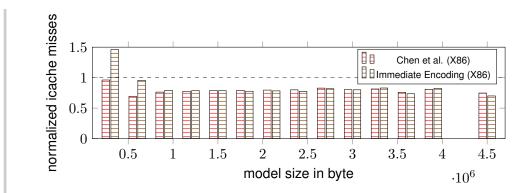

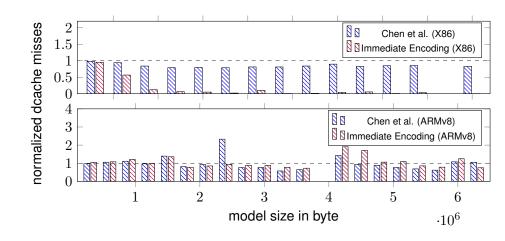

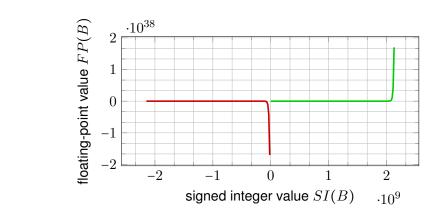

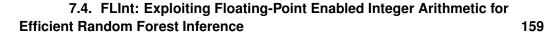

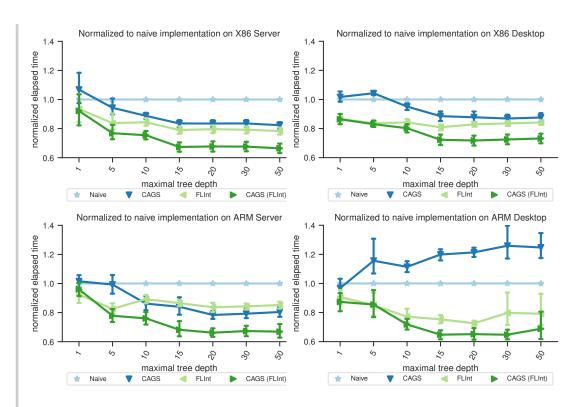

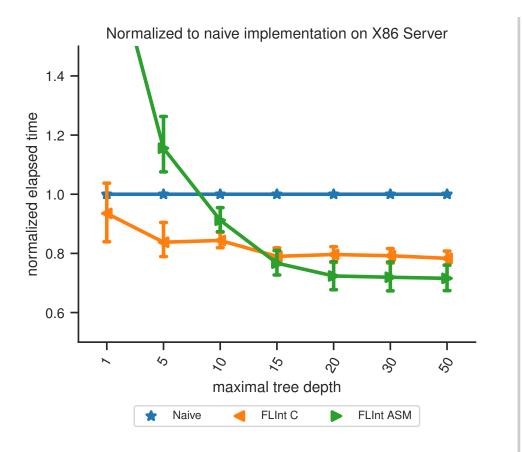

For the generic solution, the basic concept is to consider the binary representation of a floating-point number as a bit vector, which can also be interpreted as an integer number. This bit vector is then immediately encoded into a set of instructions. For instance, in a 32-bit architecture, instructions naturally cannot have 32-bit wide immediate fields. Therefore, a set of instructions is synthesized to load the 32-bit floating-point bit vector into a register from immediate encoded portions of the bit vector. Afterward, the integer register is copied bit by bit to a floating-point register without conversion, such that the number is available for arbitrary floating-point arithmetic. In consequence, only the load operation to a floating-point register, which would normally have to be done from data memory, is replaced by corresponding immediate encoded operations. This method has the advantage that afterward the number is present in a floating-point register and can serve for any type of floating-point computation.