# Dissertation zur Erlangung des akademischen Grades Dr. rer. nat.

## **MIBAD**

An FPGA-based readout system for the LHCb Beam Conditions Monitor

Martin Stefan Bieker

geboren am 19.10.1993 in Quakenbrück

Fakultät Physik Technische Universität Dortmund 2024

| Der Fakultät Physik der Technischen Universität Dortmund zur Erlangung des akader | nis- |

|-----------------------------------------------------------------------------------|------|

| chen Grades eines Doktors der Naturwissenschaften vorgelegte Dissertation.        |      |

Gutachter:

Prof. Dr. Johannes Albrecht PD Dr. Dominik Elsässer

Vorsitzender der Prüfungskommission: apl. Prof. Dr. Heinz Hövel

Vertreter der wissenschaftlichen Mitarbeiter: Prof. Dr. Zhe Wang

Datum der Einreichung der Dissertation: 14. Mai 2024

Datum der mündlichen Prüfung: 28. Juni 2024

### **Abstract**

Experiments at particle accelerators, such as the Large Hadron Collider (LHC), are at risk of damage due to the high-energy beams. The Beam Conditions Monitor (BCM) protects the LHCb detector at the LHC. It measures the particle flux with diamond sensors at two positions near the interaction point. If the measured signals exceed safe levels, the BCM automatically triggers a dump of the LHC beams.

The LHCb detector was upgraded from 2018 to 2022. Consequently, the BCM needed to be adapted to a five-fold increase in instantaneous luminosity and a new detector geometry. Moreover, the pre-existing BCM hardware card is no longer supported due to an experiment-wide replacement of the readout electronics.

This thesis presents the *Machine Interface Beam Abort Decision (MIBAD)* system as the BCM readout for the post-upgrade era. The development of the system, encompassing hardware, firmware, and software, is detailed. The main emphasis of this work is the implementation of the beam abort decision logic. As a vital part of the BCM safety system, the MIBAD continuously evaluates the beam conditions while meeting strict requirements regarding reliability and availability.

A review of the testing and commissioning phase, as well as the experiences in the first months of operation, indicate that these goals have been met. The upgraded BCM, equipped with the MIBAD system, has safeguarded the LHCb detector since June 2023.

### Zusammenfassung

Experimente an Teilchenbeschleunigern, wie dem Large Hadron Collider (LHC), sind Beschädigungsrisiken durch die hochenergetischen Strahlen ausgesetzt. Daher wird das LHCb-Experiment am LHC durch den Beam Conditions Monitor (BCM) geschützt. Mithilfe von Diamantsensoren misst dieses Sicherheitssystem den Teilchenfluss an zwei Orten in der Nähe des Interaktionspunkts. Überschreiten die Messwerte ein sicheres Niveau, löst der BCM automatisch eine Extraktion der LHC-Strahlen aus.

In den Jahren 2018 bis 2022 hat der LHCb-Detektor ein Upgrade erhalten. Infolgedessen musste der BCM an die verfünffachte instantane Luminosität und die veränderte Detektorgeometrie angepasst werden. Außerdem wird die bestehende Ausleseelektronik des BCM wegen eines experimentweiten Austauschs der Datennahmehardware nicht mehr unterstützt.

In dieser Arbeit wird das Machine Interface Beam Abort (MIBAD) System für den Betrieb des BCMs nach dem Upgrade vorgestellt. Alle Aspekte der Entwicklung, also Hardware, Firmware und Software werden behandelt. Den Schwerpunkt der Arbeit bildet die Implementierung der Routine für die Bewertung der Stahlqualität mit programmierbaren Logikbausteinen. Für diese Kernkomponente des Strahlüberwachungssystems werden strenge Anforderungen bezüglich Verlässlichkeit und Verfügbarkeit gestellt.

In Hinblick auf die Testphase und die ersten Monate im Produktivbetrieb wurden diese Ziele erreicht. Seit Juni 2023 schützt der BCM mit der MIBAD Ausleseelektronik den LHCb Detektor.

## **Contents**

| 1. | Introduction |                                                |          |  |  |  |  |  |

|----|--------------|------------------------------------------------|----------|--|--|--|--|--|

| 2. | 2.1.         | LHCb experminent at the LHC Physics motivation | <b>3</b> |  |  |  |  |  |

|    | 2.2.         | The LHCb experiment at the LHC                 | 5        |  |  |  |  |  |

|    |              | Risk to the experiment due to LHC beams        | 13       |  |  |  |  |  |

|    | 2.4.         | LHC Beam Dumping system                        | 16       |  |  |  |  |  |

| 3. |              | ector physics                                  | 18       |  |  |  |  |  |

|    | 3.1.         | Interaction of particles and matter            | 18       |  |  |  |  |  |

|    | 3.2.         | Diamond as detector material                   | 21       |  |  |  |  |  |

| 4. | Bea          | Beam Conditions Monitor 27                     |          |  |  |  |  |  |

|    | 4.1.         | Sensor characterization                        | 29       |  |  |  |  |  |

|    | 4.2.         | Stations                                       | 29       |  |  |  |  |  |

|    | 4.3.         | Front-end electronics                          | 33       |  |  |  |  |  |

|    | 4.4.         | Simulation studies                             | 36       |  |  |  |  |  |

| 5. | Rea          | Readout system 38                              |          |  |  |  |  |  |

|    |              | Requirements                                   | 38       |  |  |  |  |  |

|    | 5.2.         | •                                              | 39       |  |  |  |  |  |

|    | 5.3.         | Architecture                                   | 42       |  |  |  |  |  |

| 6. | Rea          | dout hardware                                  | 44       |  |  |  |  |  |

| -  |              | Field Programmable Gate Arrays                 | 45       |  |  |  |  |  |

|    | 6.2.         |                                                | 46       |  |  |  |  |  |

|    | 6.3.         | MIBAD FPGA board                               | 48       |  |  |  |  |  |

|    | 6.4.         | Interface card                                 | 48       |  |  |  |  |  |

|    | 6.5.         | Power supply                                   | 50       |  |  |  |  |  |

|    | 6.6.         | Optical mezzanine cards                        | 51       |  |  |  |  |  |

| 7. | Rea          | dout firmware                                  | 53       |  |  |  |  |  |

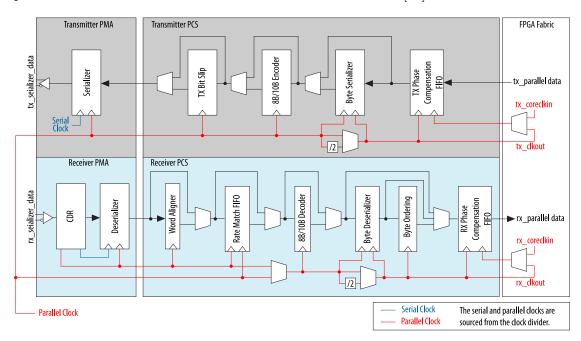

|    | 7.1.         | High Speed Serial Transceivers                 | 55       |  |  |  |  |  |

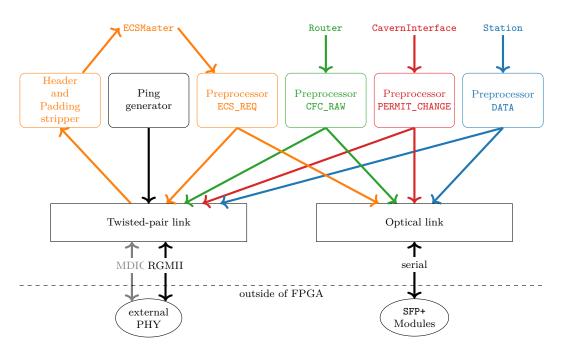

|    | 7.2.         | Frame router                                   | 59       |  |  |  |  |  |

|    | 7.3.         | Front end emulator                             | 61       |  |  |  |  |  |

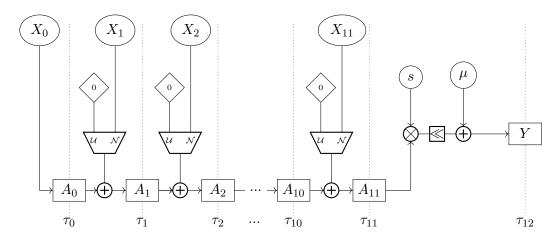

|    | 7.4.         | Data processing                                | 68       |  |  |  |  |  |

|    | 7.5.         |                                                | 76       |  |  |  |  |  |

|    | 7.6          | Back-end interface                             | 79       |  |  |  |  |  |

## Contents

|     | 7.7.   | ECS bus on the FPGA                          |

|-----|--------|----------------------------------------------|

|     | 7.8.   | Clock distribution and reset control         |

| 8.  |        | dout software 91                             |

|     | 8.1.   | Monitoring and control                       |

|     | 8.2.   | Post-mortem readout                          |

| 9.  | Com    | sissioning for Run 3                         |

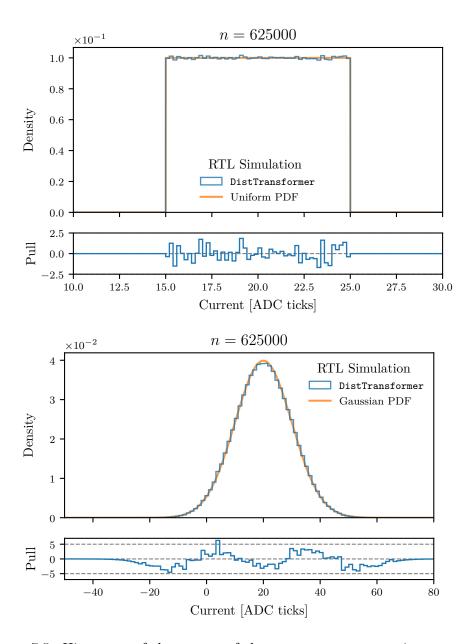

|     | 9.1.   | Simulation studies                           |

|     |        | Verification in hardware                     |

|     |        | Tandem operation and luminosity measurements |

|     |        | First beam dump                              |

| 10  | . Con  | clusion and outlook 109                      |

| Bil | oliogr | raphy 11                                     |

| Gle | ossar  | 120                                          |

| Α.  | Арр    | endix 12                                     |

|     | A.1.   | Front-end card                               |

|     |        | BCM threshold table                          |

|     |        | PermitChange packet                          |

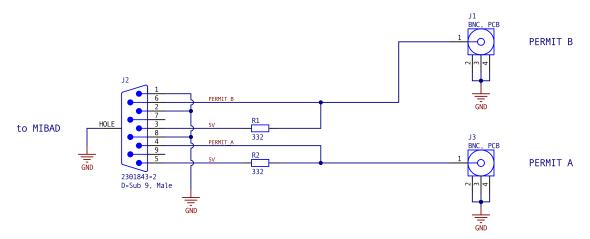

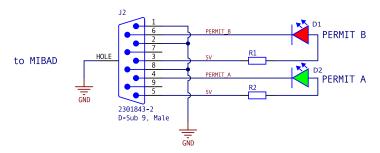

|     |        | Circuit diagrams                             |

|     |        | Mapping of MPO trunk fibers                  |

## 1. Introduction

The current understanding in the field of particle physics is formulated in the so-called Standard Model (SM)[37, 91, 110]. It describes all known elementary particles and three of the four fundamental interactions. Even though empirical observations confirm the predictions of the SM with high precision, the model is known to be incomplete. For example, it does not describe gravitational interactions or explain the origin of neutrino masses[6, 32]. Further, the SM does not describe dark matter or dark energy, which together account for 95 % of the energy density of the universe[5, 85, 108]. Additionally, the CP violation predicted by the SM is insufficient to explain the matter–antimatter imbalance observed in the universe[90].

Experiments at particle accelerators, such as the LHC[30] at the European Organization for Nuclear Research (CERN), are a possible avenue to probe the SM and search for New Physics. Such experiments usually involve placing a sensitive particle detector close to the crossing point of two high-energy particle beams and studying the results of the particle collisions. One of the four large LHC experiments, the Large Hadron Collider beauty (LHCb) experiment[71], is specialized in the study of particles containing b and c quarks. Instruments such as the LHCb detector are an invaluable asset to the scientific community, both in monetary terms and in countless person-hours spent on research and development.

A unique feature of the LHCb detector is the VErtex LOcator (VELO), a tracking system that features active silicon sensors as close as 8 mm to the LHC beam[71]. Due to their exposed position, components such as the VELO are susceptible to damage by the high-energy LHC beams. The BCM is a subsystem of the LHCb experiment dedicated to mitigating these risks. It features two stations with eight diamond sensors each that continuously monitor the particle flux near the LHCb interaction point (IP). When the conditions for a safe operation of the LHCb detector are no longer given, the BCM automatically requests a dump of the LHC beams to protect the detector. Since its initial commissioning in 2008, the BCM has successfully protected the LHCb detector.

From 2018 to 2022, the detector received a major upgrade to increase the rate of data taking, thereby reducing the statistical uncertainties of its measurements. Aspects of the upgrade include a fivefold increase in instantaneous luminosity and a new configuration of the VELO which brings sensitive material even closer to the beams[4]. In the light of these changes, the need for reliable protection of the detector becomes even more important.

#### 1. Introduction

The BCM system was overhauled alongside the rest of the experiment. One aspect of this upgrade is the construction of two stations with new diamond sensors. This is done to mitigate the effects of radiation damage and to adapt the station geometry to changed spatial constraints in the cavern. Furthermore, the BCM needs a new data acquisition (DAQ) system as the original hardware is reaching its end of life.

The goal of this thesis is to provide a comprehensive overview of activities relating to the upgrade of the BCM. Special emphasis is placed on the data acquisition system. The core component of this system is the MIBAD unit. Based on low-cost, off-the-shelf components, it receives and analyzes the data from the BCM front-end electronics. If necessary, the MIBAD also initiates the beam abort via the LHC interlock.

Beginning with a brief introduction to the SM, chapter 2 explores how the properties of B mesons influence the design of the LHCb detector and, therefore, its peculiar susceptibility to the LHC beams. At the end of the chapter, possible modes of beaminduced damage are investigated. Chapter 3 introduces the physical foundations for diamond sensors of the BCM.

Considering the abovementioned hazards, chapter 4 provides a bird's-eye view of the BCM system as a whole. On one hand, this includes parts of the original system that are kept in place, e.g., the front-end electronics. On the other hand, it highlights activities such as testing of new diamond sensors, mechanical engineering of stations, and simulation studies, that occurred in the scope of the BCM upgrade.

The remainder of this work is dedicated to the development of the readout system. At first, the requirements that informed the design of the DAQ system are laid out in chapter 5. This includes a discussion of interfaces to external systems, such as the LHC and the VELO interlocks. Based on these constraints, a readout architecture for the upgraded BCM is presented.

Subsequently, the implementation of this architecture is discussed in three aspects. At the heart of the MIBAD system lies a so-called field programmable gate array (FPGA). Chapter 6 explains how this card is embedded in a DAQ platform that provides necessary auxiliary components, external interfaces, and is suitable for safety-critical environments. Programmable logic devices, such as FPGAs, need their function to be specified through a hardware description language (HDL). Therefore, chapter 7 details the development of a firmware design which allows the real-time processing of the BCM data on the FPGA. The development of the software stack that is requirements controlling and monitoring BCM operations is presented in chapter 8.

The upgraded BCM with the new readout system is in operation since mid-2023. Details of the commissioning, such as system testing, first operational data, and the "trial by fire" of the upgrade BCM can be found in chapter 9.

## 2. The LHCb experminent at the LHC

## 2.1. Physics motivation

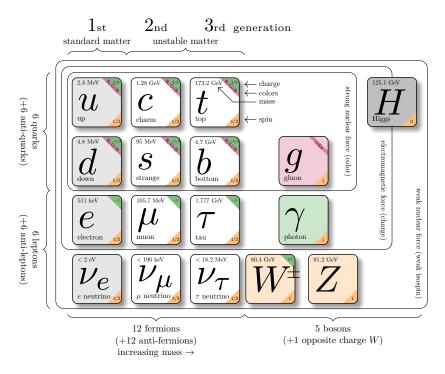

The Standard Model (SM) of particle physics is a relativistic quantum field theory that describes all known particles and three fundamental forces. A schematic overview of the SM particles is provided in Fig. 2.1. These particles can be classified according to their spin: *Bosons* have integer and *fermions* half-odd-integer spin values.

Four bosons mediate the interactions between the SM particles. The photon,  $\gamma$ , carries the electromagnetic interaction. Due to its long-range and relative strength, effects of the electromagnetic force can be directly observed in the macroscopic world. Gluons, g, couple to quarks, other gluons, and themselves. They are responsible for the strong interaction. The  $W^{\pm}$  and Z bosons mediate the weak interaction.

Discovered in 2012 by the ATLAS and CMS experiments at the LHC, the Higgs particle,  $H^0$ , is the last-discovered particle of the SM. It is a scalar, i.e., spin-0, boson which is responsible for giving the other SM particles their mass via spontaneous symmetry breaking according to the Higgs mechanism[29, 40].

The 12 fermions can be subdivided into six leptons and six quarks. Leptons do not couple to the gluon and therefore do not interact via the strong force. There are three lepton generations,  $(e, \mu, \tau)$ , each consisting of a charged lepton and its associated neutrino. The quark sector can also be divided into three generations. In each generation, there is an up-type quark with an electrical charge +2/3e and a down-type quark with a charge of -1/3e. Besides electrical charge, quarks also carry color charge. Hence, they couple to gluons and interact strongly with other quarks.

Compared to the other SM forces, the coupling constant of the strong force increases with distance. Therefore, single quarks cannot exist in free states, a phenomenon known as confinement. Instead, they form bound states called hadrons. Hadrons typically consist of a quark-antiquark pair or three (anti-)quarks. The latter is called a baryon, and the former a meson. However, exotic quark states, such as tetraquarks and pentaquarks, have been observed [1, 2]

As mentioned in the introduction, one of the open questions of the SM is the origin of the matter-antimatter imbalance which is observed in the universe. In 1967, Sakharov postulated three necessary preconditions for the emergence of baryon asymmetry[90]: Besides the non-conservation of the baryon number and thermodynamic non-equilibrium in the early universe, a violation of the *CP* symmetry is required. The *CP* transformation, a combination of charge conjugation and parity inversion, transforms matter into antimatter states and vice versa.

The SM allows for *CP* violation in the weak interaction via mixing matrices. These are the Cabibbo–Kobayashi–Maskawa (CKM)[21, 62] and Pontecorvo–Maki–Nakagawa–Sakat

#### 2. The LHCb experiment at the LHC

Figure 2.1.: Schematic overview of the SM particles. Figure adapted from Ref. [20].

(PMNS)[77, 83] matrices for the quark and lepton sector, respectively. However, the degree of CP violation predicted by the SM is not sufficient to explain the baryon asymmetry observed in the universe.

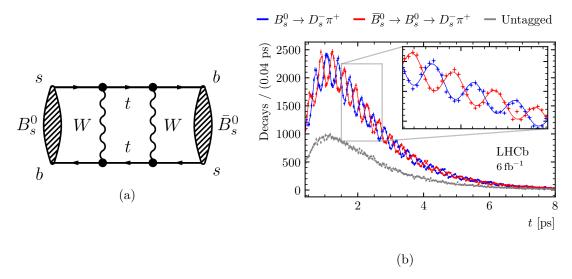

In the quark sector, the CKM matrix quantifies the mixing of flavor and mass eigenstates. A consequence of this mixing is so-called particle-antiparticle oscillation. One instance of this are oscillations in the  $B_s^0 \overline{B}_s^0$  system. The Feynman graph in Fig. 2.2a shows the leading-order contribution to this process. A measurement of this oscillation has recently been published by the LHCb collaboration[3]. Fig. 2.2b depicts the decaytime distributions. The frequency of this oscillation,  $\Delta m_s$ , relates to the elements of the CKM matrix. A precise measurement of  $\Delta m_s$  can be used to probe CP violation in the SM.

Precision measurements, such as the one above, pose certain experimental challenges: A source capable of delivering many  $B_s^0$  mesons is needed to perform an analysis with the required statistical precision. Also, the decay products need to be detected and reconstructed with a high efficiency. Experimentally, the decay time is derived from the difference of the production and decay vertex. Given the range of decay times in Fig. 2.2b, the corresponding flight distances are in the order of millimeters. Therefore, a tracking system with a sufficiently high spatial resolution is required to observe these oscillations. An experiment that fulfills these requirements is the LHCb detector at the LHC.

Figure 2.2.: Left: Feynman diagram of one of the leading order contributions  $B_s^0$  mixing. Right: Decay time distributions of  $B_s^0 \to D_s^- \pi^+$ . Figure taken from Ref. [3].

## 2.2. The LHCb experiment at the LHC

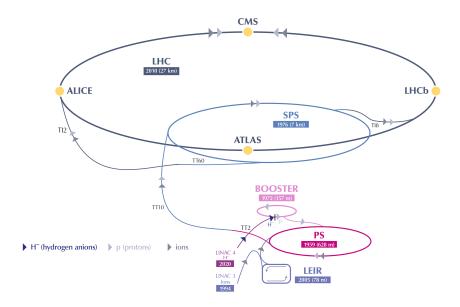

Located at the European Organization for Nuclear Research (CERN) near Geneva, Switzerland, the LHC is the largest, most powerful particle accelerator currently in operation. Protons and heavy nuclei are accelerated to an energy of up to 7 TeV in two underground storage rings with a circumference of 26.7 km. At four points around the ring, the counter-roating beams collide. In each beam, the LHC can accelerate of up to 2808 bunches, each containing a maximum of  $1.15 \times 10^{11}$  protons. The subsequent description of the LHC, as seen in Fig. 2.3, is based on Ref. [30].

The LHC tunnel, which was repurposed from the former Large Electron Positron Collider (LEP), is made up of eight straight sections connected by arcs. Superconducting dipole magnets are used to bend the beams in the arc sections. Using liquid helium, these magnets are cooled to temperatures of 2 K and reach field strengths of up to 8 T.

In the center of each straight section lies a so-called insertion region (IR). In four of these regions, the beams are collided, and the surroundings are instrumented to study these collisions. The general-purpose detectors ATLAS and CMS are located at IR 1 and IR 5, respectively. These experiments are designed for data taking at high luminosities. The medium-luminosity insertions, IR 2 and IR 8, host the ALICE and LHCb experiments.

In addition to the experiments located at the collision points, the other IRs host other facilities required for operation of the LHC. Particles that deviate from the nominal orbit either in momentum or transverse offset are removed by collimator systems located at IR 3 and IR 7. IR 4 houses the radio frequency (RF) cavities required for the acceleration of the protons. The safe disposal of the high-energy LHC beams, is critical for the operation of the accelerator. For this reason, a dedicated beam abort facility is located

Figure 2.3.: Overview of the Large Hadron Collider (LHC) and its pre-accelerators. The proton beam is created by stripping electrons off hydrogen anions accelerated by LINAC 4. Subsequently, the beam energy is stepped up by the Proton Synchrotron Booster (PSB), Proton Synchrotron (PS), and Super Proton Synchrotron (SPS). Figure modified from Ref. [74].

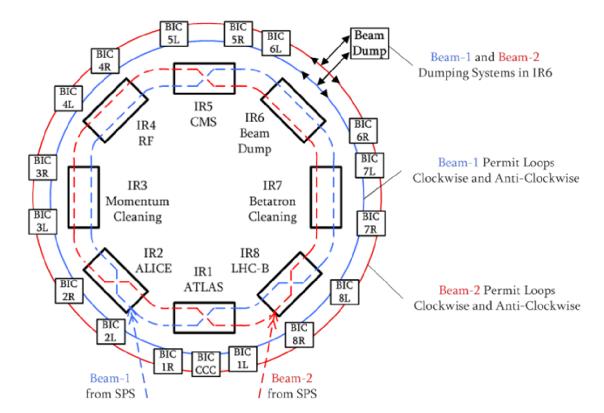

at IR 6. Due to its relevance for the BCM, the LHC Beam Dumping System (LBDS) is described in greater detail in section 2.4.

Before injection into the LHC ring, the particles pass through a chain of pre-accelerators, shown in Fig. 2.3. Since 2020, the newly commissioned LINAC4 is the first step in the chain[97]. This linear accelerator produces a beam of hydrogen anions, H<sup>-</sup>, with a kinetic energy of 160 MeV. The hydrogen ions are stripped of their electrons, leaving protons that are injected into a chain of three circular pre-accelerators. Subsequently, the protons are accelerated by the Proton Synchrotron Booster (PSB), Proton Synchrotron (PS), and Super Proton Synchrotron (SPS) to energies of 1.4 GeV, 25 GeV, and 450 GeV, respectively. From SPS, the beam is injected into the LHC via two transfer lines, which are referred to as TI2 and TI8. Beam 1, which circulates clockwise in the LHC ring, is injected near IR 2 upstream of the ALICE experiment. Circulating in the opposite direction, beam 2 is injected near IR 8 upstream of the LHCb experiment.

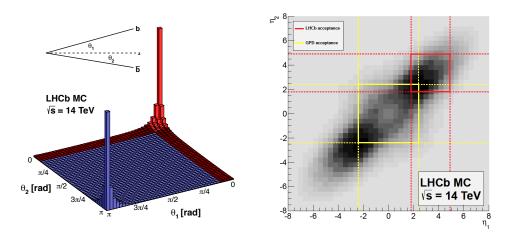

In the high-energy proton-proton collisions at the LHC, bb pairs are predominantly produced by gluon-gluon fusion. As it is likely that the gluons involved have different momenta, the produced particles receive a significant boost in the direction of the beams. Fig. 2.4 shows the resulting angular distribution for the production of  $b\bar{b}$  pairs from pp collisions at a center of mass energy of 14 TeV.

Therefore, the LHCb detector is implemented as a single-arm forward spectrometer. In contrast to general purpose detectors such as ATLAS or CMS, the LHCb detector

Figure 2.4.: Distribution of  $b\bar{b}$  pairs produced by pp collisions at a center of mass energy of 14 TeV as a function of polar angle,  $\theta$ , (left) and pseudorapidity,  $\eta$  (right). The acceptance of the LHCb detector is indicated in red, whereas the yellow lines show the acceptance of a typical general-purpose detector(GPD). Figures taken from Ref. [28].

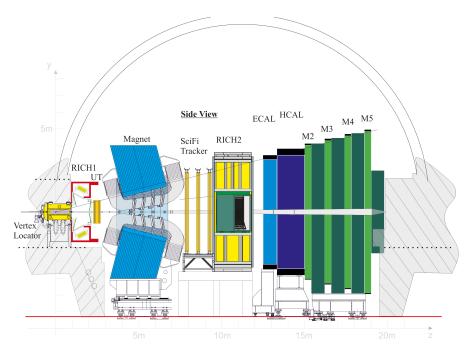

does not surround the IP of the LHC beams symmetrically. Instead, only a relatively small angular region in the forward direction is instrumented so that the detector covers a pseudo rapidity range of  $2 < \eta < 5$  [71]. An overview of the LHCb detector is given in Fig. 2.5. It consists of several subdetectors, which can broadly be categorized by their function into two groups, the tracking system and the particle ID (PID) system.

#### 2.2.1. Tracking system

The VELO is a precise silicon pixel tracking system which surrounds the IP of the LHC beams. Its main purpose is the determination of the primary and secondary vertices, i.e. the location of the original pp collision and the subsequent decays of short-lived particles such as B mesons.

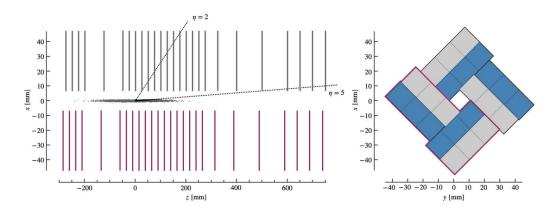

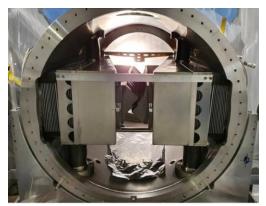

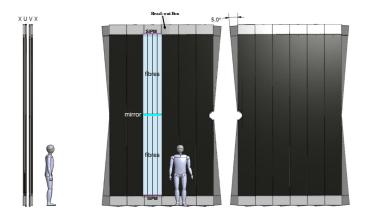

The VELO is made up of two stations which can be moved away from the beams during injection to protect the sensors from damage by the LHC beams. As seen in Fig. 2.6, each station consists of 26 L-shaped silicon pixel detector modules. The modules are placed inside the LHC vacuum chamber to reduce the amount of material between the interaction region and the VELO sensor. To suppress interference from the VELO structures on the LHCs operation (such as changes to the machine impedance), the sub detector is separated from the beam line by a thin aluminum foil. This so called RF-Foil (see Fig. 2.7) has a thickness of around 250 µm and is machined from a solid piece of aluminum.

Because the RF-Foil is the part of the VELO that is closest to the LHC beam line, it is very susceptible to damage by adverse beam conditions (see section 2.3). During

#### 2. The LHCb experiment at the LHC

Figure 2.5.: Schematic of the LHCb detector after the completion of Phase I upgrade at the beginning of Run 3. Figure taken from Ref. [70].

data taking, the VELO stations are in the position closest to the beam axis. Then, the minimum clearance of the beam axis to the RF-Foil is 3.5 mm.

Due to their short lifetimes, particles such as B and  $B_s^0$  mesons cannot leave the VELO before they decay. However, the lifetimes of  $K_s^0$  mesons and  $\Lambda$  are two orders of magnitude larger. Hence, a majority of these decays occur between the VELO and the Scintillating Fibre (SciFi) tracker. The Upstream Tracker, placed between the Ring Imaging Cherenkov (RICH) 1 and the dipole magnet, significantly improves the reconstruction of these decays [70].

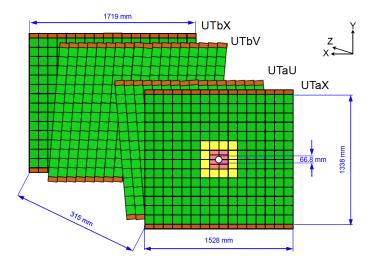

It consists of four planes of silicon strip sensors, as shown in Fig. 2.8. The strips are arranged to provide the maximum spatial resolution in the bending (horizontal) plane. However, central layers, UTaU and UTbV, are tilted by  $\pm 5^{\circ}$  to allow for 3D track reconstruction by combining hits from multiple layers.

The track density is not uniform over the  $1.5\,\mathrm{m}\times1.3\,\mathrm{m}$  acceptance of the detector. It is highest near the beam pipe and sharply falls off towards the outer regions. Depending on the area, silicon strips with varying lengths and widths are used with the goal of keeping the maximum occupancy below a few percent. The single hit efficiency of the sensors exceeds  $99\,\%[4]$ .

Particle momenta are determined by observing the bending of the particle tracks in a magnetic field. This field is produced by a normal-conducting dipole magnet located between the UT and the SciFi tracker. The LHCb dipole consists of two aluminum coils integrated into an iron yoke. With a nominal current of  $5.85\,\mathrm{kA}$ , these water-cooled coils produce a magnetic field with a bending power of  $4\,\mathrm{T}\,\mathrm{m}$ . Tracks of charged particles are

Figure 2.6.: Left: Placement of the VELO sensors in the x-z plane around the luminous region at the IP. Right: Layout of the VELO modules in the closed position in the x-y plane. Figures taken from Ref. [4].

Figure 2.7.: Prototype of the VELO RF-Foil, which has a thickness of 250 µm and is milled from a single block of aluminum. Figures taken from Ref. [65].

Figure 2.8.: Schematic overview of the geometry of the Upstream Tracker (UT): The layout consists of four layers along the z axis. The strip sensors in the outer stations are parallel to the y axis. The inner stations are angled  $\pm 5^{\circ}$  to enable 3-dimensional localization of the particle hits. Figure taken from Ref. [70].

bent in the horizontal plane. During data taking, the polarity of the magnet is periodically reversed to investigate the impact of detector asymmetries. The magnet covers the full detector acceptance, i.e.,  $\pm 250 \,\mathrm{mrad}$  vertically and  $\pm 300 \,\mathrm{mrad}$  horizontally.

The Scintillating Fibre (SciFi) tracker is located downstream of the dipole magnet. It measures the curvature of particle tracks due to the magnetic field, thereby providing an estimate for the momentum of the particles.

The tracker utilizes scintillating fibers, which are read out by silicon photomultipliers, to localize the hits of charged particles. Photons created by the scintillation process are guided by the fibers via total internal reflection. This allows the readout electronics to be placed outside the acceptance of the tracker.

Fig. 2.9 shows the general layout of the SciFi tracker. It has three tracking stations with four layers of sensitive material at each station. In analogy to the UT design, the inner layers in each station are rotated by  $\pm 5^{\circ}$  to provide 3D hit information. The layers are built of modules with a length of 4850 mm and a width of 523 mm[4].

In the first two tracking stations, ten modules per layer are required to cover the nominal LHCb acceptance, whereas the third station has twelve modules. The SciFi tracker is designed for a target single-hit efficiency over 99 % and a resolution of less than 100 µm in the bending plane [4].

#### 2.2.2. Particle Identification

Hadron identification, in particular the separation of pions and kaons, is an essential requirement of the LHCb experiment. The particle identification subsystem of the LHCb

#### 2. The LHCb experiment at the LHC

Figure 2.9.: Each station of the SciFi-Tracker is made from modules made of fiber mats placed vertically along the width of the station. The mats are read out on the top and the bottom by silicon photo multipliers (SiPMs). A mirror is added to the other side of the mats to increase the light yield. Figure taken from Ref. [70].

detector consists of the two RICH detectors, an electromagnetic and hadron calorimeter, and the muon chambers.

For the LHCb experiment, this task is handled by the PID subsystem. Here the RICH detectors play an important role. These subdetectors are located at two points in front of and behind the magnet. Between the VELO and the UT and between the SciFi tracker and the calorimeters. Charged particles traveling faster than the speed of light in a given medium emit so-called Cherenkov radiation. The light is emitted in a cone-shaped angular distribution along the path of the particle, where the opening angle of the Cherenkov is given by

$$\cos \theta = \frac{m}{n \cdot \beta}.\tag{2.1}$$

This dependence on the velocity  $\beta$  is exploited by the RICH subdetectors. Together with momentum information from the tracking system (see section 2.2.1) a mass hypothesis for each particle can be formed.

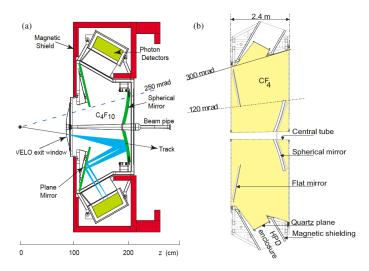

A schematic overview of the RICH stations structure is given in Fig. 2.10: RICH 1 which has an angular acceptance of  $300\,\mathrm{mrad}$  (horizontal) and  $250\,\mathrm{mrad}$  vertical uses Perfluorobutane ( $\mathrm{C_4F_{10}}$ ) as the active radiator medium. Optimized for higher momentum tracks and with a smaller acceptance –  $120\,\mathrm{mrad}$  (horizontal) and  $100\,\mathrm{mrad}$  (vertical) – RICH II uses carbon tetrafluoride  $\mathrm{CF_4}$  as radiator medium[67]. Both stations use a series of spherical and flat mirrors to guide the Cherenkov light into multianode photo multipliers for read-out.

To measure the energy of particles, LHCb features a calorimeter system consisting of an electromagnetic calorimeter (ECAL) and hadronic calorimeter (HCAL). The operational principle of a calorimeter is to stop incoming primary particles by inducing particle showers inside an absorber material. In the ECAL, charged particles and pho-

#### 2. The LHCb experiment at the LHC

Figure 2.10.: Optical system of the RICH subdetectors. Light produced by the radiators, namely  $C_4F_{10}$  for RICH 1 and  $CF_4$  for RICH 2, is guided by spherical and planar mirrors to multi-anode photo multipliers. Figure taken from Ref. [69].

tons are stopped with a lead absorber. Iron is used for strongly interacting particles in the HCAL.

The secondary particles created by the showers are then detected in scintillator layers interspersed with the absorber material, where optical photons are created depending on the amount of energy deposited. These photons are then guided by wavelength shifting optical fibers to photo multiplier tubes for readout.

Of all particle species that travel through the LHCb detector, muons are the ones that travel the farthest. Due to their lack of hadronic interaction and their relatively high mass compared to electrons, they largely pass through all detector layers discussed so far. Therefore, the muon chambers are placed behind the HCAL, furthest from the IP.

The muon system consists of four stations, M 2-M 5. These stations consist of multiwire proportional chambers, interleaved with iron filters. The 80 cm thick absorbers are used to differentiate between increasingly energetic muons. Muons with a momentum of more than  $6 \, \text{GeV/c}$  pass the last station. Multi-wire proportional chambers are gas detectors, consisting of high voltage electrodes in a gas volume. Based on these measurements, the muon system can determine the transverse momentum,  $p_{\text{T}}$ , of a muon candidate with a resolution of 20 %. This information is important for trigger decisions and event reconstruction, as muons are present in the final state of many relevant decay channels.

Table 2.1.: Evolution of the nominal beam parameters over the three runs of the LHC. Values are given for the proton energy,  $E_{\rm p}$ , the number of protons per bunch,  $N_{\rm b}$ , the number of bunches stored per beam,  $n_{\rm b}$ , and the resulting total energy per beam,  $E_{\rm beam}$ . Data taken from Ref. [76].

|                     |       | Run 1<br>(2009–2013) | Run 2<br>(2015–2018) | Run 3<br>(2022–2024) |

|---------------------|-------|----------------------|----------------------|----------------------|

| $E_{\rm p}$         | (TeV) | 4                    | 6.5                  | 6.8                  |

| $N_{ m b}$          |       | $1.7 \times 10^{11}$ | $1.2\times10^{11}$   | $1.8 \times 10^{11}$ |

| $n_{ m b}$          |       | 1380                 | 2556                 | 2748                 |

| $E_{\mathrm{beam}}$ | (MJ)  | 150                  | 320                  | 539                  |

### 2.3. Risk to the experiment due to LHC beams

Over the years of its operation, the LHC is continuously pushing both the energy and luminosity frontier. As indicated in table 2.1, the increase of proton energy and beam intensity, as given by the total number of protons in the machine, leads to ever-increasing beam energies. In Run 3, the energy is expected to reach 539 MJ[76] per beam. This level of stored energy represents a major challenge for the machine protection system[111].

Even losses of a fraction of the total beam particles can damage susceptible equipment. Energy depositions of as little as  $38\,\mathrm{mJ/cm^2}$  can lead to a local loss of superconductivity in some LHC magnets[11]. This triggers a so-called *quench* with the ohmic heating caused by the now normal conducting region leads to further warming and further loss of superconductivity. If not controlled, a magnet quench has the potential to severely damage surrounding equipment.

For this reason, an effective machine protection system is an imperative for operating a machine such as the LHC. The Beam Loss Monitor (BLM) is the primary machine protection system of the accelerator. It consists of circa 4000 detectors, mostly ionization chambers, placed around the LHC ring[89]. Due to the small aperture of the VELO, the LHCb experiment operates its own dedicated beam monitoring system. The Beam Conditions Monitor (BCM), which is introduced in detail in chapter 4, measures the particle flux around IP 8.

Various processes contribute to this particle flux. Under normal conditions, the particle collisions at the interaction point are the major source of flux[72]. As part of the BCM upgrade, Monte-Carlo simulations were conducted to estimate the resulting BCM signals from this background, cf. section 4.4.

Due to various processes, protons can attain a deviation in terms of momentum or transverse offset with respect to the nominal bunch position. As these particles are still guided by the beam optics, they travel with the nominal bunches, forming the so-called beam halo. Collimators exist at various places around the ring to intercept the halo particles. However, not all protons interact with the collimator, or they are elastically scattered, leaving a secondary halo. Therefore, a multi-stage collimation process is

utilized at the LHC with secondary and tertiary collimators to intercept the remaining halo

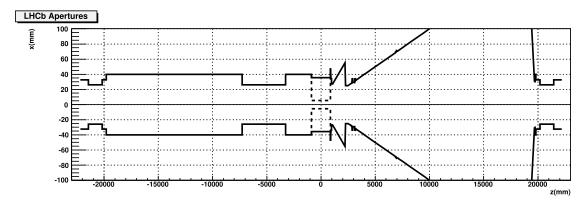

The aperture around the LHCb experiment determines the level of machine induced background in the experimental cavern. Figure Fig. 2.11 shows the horizontal aperture 22m in either direction from IP 8. In this area, the aperture is fixed, except for the VELO. During injection and until stable beams have been established, the VELO remains in the retracted position. At this point in time, the narrowest locations are the within the compensator magnets at  $\pm 22\,\mathrm{m}$  from the IP and at the UT with an aperture of 26 mm and 25 mm, respectively[72]. Once data taking commences, the VELO is moved towards the beam and it becomes the area of minimal aperture.

Beyond the nominal backgrounds, an understanding of the particle flux during adverse beam conditions is important for the design of the BCM. In the remainder of the section, three beam loss scenarios are examined. The most basic adverse condition is beam scraping. Due to misconfigured or malfunctioning beam optics, the beam could significantly deviate from its nominal trajectory, moving closer to the boundary of the aperture. A substantial growth of transverse emittance, which corresponds to an increase in beam width, would have the same effect.

Ultimately, portions of the beam will scrape on narrow parts of the aperture, leading to large beam losses at these structures. The resulting energy deposition has the potential to damage adjacent structures, which for the LHCb detector is the VELO. As part of the BCM Monte Carlo studies, simulations were conducted to quantify the response of BCM in beam scraping scenarios and relate it to the energy deposition in the VELO.

First observed in June 2010, so-called unidentified falling objects (UFO) have caused beam losses that are localized and occur on a timescale of a few LHC turns[13]. It is hypothesized that these losses are caused by micro-meter sized dust attached to the ceiling of the beam pipe[73]. Once they become dislodged, they fall and cross the high-energy proton beam. The resulting beam losses can cause both quenches of superconducting magnets and protective beam dumps by the BLM and the BCMs of the experiments. In Run 2, UFO incidents lead to 62 beam dumps. Of these, 9 were initiated by the experiment BCMs[81].

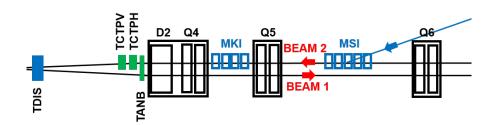

The loss mechanisms discussed so far occur when the beams are already circulating in the LHC ring. However, in addition to this, losses during the injection process need to be considered. Concerning the safety of the LHCb detector, the injection of beam 2 has the greatest impact due to the proximity of the injection point to the LHCb experimental cavern

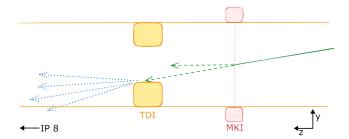

The injection area is located approximately 190 m downstream of IP 8. At this point, two magnets shown in Fig. 2.12 direct the proton bunches supplied by the transfer line TI 8 into the LHC orbit. A series of septum magnets bend the protons in the horizontal plane. From this point on, the incoming and already circulating bunches travel, vertically separated, in the same vacuum chamber. The injection kicker magnet (MKI), produces a pulsed magnetic field that deflects the incoming bunches into the LHC orbit while leaving the circulating bunches unaffected.

Failure of the kicker during injection, as illustrated in Fig. 2.13, leaves the injected bunch undeflected and on trajectory to leave the aperture. Similarly, a mistimed kicker

#### 2. The LHCb experiment at the LHC

pulse can bend circulating bunches out of orbit. Beam absorbers(TDI) are placed behind the kicker magnet to intercept any stray bunches. According to Ref. [93], the TDI has protected downstream equipment, such as superconducting magnets and the LHCb detector, during several kicker failures.

However, when the movable absorber jaws of the TDI are inappropriately positioned, scraping of the beam can lead to showers of secondary particles travelling in the direction of the LHCb cavern. In a reduced form, these so-called splashes are commonly observed by the BCM during injections. In the past, splashes from the TDI have caused quenches in nearby superconducting magnets[93]. These events also triggered interventions from the BCM due excessive particle fluxes. One such incident at the beginning of Run 3 is presented in section 9.4.

Figure 2.11.: Horizontal aperture in the area  $\pm 22 \,\mathrm{m}$  of IP 8. Figure taken from Ref. [72].

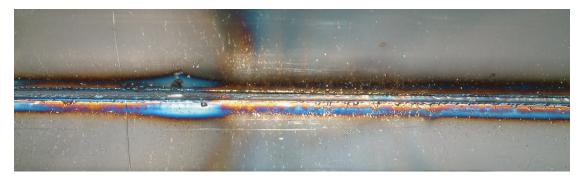

Even the 450 GeV injection beam from the SPS can cause significant damage when it comes in direct contact with the aperture of the accelerator, An incident during a high-intensity SPS extraction test in 2004 illustrates this fact. A full LHC injection batch containing  $3.4 \times 10^{13}$  protons was extracted on a significantly wrong trajectory and collided with the wall of the vacuum chamber. Fig. 2.14 shows the resulting damage, which included an approximately 25 cm long cut leading to a vacuum leak.

Figure 2.12.: Injection of beam 2 in the to the right of the LHCb experimental cavern. Figure modified from Ref. [23].

Figure 2.13.: Illustration of injection kicker failure. When the injection kicker, MKI, fails to fire, the incoming beam is not bent onto the LHC orbit. Instead, it is absorbed by the TDI collimator to prevent damage to the machine. However, interactions with the TDI material can produce secondary particles that can reach the LHCb cavern. Figure based on Ref. [93].

Figure 2.14.: Damage in the TT 40 SPS extraction line after impact with a 450 GeV proton beam. The length of the groove is approximately 110 cm. Figure taken from Ref. [38].

## 2.4. LHC Beam Dumping system

A significant amount of energy is stored in the circulating LHC beams. Therefore, both during normal operation and in case of emergencies, the safe disposal of the beams is very important for the safe operation of the accelerator. The LHC Beam Dumping System (LBDS) located at IR 6, which is shown in Fig. 2.15[30], achieves this task by extracting the beam the main beam line and guiding it to an absorber capable of thermally dissipating the energy of the beam. The LBDS consists of two symmetrical assemblies, one for each ring. A set of 15 extraction kicker magnets are used to horizontally deflect the beam from its nominal trajectory. These magnets' ramping time of 3 µs determines the length of the abort gap. If the kickers ramp outside this gap (unsynchronized beam dump), the beam is deflected into structural material in the vicinity of the extraction point, which may lead to damages.

The deflected bunches travel through the high-field gap of the 15 septum magnets while the nominal trajectory passes through the field-free region. The field of the septum magnets deflects the bunches vertically and away from the LHC cryostat. To decrease

#### 2. The LHCb experiment at the LHC

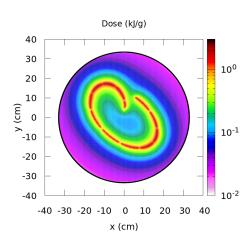

Figure 2.15.: Left: Simulated transverse energy deposition of a  $7\,\mathrm{TeV}$  beam with  $1.8\times10^{11}$  protons per bunch at a depth of about  $270\,\mathrm{cm}$ . Figure taken from Ref. [76]. The form of the distribution is the result of sweeping the beam across the dump block to reduce the maximum energy density. Right: Front-view on the cylindrical beam dump block surrounded by concrete shielding. Photo cropped from Ref. [79].

the energy density of the beam, a dilution kicker magnets sweep the beam across the absorber block, which located a drift length of  $\sim 750\,\mathrm{m}[30]$ . The absorber itself consists of a water-cooled graphite cylinder with a diameter of 722 mm and a length of 8520 mm. The graphite is encased in stainless steel and over pressurized with nitrogen to prevent oxidation of graphite. For radiation shielding the absorber assembly is surrounded by 900 t of steel and concrete blocks[76].

The BCM uses diamond sensors to measure the particle flux. Energy deposition mechanisms are important for understanding potential damage scenarios, which include the energy deposition in the VELO sensors. This chapter introduces the detector physics concepts relevant for the BCM. A thorough treatment of this subject is available in established literature, e.g. Ref. [63]. In the first section the interaction of particles and matter is discussed in general. Subsequently, the focus of the second part lies on chemical vapor deposition (CVD) diamond, which is used as the sensor material for the BCM.

## 3.1. Interaction of particles and matter

In general, particles are detected via their interactions with the surrounding matter. A particle travelling through a medium will interact with it and thereby deposit energy. The properties of both the target material and the incident particles determine the type and rate of interactions and the amount of energy transferred. The *stopping power*  $\langle - dE/dx \rangle$  quantifies the mean energy loss per distance travelled. For charged particles, the relevant processes are excitation and ionization at lower energies, and radiative losses due to Bremsstrahlung at higher energies.

Ionization losses occur due to Rutherford scattering of the incident particles on the electrons of the target medium. Depending on the amount of transferred energy, this leads to ionization or excitation of the target atom. For heavy particles, i.e.,  $m > m_e$ , the average stopping power due to ionization and excitation is given by the Bethe-Bloch formula [17]:

$$\left\langle -\frac{\mathrm{d}E}{\mathrm{d}x} \right\rangle = Kz^2 \frac{Z}{A} \frac{1}{\beta^2} \left[ \frac{1}{2} \ln \frac{2m_e c^2 \beta^2 \gamma^2 W_{\text{max}}}{I^2} - \beta^2 \right]. \tag{3.1}$$

The stopping power is a function of the particles relativistic kinematic parameters  $\beta$  and  $\gamma$ . The other quantities are

- a constant scaling factor  $K = 0.307 \,\mathrm{MeV cm^2/mol}$ ,

- the charge of the incident particle z,

- the atomic number A, molar mass Z, and mean excitation energy, I, of the target material,

- and the maximum energy transfer possible per interaction  $W_{\text{max}}[85]$ .

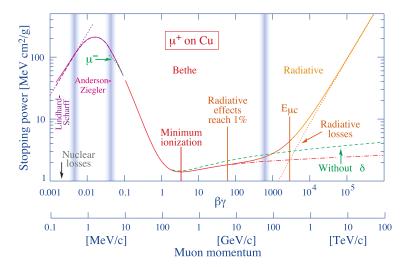

Fig. 3.1 exemplifies the stopping power for antimuons,  $\mu^+$ , on a copper target over a wide kinematic range. In the intermediate momentum range,  $0.1 < \beta \gamma < 1000$ , the stopping

power is described by the Bethe-Bloch equation. Here, the mean energy loss reaches a minimum. According to Ref. [85], this occurs at  $\beta\gamma \approx 3$  to 3.5 in most materials. Particles in this regime are referred to as minimum ionizing particles (MIPs). For the characterization of particle detectors MIPs serve as an important benchmark because they represent the worst case signal size due to the minimal energy deposition.

Figure 3.1.: Stopping power for an antimuon beam through copper in different energy regimes. Figure taken from Ref. [85].

The aforementioned calculations are valid for heavy particles. But during testing of detectors with  $\beta$  sources for example, the stopping power for electron beams is of special interest. Several modifications have to be made to eq. (3.1) to correctly describe the interaction of electrons: Firstly, because incident and target particle are of the same species, quantum mechanical indistinguishability reduces the maximum energy transfer  $W_{\text{max}}$  by a factor of two compared to the classical treatment. Secondly, in the case of large energy transfers, the interactions have to be treated as discrete processes, Møller scattering, i.e. See Refs. [85, 109] for a more thorough treatment including the computation of the applicable interaction cross-sections.

With higher momentum, the Bethe-Bloch theory, cf. eq. (3.1), predicts logarithmic increase in stopping power. Yet, a stronger rise is observed for higher values of  $\beta\gamma$ , because radiative effects become significant in this regime. Charges deflected in the electric field of the medium's nuclei radiate photons. The energy loss due to this Bremsstrahlung scales linear with the incident particle's energy and is inversely proportional to the square of its mass M:

$$\left(-\frac{\mathrm{d}E}{\mathrm{d}x}\right)_{\mathrm{rad}} = \frac{E}{X_0} \propto Z^2 \frac{E}{M^2}.$$

(3.2)

Hence, radiative losses become significant at lower energies for electrons compared to heavier particles.

The radiation length,  $X_0$ , represents the typical length scale for radiative losses in a given material. It is also useful to compare the influence of different materials on a

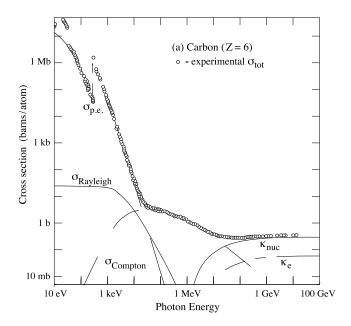

particle beam. The photons produced by Bremsstrahlung can also interact with the surrounding matter. Depending on the energy, there are three different processes that dominate the interaction of photons with matter, which are shown in Fig. 3.2 for a carbon target.

In the low-energy regime, i.e.,  $E_{\gamma} \lesssim 10\,\mathrm{keV}$ , the photo-electric effect dominates the total interaction cross-section. Here, an electron is removed from the atomic shell of the material after interacting with an incoming photon. The latter is absorbed in the process. The remaining energy of the photon is transferred to the electron as kinetic energy. For higher photon energies, which are comparable to the electron rest energy  $m_e c^2$ , Compton scattering becomes the dominant interaction. In this case, the photon is scattered inelastically on an electron. Some of the initial photon's energy is transferred to the electron during the interaction. As a result, the outgoing photon is emitted with a larger wavelength.

For even higher energies, pair production is the dominating process. The conversion of a photon to an electron positron pair is possible when the incident photon energy is at least  $2m_e$ . In isolation, this reaction is not possible as it violates the conservation of momentum. However, in the presence of a nuclear field, this limitation is lifted. Pair production is related to the emission of Bremsstrahlung. In fact, at high energies, products of either reaction can in turn undergo the other, leading to the formation of an electromangetic shower. In these cascades, a single incident photon or electron creates an exponentially growing number of daughter particles by repeated pair production and Bremsstrahlung emission. The reaction stops when the photon energy falls below the minimum energy for pair production mentioned above. In the context of the LHCb experiment, electromagnetic showers are relevant both for the energy measurement in the calorimeters and as a possible consequence of adverse beam conditions as discussed in section 2.3.

Figure 3.2.: Photon cross-section as a function of energy in a carbon target.  $\sigma_{\text{p.e.}}$  corresponds to the photo-electric effect,  $\sigma_{\text{Compton}}$  to the Compton effect, and  $\kappa_{\text{nuc}}$  to pair production in the nuclear field. Figure modified from Ref. [85].

#### 3.2. Diamond as detector material

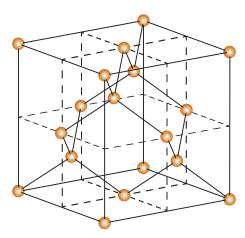

This section will give an introduction to the properties of chemical vapor deposition (CVD) diamond and its application in particle detection. In table 3.1, the material properties of diamond are summarized and compared to silicon, which is a common material in detector applications. Carbon can form different solid phases depending on the spacial configuration of the atoms: Graphite and diamond are two common allotropes of the element carbon. Diamond is made up of atoms arranged in the eponymous diamond lattice structure shown in Fig. 3.3. This structure consists of two interlaced fcc lattices shifted diagonally by a quarter of the lattice constant. Each atom forms  $sp^3$ -hybrid orbitals with its four closest neighbors. This results in a tetrahedral crystal structure with a lattice constant of 3.57 Å[88].

Diamond is meta-stable under standard temperature and pressure conditions, This means it does not convert to the thermodynamically preferable Graphite configuration due to the high activation energy of  $728\,\mathrm{kJ\,mol^{-1}}$  for this reaction[24]. In nature, diamond is formed at high temperatures and pressures in the earth's mantel and moved up into the crust by volcanic activity. As early as 1995, this process was replicated by the so called high-pressure high-temperature (HPHT) synthesis. In this process, carbon is converted into diamond at pressures 50 kbar to 100 kbar and temperatures of 1800 K to 2300 K [82]. Diamonds produced by the HPHT technique are almost exclusively utilized in industrial applications. They are unsuitable for detector use due to their small size – typically around 1 mm – and insufficient purity.

Figure 3.3.: The diamond crystal structure consists of two interlaced face-centered cubic (fcc) lattices shifted diagonally by a quarter of the lattice constant. Figure taken from Ref. [63].

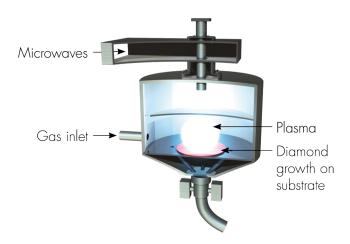

An alternative to HPHT synthesis is the chemical vapor deposition (CVD) process, in which diamond is grown on a substrate in a low pressure ( $< 100 \,\mathrm{kPa}$ ) environment. The underlying process is the decomposition of methane

$$CH_{4(g)} \longrightarrow 2H_{2(g)} + C_{diamond}$$

(3.3)

and the subsequent deposition of the carbon onto a substrate. For the reaction to proceed, activation energy must be provided to the gaseous phase. This can be done in several ways, such as via a hot filament or a microwave plasma. For detector-grade diamond, the latter is the preferred method as it introduces the fewest impurities into the finished product. A schematic reactor for the microwave CVD process is shown in Fig. 3.4.

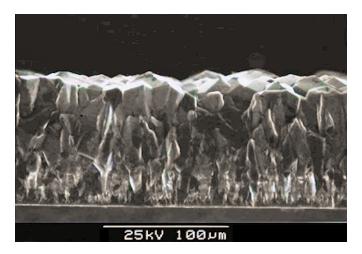

The large-scale structure of the resulting diamond depends on the choice of substrate: If a single crystal is used, it continues to grow due to the carbon deposition. The result is a so-called single-crystalline CVD (sCVD) diamond. Alternatively, powdered diamond can be used as growth medium. Each diamond grain serves as a nucleation site for vapor deposition, which causes columnar growth (see Fig. 3.5) of poly-crystalline CVD (pCVD) diamond, whereby the grain size increases in the growth direction. This polycrystaline structure impacts the electrical properties of the diamond in a potentially undesirable manner. However, pCVD diamond can be grown to larger sizes and produced at a lower cost. Therefore, they are often the preferred choice in detector applications such as the BCM.

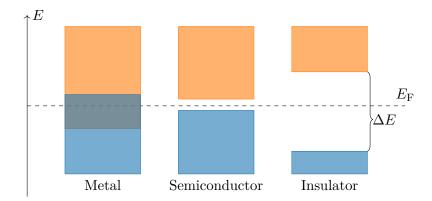

For the use of a material as a sensor medium its electrical properties are of importance. In solids, the energy levels of the electrons are influenced by the large number of atomic nuclei in the crystal lattice. This leads to the formation of so-called energy bands with groups of tightly spaced energy levels separated by a relatively large band gap ( $\sim$  eV). The occupation of these bands depends on the temperature according to the Fermi-Dirac

Figure 3.4.: In a CVD reactor, incoming process gases, usually methane and hydrogen, are activated by a microwave plasma. The carbon radicals formed by this reaction are then deposited onto a substrate, where diamond can grow under the right conditions. Figure taken from Ref. [27].

distribution[25, 31, 63]:

$$f(E) = \frac{1}{\exp\left(\frac{E - E_{\rm f}}{k_{\rm B}T}\right) + 1}.$$

(3.4)

The Fermi energy,  $E_{\rm F}$ , corresponds to the highest energy level that would be occupied in the absence of thermal excitations ( $T=0\,\rm K$ ). The energy bands directly above and below  $E_{\rm F}$  are referred to as valence and conduction band, respectively. Fig. 3.6 shows several possible configurations of these bands in relation to the Fermi energy. These correspond to different classes of solids in terms of electrical conductivity: In conductors the Fermi level does not fall into the band gap, either because the two bands overlap or  $E_{\rm F}$  lies within the conduction band. Electrons can easily transition between states within one band due to the small energy differences. An electric field can therefore impart energy and momentum onto these charge carriers. Macroscopically, this movement can be observed as electrical current. This band structure is characteristic of metals and explains the high conductivity of these materials.

However, the Fermi level can also lie in the band gap between valance and conduction band. For materials with large band gaps,

$$\Delta E \gg k_{\rm B}T$$

,

the valance band is completely filled, and the conduction band is empty. In absence of thermal excitations, no electron has sufficient energy to cross the band gap. An electric field cannot impart energy on electrons in the completely filled energy band, because there are no free states in the band left for the electrons to transition into. Hence, no current flow is possible, and the material is considered an *insulator*. However, a fraction of electrons according to eq. (3.4) are excited thermally and transition from the valence

Figure 3.5.: Scanning electron microscopy image showing a CVD diamond film with a thickness of 100 µm. It is grown on a silicon substrate with the grain size increasing from the substrate side (bottom) to the growth side (top). Image courtesy of CVD diamond group, School of Chemistry, University of Bristol, UK.

to the conduction band. Here, they contribute as free charge carriers to the conduction of electrical current. Meanwhile, the unoccupied states in the valence band also propagate as positively charged *holes* in the opposite direction of the electrons.

Materials with sufficiently small band gaps, e.g.,  $1.11\,\mathrm{eV}$  for Silicon or  $1.44\,\mathrm{eV}$  for Gallium arsenide[88], are classified as *semiconductors* because a significant amount of free charge carriers are present at room temperature. Typical values for the conductivity lie between  $10^4\,\Omega^{-1}\,\mathrm{cm}^{-1}$  and  $10^{-10}\,\Omega^{-1}\,\mathrm{cm}^{-1}[94]$ .

Thermal excitation is not the only source of free charge carriers in semiconductors. The energy needed to cross the band gap can also be deposited by the interaction of high energy particles with the material as discussed in the previous section 3.1. This way, semiconductors can serve as particle detectors: With the deposited energy, electrons can transition from the valence to the conduction band. This creates free charge carriers in the form of electron-hole pairs in the semiconductor. Not all energy deposited in the medium leads to electrons overcoming the band gap. Therefore, the average energy needed to create an electron hole pair is larger than the band gap of the material. For diamond this value is  $13.1\,\mathrm{eV}[75]$ .

A bias voltage is applied to the sensor to separate and detect the freed charge carriers. According to Ramo's theorem[84], a current  $i_k$  is induced on an electrode, k, by a charge, q, moving with velocity  $\vec{v}$ :

$$i_k = q\vec{F}_{\mathbf{w}} \cdot \vec{v}. \tag{3.5}$$

The latter is a function of the electron and hole mobilities,  $\mu_e$  and  $\mu_h$ . The so-called weighting field  $\vec{F}$  is calculated by removing the charge and setting all electrodes to ground potential (0 V), except for k which is set to  $V_k = 1$  V. Ramo's theorem implies that the

Table 3.1.: Selected physical properties of diamond. For pCVD these values can vary significantly. For comparison with a typical semiconductor values for Silicon are also provided. Temperature-dependent values are given at 300 K.

| Property                   | Diamond      | Silicon               | Unit                    |

|----------------------------|--------------|-----------------------|-------------------------|

| atomic number              | 6            | 14                    |                         |

| atom mass                  | 12.01        | 28.09                 | u                       |

| density                    | 3.51         | 2.328                 | $\rm gcm^{-3}$          |

| crystal structure          | diamond      | diamond               |                         |

| lattice constant           | 3.57         | 5.431                 | Å                       |

| band gap                   | 5.5          | 1.12                  | $\mathrm{eV}$           |

| intrinsic carrier density  | 0            | $1.01 \times 10^{10}$ | $\mathrm{cm}^{-3}$      |

| resistivity                | 1e16         | 2.3e5                 | $\Omega\mathrm{cm}$     |

| avg. energy per (e/h) pair | 13.1         | 3.65                  | eV                      |

| thermal conductivity       | >18          | 1.48                  | ${ m Wcm^{-1}K^{-1}}$   |

| mobility (e)               | $\sim 1800$  | 1450                  | ${ m cm^2V^{-1}s^{-1}}$ |

| mobility (h)               | $\sim 2300$  | 500                   | ${ m cm^2V^{-1}s^{-1}}$ |

| lifetime (e)               | $\sim 0.100$ | >100                  | μs                      |

| lifetime (h)               | $\sim 0.050$ | >100                  | μs                      |

signal is not dependent on the free charge carriers reaching the electrodes. Rather, the charge is continuously collected for the duration of the charge movement. If the charge is lost before reaching the electrode, the remaining signal to be generated is lost. It means that the percentage of collected signal is determined by the charge carriers mean drift distance. This so-called charge collection distance (CCD),

$$CCD = E\left(\mu_{e}\overline{\tau}_{e} + \mu_{h}\overline{\tau}_{h}\right), \tag{3.6}$$

depends on the bias field strength E as well as the charge carrier mobility,  $\mu_{\{e,h\}}$ , and mean drift time  $\bar{\tau}_{\{e,h\}}$ , The charge collection efficiency (CCE) is the ratio of charge detected at the electrodes to the amount of free charge carriers initially created by the ionization process. This value can be estimated from the CCD if the latter is small compared to the spacing of the electrodes, which is usually the case for CVD diamond sensors of typical sizes:

$$CCE = \frac{Q_{\text{ion}}}{Q_{\text{det}}} \approx \frac{CCD}{d}.$$

(3.7)

In pCVD diamond, this lifetime is heavily influenced by the geometric structure of the material because the grain boundaries in the poly crystal create potential wells which trap the charge carriers and therefore reduce the CCD. For individual pCVD samples there can be a significant difference in efficiency due to variations in the grain structure of the diamond. For applications such as the BCM, this reduces the signal current for a given particle flux and noise level. Hence, it is desirable to use sensors with a large CCE. The measurement of the CCE was part of the characterization of the BCM sensors, which was done by the Dortmund group, and is presented in section 4.1 and Ref. [99].

Figure 3.6.: The electrical conductivity of materials is determined by the position of the valence and conduction bands with respect to the Fermi level  $E_{\rm F}$ . For metals, the Fermi level lies within one band or two overlapping bands. If  $E_{\rm F}$  lies in a band gap,  $\Delta E$ , the material is classified as either a semiconductor or insulator depending on the size of  $\Delta E$ .

In addition to the initial grain structure, radiation induced damages also influence the efficiency. Similar to the grain boundaries, these effects also create further trapping centers by introducing additional acceptor and donator levels in the band structure of the diamond. Radiation damage to diamond sensors does not lie within the scope of this thesis. For further details, the reader is referred to Refs. [63, 85].

## 4. Beam Conditions Monitor

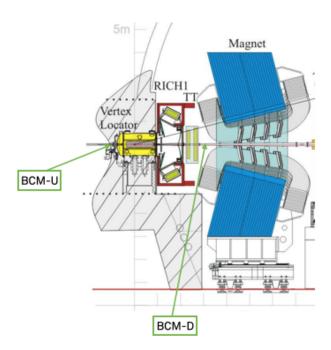

To protect the LHCb experiment from damage due to adverse beam conditions, the detector design incorporates the so called Beam Conditions Monitor (BCM). This safety system monitors the particle flux around the beam pipe at two locations near the LHCb interaction point as seen in Fig. 4.1: One station, BCM-U, is situated at  $z=-2131\,\mathrm{mm}$  on the shielding wall of the VELO alcove as seen in Fig. 4.2a. On the other side, 2765 mm downstream of the IP, the second station, BCM-D, is mounted in the area between the UT and the LHCb dipole magnet, cf. Fig. 4.2b. The BCM has protected the LHCb detector since the beginning of Run I of the LHC in 2008. Ref. [43] describes the original design of the BCM system.

Figure 4.1.: The BCM system consists of two stations placed on the beam pipe: The upstream station (BCM-U) is located in the non-instrumented hemisphere 2131 mm from the IP. The downstream station (BCM-D) is situated between the UT and the magnet at a distance of 2765 mm from the IP. Figure modified from Ref. [70].

At each station, eight polycrystalline CVD sensors are mounted radially around the beam pipe. Diamond is chosen as the sensor material due to its unique properties.

#### 4. Beam Conditions Monitor

(a) BCM-U station located at the shielding wall of the VELO alcove

(b) BCM-D mounted on the beam pipe near the magnet.

Figure 4.2.: The two stations of the BCM are located on either side of the LHCb IP and are mounted an annular support structure. To shield the system from electrical noise, each station is wrapped with copper foil.

Firstly, the sensors should function at ambient temperature. Otherwise, cooling infrastructure would need to be installed at the BCM stations, leading to additional complexity and reduced reliability. In contrast to e.g. silicon sensors, diamond detectors can be operated at higher temperatures due to their relatively low dark currents. Secondly, the BCM stations are located close to the beam pipe and the IP, which exposes them to high radiation doses from the operation of the LHC. Its crystal structure makes diamond sufficiently radiation hard that the sensors can withstand the harsh radiation environment for several years.

Besides the sensors, auxiliary components belong to each station, such as the annular support structure attached to the beam pipe. These components are described in section 4.2 Also, each station features a mini-crate where the diamond connection unit (DCU) is located. The former houses the front-end charge to frequency converter (CFC) card, see section 4.3 and Ref. [36], and its low-voltage power supply. The latter terminates the conductors coming from the sensors, passes the sensor current to the input channels of the CFC card, and supplies the bias voltage (200 V) to the sensors.

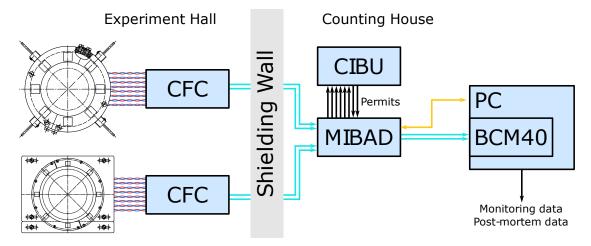

The current measurements acquired by the front-end cards is read out via two redundant optical links each. These systems are situated in the so called D3 barracks, which are separated from the LHCb detector by a 4 m thick concrete shielding wall[105]. This enables access to these systems independent of the LHC operational status, and allows for design of the back-end systems without consideration for radiation hardness.

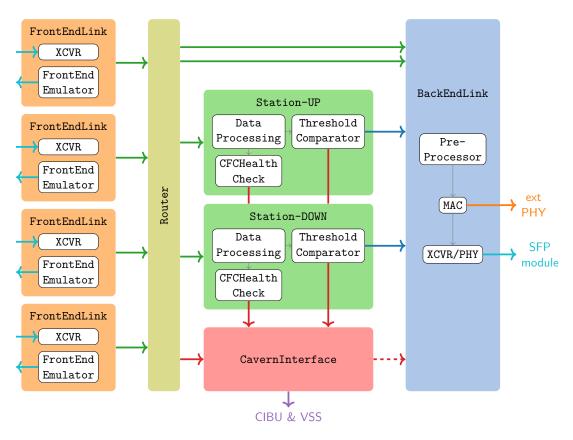

The readout system receives the data frames from the CFC cards via the optical links and decodes them to recover the measured currents. Based on these currents and a set of predefined thresholds, the system determines whether the beam conditions allow for the safe operation of the LHCb detector. If not, a beam abort is triggered via the Controls-Interlocks-Beam-User (CIBU) interface to the LHC[106]. A more complete specification of the readout system and its external interfaces is provided in chapter 5.

For the implementation of the BCM DAQ system, which includes the aforementioned online data processing and beam abort logic, FPGAs are chosen. These integrated circuits provide programmable logic elements, and enable the design of versatile data acquisition and processing systems. The development of the DAQ for the upgraded BCM system is the main aspect of this thesis. Therefore, this work will be presented in three dedicated chapters 6, 7, and 8 for the hardware, firmware, and software aspects of the system, respectively. For setting the above-mentioned thresholds, Monte Carlo simulations of the BCM stations and the VELO have been conducted by the BCM group [87]. An overview of these studies is given at the end of this chapter in section 4.4.

### 4.1. Sensor characterization

During the refurbishment of the BCM system, the stations were outfitted with new diamond sensors. 32 polycrystalline diamonds, with the same specified requirements as the original sensors, have been procured from Element Six Technologies in 2021.

As outlined in section 3.2, the CCE of the sensors varies due to differences in the grain structure of the material. Furthermore, according to Ref. [43], erratic current spikes in the order of several micro amperes were observed in certain sensors of the original BCM. Therefore, a characterization of the sensors is needed to decide which subset to use in the refurbished BCM.

The characterization procedure was developed in the scope of several theses [33, 60, 61]. Eventually, Ref. [99] describes the final test setup and presents measurements on prototype sensors. For the test, a bias voltage of 200 V is applied to each sensor. A time-integrated measurement of sensor currents is performed with a Keitheey 6487 picoammeter [101]. Initially, the dark current of the sensors is measured. Next, the sensors are placed under a <sup>90</sup>Sr source, which provides electrons with an energy of up to 2.3 MeV [15]. Out of the 32 diamonds, the 16 sensors with the highest signal-to-noise ratio were chosen. Diamonds that exhibited erratic behavior were excluded.

#### 4.2. Stations

For optimal coverage of the particle flux around the beam pipe, the sensors are placed symmetrically around it. This is achieved by a mechanical support structure in form of two half rings for each station. For the upstream BCM station, it is mounted on the shielding wall of the VELO alcove. There are many systems located in this area even though it does not lie in the actual acceptance of the LHCb detector. For Run 3, the

#### 4. Beam Conditions Monitor

Figure 4.3.: Mechanical support of BCM-U. One half station mounted on a "sliding door" (dark gray) which runs along two rails located on the shielding wall in the background is shown. This configuration allows the BCM to be moved into and out of the confined space between the shielding wall and the Probe for LUminosity MEasurement (PLUME) detector in the foreground.

PLUME detector [68], which is located just in front of the BCM-U, was installed as an additional luminometer.

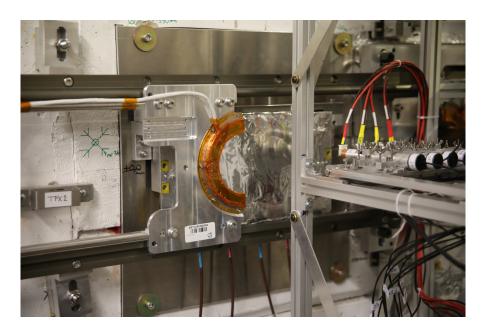

This poses a maintenance challenge for the BCM because there is only a few centimeters of space between the PLUME envelope and the upstream station. To mitigate this, a new support structure was developed by the Dortmund BCM group which is shown in Fig. 4.3. The ring carrying the sensors and PCB is fixed to a machined aluminum plate which is attached to a rail system. This system allows for the station to be opened and moved way from beam pipe and out of the confined space between PLUME and the shielding wall. During beam operation, the areas in the vicinity of the LHCs beams become activated. This is especially relevant for the VELO alcove due to its proximity to the IP. Maintenance work on the BCM may potentially have to take place during short technical stops with little time for the activation of the work area to subside. Following the ALARA<sup>1</sup> principle, the duration of the intervention has to be minimized to keep the doses incurred by maintenance personnel low. Each side of the station can be removed from the guide rails and replaced by a spare part. A second copy of the half plates (including the diamond sensors) was produced by the Dortmund BCM group and serves as a spare for drop-in replacement. From each half station, the sensors are connected via a twisted-pair cable. For this, a standard Category 7 shielded, twisted-pair cable was

<sup>&</sup>lt;sup>1</sup>As Low As Reasonable Achievable

#### 4. Beam Conditions Monitor

Figure 4.4.: Schematic showing the connection of a single sensor to a front-end channel. The low-pass filter is housed in the DCU.

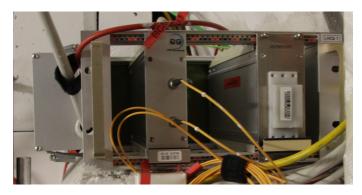

Figure 4.5.: Minicrate housing the front-end card and its power supply. The DCU attached on the left side.

used. The use of standardized cabling has advantages for complying with CERN safety standards and procuring spare material.

For the design of the BCM downstream station, the effect of any material brought into the LHCb acceptance needs to be considered. Any material in this area, especially with a short radiation length  $X_0$ , can lead to interactions with particles in the detector such as multiple scattering and the initiation of particle showers. These effects prevent the tracking and the correct reconstruction of the events which decreases the overall efficiency of the detector. For this reason, the support structure of the downstream station is made from the plastic material Tecapeek instead of aluminum. On this base, the printed circuit boards (PCBs), each of which hold four sensors, are attached by Tecapeek screws. The station can be separated into two parts to place it onto the beam pipe, and it is mechanically secured by clamping it to the support structure of the beam pipe as seen in Fig. 4.2b. To further reduce the material budget, a hand-wound cable with is used to connect the sensors to the front end electronics, which is made from thin twisted Kapton<sup>®</sup> coated copper pairs.

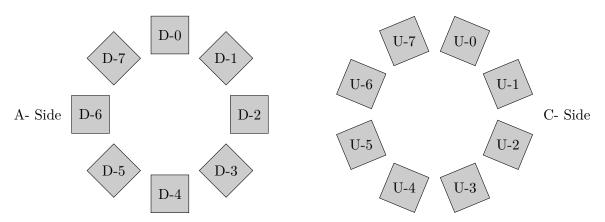

Fig. 4.6 shows the sensors are mounted on a PCB as well as the sensor numbering for both stations. To shield the system from electromagnetic interference (EMI), the sensors at both stations are covered with Kapton<sup>®</sup> coated copper foil. The cables for

### 4. Beam Conditions Monitor

Figure 4.6.: Top: BCM-D station with the shielding foil removed. Numbering scheme for the BCM sensors. When looking along the positive z direction, the channels are numbered increasing counter-clockwise. For the BCM-U, the arrangement is rotated by 22.5° to allow the separation of the half plates of the station. *Nota bene:* The direction shown does not correspond to the physical access to the upstream station. In this case, the channel numbering appears clockwise.

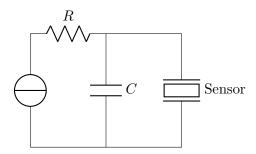

both stations are terminated in the so-called DCU, which supplies the sensors with the bias voltage of  $200\,\mathrm{V}$ , and forwards the current signals to the front-end CFC card. In Fig. 4.4 the schematic of one of the eight DCU channels is shown. For each channel, the bias voltage is filtered via a RC low-pass filter. The DCU is physically attached to the front-end mini crate (as seen in Fig. 4.5), which houses the CFC data acquisition card described in the next section.

Table 4.1.: Specifications of the CFC front-end cards. Data taken from Ref. [36].

| Current measuring range    | $2.5\mathrm{pA}$               | $1\mathrm{mA}$  |

|----------------------------|--------------------------------|-----------------|

| Error down to 10pA         | -50%                           | +100%           |

| Error down to 1nA          | -25%                           | +25%            |

| Maximal input current      | $561\mathrm{m}$                | A               |

| Input voltage peak         | 1 kV at 10                     | )0 μs           |

| Radiation tolerance        | $500\mathrm{Gy}$ in            | 20 yr           |

| Digital supply             | $+2.5{ m V}$                   | 7               |

| Analogue supply            | $\pm 5\mathrm{V}^*$            |                 |

| High-voltage monitor input | $0\mathrm{V}$                  | $+5\mathrm{kV}$ |

| Measurement period         | $40\mathrm{\mu s}$             |                 |

| Output data rate           | $800  \rm Mbit  s^{-1}  (8b1)$ | 0b encoded)     |

|                            |                                |                 |

### 4.3. Front-end electronics

The signal of the diamond sensors is a current, which is proportional to the particle flux through the sensors. This current needs to be periodically measured and the resulting data must be digitized, which is the role of the front-end (FE) electronics. For the BCM, the choice was made to use DAQ cards originally used for the LHC BLM[36]. This readout-card, in this document referred to as CFC or front-end card, allows for the measurement of 8 channels with a large dynamic range. It features radiation tolerant electronics in a robust, compact form factor. Table 4.1 provides the main design specifications of the CFC cards.

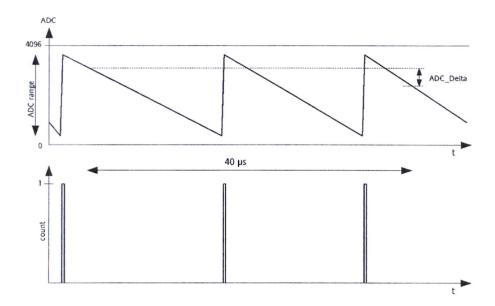

The main component of the FE card is a so-called charge to frequency converter (CFC), the operation of which is illustrated by Fig. 4.7. In this setup, the signal current is fed into an operational amplifier-driven integrator circuit. When the capacitor of the integrator reaches a certain charge, it is discharged to reset the integrator. To determine the current, the number of these charge-discharge cycles per the measurement period are counted and hence the charge per 40 µs is determined. For the BCM card, a frequency of 25 kHz, i.e., one cycle per measurement period, corresponds to a signal current of 5 µA.

To increase the resolution of the CFC, especially in the low current regime, a 12 bit analog-to-digital converter (ADC) is used to sample the integrator level at the end of a readout period. For a constant input current, the integrator level of the CFC card follows a saw tooth waveform. The current can be recovered from the count and the difference of two consecutive ADC values:

$$I(t_i) = 5 \,\mu\text{A} \left( \text{counts}(t_i) + \frac{\text{ADC}(t_{i-1}) - \text{ADC}(t_i)}{\text{ADC}_{\text{range}}} \right). \tag{4.1}$$

In principle, the  $ADC_{\rm range}$  in eq. (4.1) would be 4096, given by the width of the 12 bit ADC. However, in reality, this value is lower as the integrator output does not sweep the ADC completely. For this reason,  $ADC_{\rm range}$  needs to be empirically determined by the DAQ system for every channel.

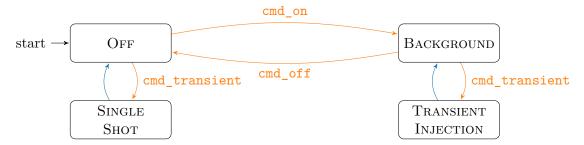

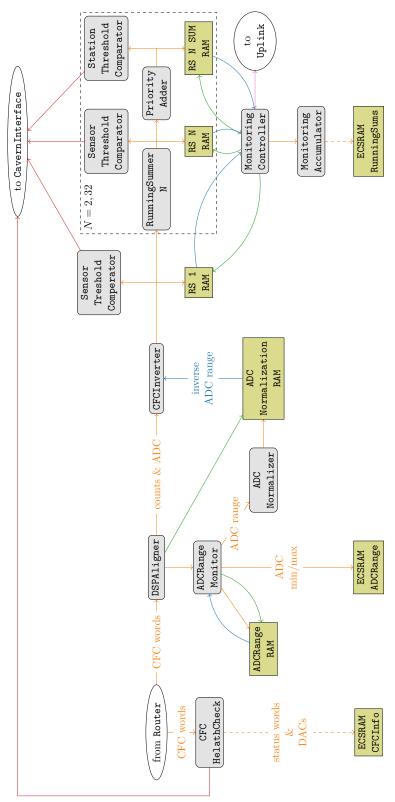

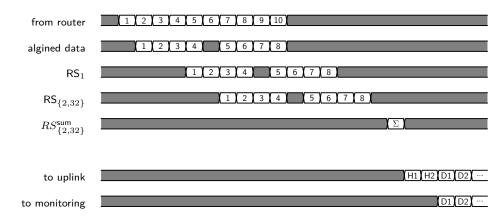

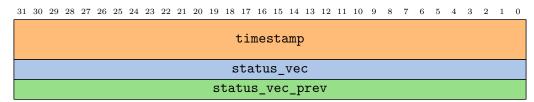

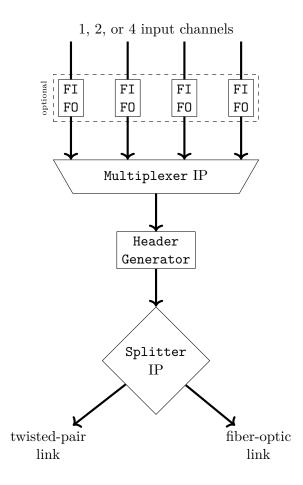

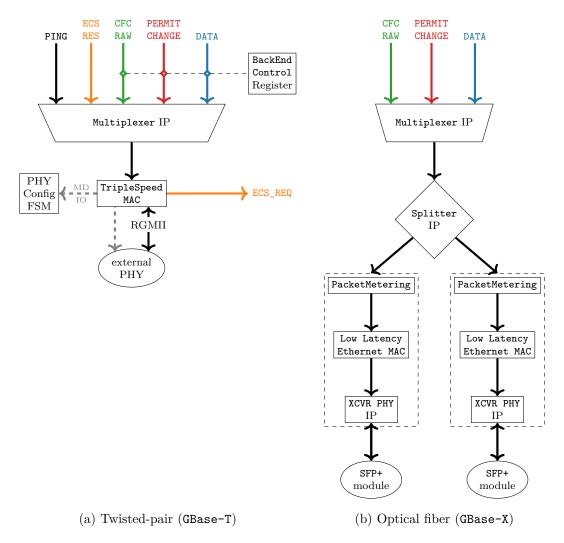

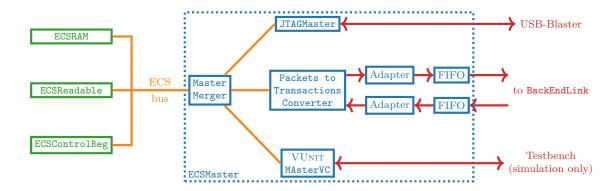

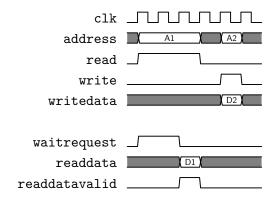

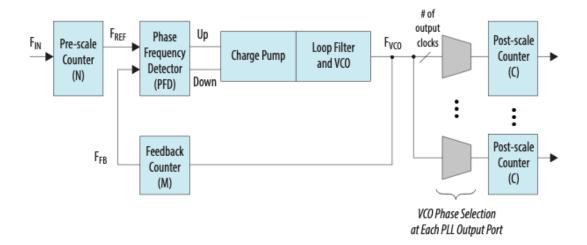

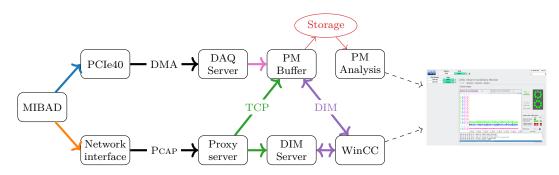

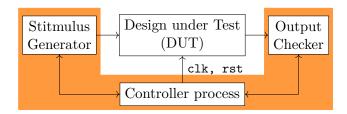

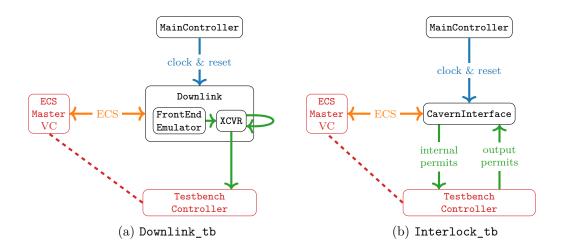

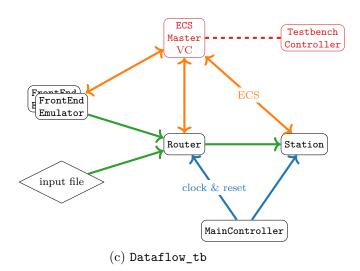

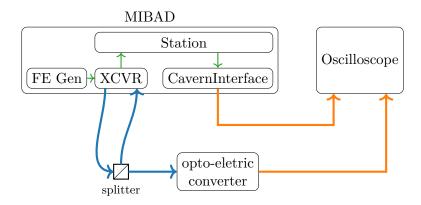

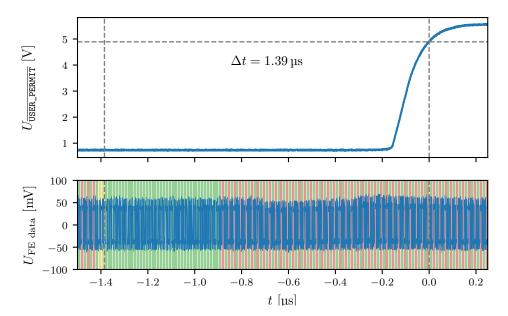

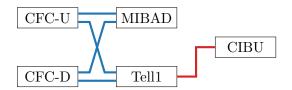

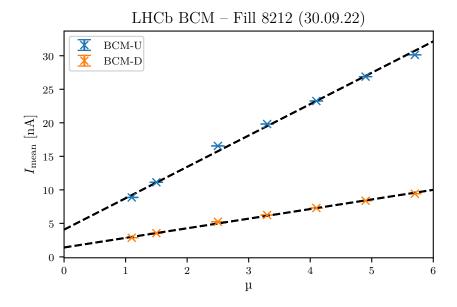

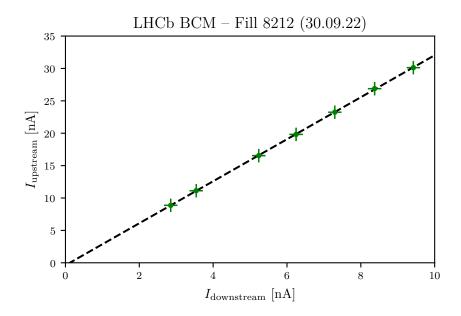

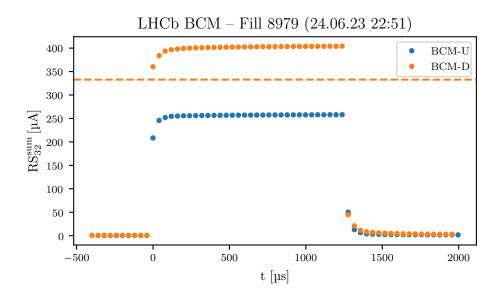

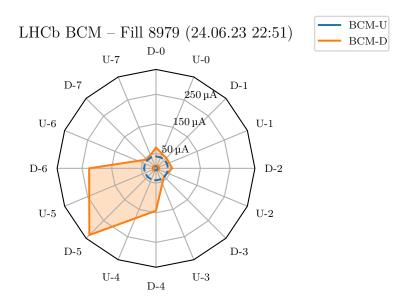

Figure 4.7.: Exemplary waveform of the CFC card's integrator level. In this case, three cycles occurred during the measurement period shown. Figure taken from Ref. [36].