## Efficient Fault-Injection-based Assessment of Software-Implemented Hardware Fault Tolerance

### Dissertation

zur Erlangung des Grades eines

Doktors der Ingenieurwissenschaften

der Technischen Universität Dortmund an der Fakultät für Informatik

von

Horst Benjamin Schirmeier

Dortmund

2016

| Tag der mündlichen Prüfung: | 13. Juli 2016              |

|-----------------------------|----------------------------|

| Dekan:                      | Prof. DrIng. Gernot Fink   |

| Gutachter:                  | Prof. DrIng. Olaf Spinczyk |

|                             | Prof. Dr. Andreas Polze    |

#### ABSTRACT

With continuously shrinking semiconductor structure sizes and lower supply voltages, the per-device susceptibility to transient and permanent hardware faults is on the rise. A class of countermeasures with growing popularity is *Software-Implemented Hardware Fault Tolerance* (SIHFT), which avoids expensive hardware mechanisms and can be applied application-specifically. However, SIHFT can, against intuition, cause more harm than good, because its overhead in execution time and memory space also increases the figurative "attack surface" of the system – it turns out that application-specific configuration of SIHFT is in fact a necessity rather than just an advantage.

Consequently, target programs need to be *analyzed* for particularly critical spots to harden. SIHFT-hardened programs need to be *measured and compared* throughout all development phases of the program to observe reliability improvements or deteriorations over time. Additionally, SIHFT implementations need to be *tested*.

The contributions of this dissertation focus on *Fault Injection* (FI) as an assessment technique satisfying all these requirements – *analysis, measure-ment and comparison*, and *test*. I describe the design and implementation of an FI tool, named FAIL\*, that overcomes several shortcomings in the state of the art, and enables research on the general drawbacks of simulation-based FI. As demonstrated in four case studies in the context of SIHFT research, FAIL\* provides novel fine-grained analysis techniques that exploit the newly gained possibility to analyze FI results from *complete* fault-space exploration. These analysis techniques aid SIHFT design decisions on the level of program modules, functions, variables, source-code lines, or single machine in-structions.

Based on the experience from the case studies, I address the problem of large computation efforts that accompany exhaustive fault-space exploration from two different angles: Firstly, I develop a heuristical fault-space pruning technique that allows to freely trade the total FI-experiment count for result accuracy, while still providing information on *all* possible faultspace coordinates. Secondly, I speed up individual TAP-based FI experiments by improving the fast-forwarding operation by several orders of magnitude for most workloads. Finally, I dissect current practices in FI-based evaluation of SIHFT-hardened programs, identify three widespread pitfalls in the result interpretation, and advance the state of the art by defining a novel comparison metric.

#### PUBLICATIONS

Parts of this thesis have been published in the following peer-reviewed journal, conference and international workshop papers:

**Horst Schirmeier**, Rüdiger Kapitza, Daniel Lohmann, and Olaf Spinczyk. DanceOS: Towards dependability aspects in configurable embedded operating systems. In Alex Orailoglu, editor, *Proceedings of the 3rd HiPEAC Workshop on Design for Reliability (DFR '11)*, pages 21–26, Heraklion, Greece, January 2011. [SKLS11]

**Horst Schirmeier**, Jens Neuhalfen, Ingo Korb, Olaf Spinczyk, and Michael Engel. RAMpage: Graceful degradation management for memory errors in commodity Linux servers. In *Proceedings of the 17th IEEE Pacific Rim International Symposium on Dependable Computing (PRDC '11)*, pages 89–98, Pasadena, CA, USA, December 2011. IEEE Computer Society Press. doi: 10.1109/PRDC.2011.20. [SNK<sup>+</sup>11]

**Horst Schirmeier**, Martin Hoffmann, Rüdiger Kapitza, Daniel Lohmann, and Olaf Spinczyk. Revisiting fault-injection experiment-platform architectures. In *Proceedings of the 17th IEEE Pacific Rim International Symposium on Dependable Computing (PRDC '11)*, pages 284–285, Pasadena, CA, USA, December 2011. IEEE Computer Society Press. Fast abstract. doi: 10.1109/PRDC.2011.46. [SHK<sup>+</sup>11]

**Horst Schirmeier**, Martin Hoffmann, Rüdiger Kapitza, Daniel Lohmann, and Olaf Spinczyk. FAIL\*: Towards a versatile fault-injection experiment framework. In Gero Mühl, Jan Richling, and Andreas Herkersdorf, editors, *25th International Conference on Architecture of Computing Systems (ARCS '12), Workshop Proceedings*, volume 200 of *Lecture Notes in Informatics*, pages 201–210. German Society of Informatics, March 2012. [SHK<sup>+</sup>12]

Christoph Borchert, **Horst Schirmeier**, and Olaf Spinczyk. Protecting the dynamic dispatch in C++ by dependability aspects. In *Proceedings of the 1st GI Workshop on Software-Based Methods for Robust Embedded Systems (SOBRES '12)*, Lecture Notes in Informatics, pages 521–535. German Society of Informatics, September 2012. [BSS12]

Björn Döbel, **Horst Schirmeier**, and Michael Engel. Investigating the limitations of PVF for realistic program vulnerability assessment. In *Proceedings of the 5th HiPEAC Workshop on Design for Reliability (DFR '13)*, Berlin, Germany, January 2013. [DSE13]

**Horst Schirmeier**, Ingo Korb, Olaf Spinczyk, and Michael Engel. Efficient online memory error assessment and circumvention for Linux with RAMpage. *International Journal of Critical Computer-Based Systems*, 4(3):227–247, 2013. Special Issue on PRDC 2011 Dependable Architecture and Analysis. doi: 10.1504/IJCCBS.2013. 058397. [SKSE13]

Christoph Borchert, **Horst Schirmeier**, and Olaf Spinczyk. Generative softwarebased memory error detection and correction for operating system data structures. In Proceedings of the 43rd IEEE/IFIP International Conference on Dependable Systems and Networks (DSN '13), Washington, DC, USA, June 2013. IEEE Computer Society Press. doi: 10.1109/DSN.2013.6575308. [BSS13a]

Christoph Borchert, **Horst Schirmeier**, and Olaf Spinczyk. Return-address protection in C/C++ code by dependability aspects. In *Proceedings of the 2nd GI Workshop on Software-Based Methods for Robust Embedded Systems (SOBRES '13)*, Lecture Notes in Informatics. German Society of Informatics, September 2013. [BSS13b]

Martin Hoffmann, Peter Ulbrich, Christian Dietrich, **Horst Schirmeier**, Daniel Lohmann, and Wolfgang Schröder-Preikschat. A practitioner's guide to softwarebased soft-error mitigation using AN-codes. In *Proceedings of the 15th IEEE International Symposium on High Assurance Systems Engineering (HASE '14)*, pages 33– 40, Miami, Florida, USA, January 2014. IEEE Computer Society Press. doi: 10.1109/ HASE.2014.14. [HUD<sup>+</sup>14b]

**Horst Schirmeier**, Lars Rademacher, and Olaf Spinczyk. Smart-hopping: Highly efficient ISA-level fault injection on real hardware. In *Proceedings of the 19th IEEE European Test Symposium (ETS '14)*, pages 69–74. IEEE Computer Society Press, May 2014. doi: 10.1109/ETS.2014.6847803. [SRS14]

Martin Hoffmann, Christoph Borchert, Christian Dietrich, **Horst Schirmeier**, Rüdiger Kapitza, Olaf Spinczyk, and Daniel Lohmann. Effectiveness of fault detection mechanisms in static and dynamic operating system designs. In *Proceedings of the 17th IEEE International Symposium on Object-Oriented Real-Time Distributed Computing (ISORC '14)*, pages 230–237. IEEE Computer Society Press, June 2014. doi: 10.1109/ISORC.2014.26. [HBD<sup>+</sup>14]

**Horst Schirmeier**, Christoph Borchert, and Olaf Spinczyk. Rapid fault-space exploration by evolutionary pruning. In *Proceedings of the 33rd International Conference on Computer Safety, Reliability and Security (SAFECOMP '14)*, Lecture Notes in Computer Science, pages 17–32. Springer-Verlag, September 2014. doi: 10.1007/978-3-319-10506-2\_2. [SBS14]

Martin Hoffmann, Peter Ulbrich, Christian Dietrich, **Horst Schirmeier**, Daniel Lohmann, and Wolfgang Schröder-Preikschat. Experiences with software-based soft-error mitigation using AN codes. *Software Quality Journal*, pages 1–27, November 2014. doi: 10.1007/s11219-014-9260-4. [HUD<sup>+</sup>14a]

Horst Schirmeier, Christoph Borchert, and Olaf Spinczyk. Avoiding pitfalls in fault-injection based comparison of program susceptibility to soft errors. In *Proceedings of the 45th IEEE/IFIP International Conference on Dependable Systems and Networks (DSN '15)*, pages 319–330, Washington, DC, USA, June 2015. IEEE Computer Society Press. doi: 10.1109/DSN.2015.44. [SBS15]

Christoph Borchert, **Horst Schirmeier**, and Olaf Spinczyk. Generic soft-error detection and correction for concurrent data structures. *IEEE Transactions on Dependable and Secure Computing*, PP(99), 2015. Pre-print. doi: 10.1109/TDSC.2015.2427832. [BSS15]

Horst Schirmeier, Martin Hoffmann, Christian Dietrich, Michael Lenz, Daniel Lohmann, and Olaf Spinczyk. FAIL\*: An open and versatile fault-injection frame-

work for the assessment of software-implemented hardware fault tolerance. In *Proceedings of the 11th European Dependable Computing Conference (EDCC '15)*, pages 245–255. IEEE Computer Society Press, September 2015. doi: 10.1109/EDCC.2015.28. [SHD<sup>+</sup>15]

Thiago Santini, Christoph Borchert, Christian Dietrich, **Horst Schirmeier**, Martin Hoffmann, Olaf Spinczyk, Daniel Lohmann, Flávio Rech Wagner, and Paolo Rech. Evaluating the radiation reliability of dependability-oriented real-time operating systems. In *Proceedings of the 12th Workshop on Silicon Errors in Logic – System Effects (SELSE '16)*, March 2016. [SBD<sup>+</sup>16]

First and foremost I want to thank my advisor Prof. Dr.-Ing. Olaf Spinczyk, who has repeatedly encouraged me during our time in Erlangen to follow him to Dortmund, and to start working in research. Without his continued support, advice, and funding, this thesis would not exist. I would also like to thank Prof. Dr. Andreas Polze for his time and commitment to review this thesis.

Over the years of researching, teaching, publishing, and networking, I met and collaborated with many excellent people. Jochen Streicher has been sharing my office since the first day, and I guess every single part of my work has been influenced by some piece of advice or a result of a discussion with him. Michael Engel always provided advice, and words of encouragement when I needed them.

In the context of the SPP-1500 *DanceOS* project,<sup>1</sup> I had the pleasure to work with Daniel Lohmann and Rüdiger Kapitza, who helped focusing my research on what finally led to this dissertation.

Then there are, of course, all the FAIL\* guys. Martin Hoffmann launched the first FAIL\* prototype together with me, and he has since continuously contributed additional components, plugins, the T<sub>32</sub> simulator back-end, or manpower in person of his student assistants. Among many other details, Christian Dietrich helped turning my assessment-cycle layer tool prototypes into the form they are in today. Christoph Borchert was among the first FAIL\* users, and our profound discussions on fault tolerance and fault injection have been essential for many of the findings in this dissertation. Björn Döbel provided several really challenging use cases, resulting in several years of enjoyable collaboration and occasional late-night discussions at varying SPP meetings. My student assistants Adrian Böckenkamp, Richard Hellwig, and Michael Lenz also put lots of work into FAIL\*, just as my students Tobias Friemel and Lars Rademacher. Without these contributors, FAIL\* would not be where it is today – thank you, guys!

Additionally, I would like to thank several people for helpful – professional or personal – discussions and the occasional coffee-machine chatter, without which the LS12 respectively CS-faculty working environment would have been a different place: Alexander, Andreas, Björn, Boguslaw, Florian, Georg, Helena, Hendrik, Ingo (in particular also for his work on RAMpage), Jan, Kuan, Matthias, Markus, Olaf, Patrick, and Thomas.

Last, but certainly not least, I would like to thank my family – especially my parents for having supported me since day one, and my wife Steffi for coping with the by-products of my thesis writing, for hugs when needed the most, and for everything else.

<sup>1</sup> This work was partly supported by the German Research Foundation (DFG) priority program SPP 1500 under grants no. SP 968/5-1, SP 968/5-2, and SP 968/5-3.

#### CONTENTS

| 1 | INT  | RODUCTION 1                                                   |

|---|------|---------------------------------------------------------------|

|   | 1.1  | Software-Implemented Hardware Fault Tolerance 2               |

|   | 1.2  | Fault Injection: Tools, Techniques, and Contributions of this |

|   |      | Dissertation 3                                                |

|   | 1.3  | Outline 12                                                    |

|   | 1.4  | Author's Contribution to this Dissertation 13                 |

| 2 | HAR  | DWARE FAULTS AND FAULT-TOLERANT COMPUTING 17                  |

|   | 2.1  | Moore's Law and the Evolution of Semiconductor Technol-       |

|   |      | ogy 18                                                        |

|   | 2.2  | Dependable Systems: Attributes, Threats, and Means 19         |

|   | 2.3  | Hardware Faults at the Transistor Level 24                    |

|   | 2.4  | Fault-Tolerant Computing 34                                   |

|   | 2.5  | Summary 45                                                    |

| 3 | FAU  | LT TOLERANCE ASSESSMENT AND HARDWARE FAULT IN-                |

|   | JECT | ΓΙΟΝ 47                                                       |

|   | 3.1  | Fault Injection 48                                            |

|   | 3.2  | Fault-Injection Tools and Techniques 59                       |

|   | 3.3  | Fault-Injection Optimizations 68                              |

|   | 3.4  | Alternative Analysis Techniques 75                            |

|   | 3.5  | Summary: Observations and Gaps in the State of the Art 77     |

| 4 | FAII | L*: A VERSATILE FAULT-INJECTION FRAMEWORK 83                  |

|   | 4.1  | Design Goals 84                                               |

|   | 4.2  | FAIL <sup>*</sup> Overview 86                                 |

|   | 4.3  | Plumbing Layer: Back-End Abstraction and Extension 87         |

|   | 4.4  | Case Study: RAMpage 99                                        |

|   | 4.5  | Assessment-Cycle Layer: Fault-Model Defaults, Pruning, and    |

|   |      | Tool Support 107                                              |

|   | 4.6  | Case Study: Generic Object Protection 118                     |

|   | 4.7  | Case Study: Return-Address Protection 127                     |

|   | 4.8  | Case Study: WSOS / Bare-Metal-Sort 137                        |

|   | 4.9  | Discussion 144                                                |

|   | 4.10 | Summary 146                                                   |

| 5 | FAU  | LT-SIMILARITY PRUNING: CAMPAIGN SPEEDUP BY EXPERIMENT-        |

|   | COU  | INT REDUCTION 149                                             |

|   | 5.1  | The Need for Full Fault-Space Coverage 150                    |

|   | 5.2  | Generalizing Fault Equivalence 151                            |

|   | 5.3  | Implementation 158                                            |

|   | 5.4  | Evaluation 161                                                |

|   | 5.5  | Summary and Conclusions 167                                   |

| 6 | SMA  | RT-HOPPING: CAMPAIGN SPEEDUP BY SINGLE-EXPERIMENT             |

|   | ACC  | ELERATION 169                                                 |

|   | 6.1  | Fast-Forwarding: State of the Art 170                         |

xi

- 6.2 Smart-hopping: Choosing the Shortest Path 173

- 6.3 Implementation 175

- 6.4 Evaluation 177

- 6.5 Discussion 179

- 6.6 Summary and Conclusions 184

- 7 COMPARISON OF PROGRAM SUSCEPTIBILITY TO SOFT ERRORS 185

- 7.1 Setting the Stage: Machine, Fault, and Failure Model 186

- 7.2 Experiment-Count Reduction Pitfalls 187

- 7.3 Fooling Fault Coverage: A Gedankenexperiment 193

- 7.4 Constructing an Objective Comparison Metric 197

- 7.5 Discussion and Generalization 201

- 7.6 Related Work 203

- 7.7 Conclusions 204

- 8 CONCLUSIONS AND OUTLOOK 207

- 8.1 Summary 208

- 8.2 Ongoing and Future Work 212

- 8.3 Final Remarks 214

#### Appendix 215

List of Figures 217 List of Tables 218 Listings 219

BIBLIOGRAPHY 221

| ABFT | Algorithm-Based Fault<br>Tolerance          | DRAM  | Dynamic Random-Access<br>Memory               |

|------|---------------------------------------------|-------|-----------------------------------------------|

| ABS  | Anti-lock Braking System                    | DUE   | Detected Unrecoverable<br>Error               |

| ACE  | Architecturally Correct<br>Execution        | DUEC  | Def/Use Equivalence Class                     |

| ALU  | Arithmetic Logic Unit                       | ECC   | Error-Correcting Code                         |

| ANN  | Artificial Neural Network                   | ECCA  | Enhanced CCA                                  |

| AOP  | Aspect-Oriented<br>Programming              | EDC   | Egregious Data<br>Corruption                  |

| API  | Application Programming<br>Interface        | EDDI  | Error Detection by<br>Duplicated Instructions |

| AVF  | Architectural<br>Vulnerability Factor       | EDM   | Error-Detection<br>Mechanism                  |

| AVI  | Application Vulnerability<br>Index          | EEA   | Execution-Environment<br>Abstraction          |

| BB   | Basic Block                                 | EF    | Effective Number of<br>Failures               |

| BEEC | Block Entry Exit Checking                   | EMI   | Electromagnetic                               |

| BER  | Backward Error Recovery                     |       | Interference                                  |

| BSSC | Block Signature Self<br>Checking            | ERM   | Error-Recovery<br>Mechanism                   |

| CCA  | Control-flow Checking                       | FEC   | Forward Error Correction                      |

|      | using Assertions                            | FER   | Forward Error Recovery                        |

| CFE  | Control-Flow Error                          | FI    | Fault Injection                               |

| CFG  | Control-Flow Graph                          | FIT   | Failure In Time                               |

| CFM  | Control-Flow Monitoring                     | FPGA  | Field-Programmable Gate                       |

| CMOS | Complementary Metal-<br>Oxide-Semiconductor |       | Array                                         |

| CMD  |                                             | FSC   | Fault-Similarity Class                        |

| СМР  | Chip-level<br>Multiprocessing               | FSP   | Fault-Similarity Pruning                      |

| COTS | Commercial Off-The-Shelf                    | FVI   | Function Vulnerability<br>Index               |

| CPU  | Central Processing Unit                     | GOP   | Generic Object Protection                     |

| CRC  | Cyclic Redundancy Check                     | HCI   | Hot Carrier Injection                         |

| DFT  | Dilution Fault Tolerance                    | IGFET | Insulated-Gate<br>Field-Effect Transistor     |

| DMR  | Dual-Modular<br>Redundancy                  | IR    | Intermediate<br>Representation                |

| ISA    | Instruction-Set                          | RMSE    | Root Mean Squared Error                          |

|--------|------------------------------------------|---------|--------------------------------------------------|

| IVI    | Architecture                             | RMT     | Redundant<br>MultiThreading                      |

| 1 V I  | Instruction Vulnerability<br>Index       | RTL     | Register-Transfer Level                          |

| JIT    | Just-In-Time                             | SBU     | -                                                |

| LANSCE | Los Alamos Neutron                       |         | Single-Bit Upset                                 |

|        | Science CEnter                           | SDC     | Silent Data Corruption                           |

| MBU    | Multiple-Bit Upset                       | SECDED  | Single-Error Correct<br>Double-Error Detect      |

| MCU    | Multiple-Cell Upset                      | SEE     | Single-Event Effect                              |

| MISFET | Metal-Insulator-                         | SER     | Soft-Error Rate                                  |

|        | Semiconductor<br>Field-Effect Transistor | SEU     | Single Event Upset                               |

| MITF   | Mean Instructions To<br>Failure          | SIHFT   | Software-Implemented<br>Hardware Fault Tolerance |

| MMU    | Memory-Management<br>Unit                | SMP     | Symmetric<br>Multiprocessing                     |

| MOSFET | Metal-Oxide-<br>Semiconductor            | SMT     | Simultaneous<br>Multithreading                   |

|        | Field-Effect Transistor                  | SOI     | Silicon-On-Insulator                             |

| MPU    | Memory-Protection Unit                   | SoR     | Sphere of Replication                            |

| MTBF   | Mean Time Between<br>Failures            | SQL     | Structured Query<br>Language                     |

| MTTF   | Mean Time To Failure                     | SRAM    | Static Random-Access                             |

| MTTR   | Mean Time To Repair                      |         | Memory                                           |

| MWBF   | Mean Workload Between<br>Failures        | SRT     | Simultaneous and<br>Redundantly Threaded         |

| MWTF   | Mean Work To Failure                     | SWIFI   | Software-Implemented<br>Fault Injection          |

| NBTI   | Negative Bias<br>Temperature Instability | ТАР     | Test-Access Port                                 |

| NMR    | N-Modular Redundancy                     | TMR     | Triple-Modular<br>Redundancy                     |

| OCD    | On-Chip Debugger                         | τοςττου | Time-of-Check-to-Time-                           |

| ODD    | Optimum Data<br>Duplication              |         | of-Use                                           |

| PVF    | Program Vulnerability                    | TTF     | Time To Failure                                  |

|        | Factor                                   | VM      | Virtual Machine                                  |

| RAP    | Return-Address Protection                | WSOS    | Winter School on                                 |

| RECCO  | REliable Code COmpiler                   |         | Operating Systems                                |

#### INTRODUCTION

#### Contents

| 1.1 | Softwar              | e-Implemented Hardware Fault Tolerance <b>2</b>                          |

|-----|----------------------|--------------------------------------------------------------------------|

| 1.2 | Fault In<br>sertatio | jection: Tools, Techniques, and Contributions of this Dis-<br>n <b>3</b> |

|     | 1.2.1                | Fault Injection 4                                                        |

|     | 1.2.2                | Fault-Space Exploration and the Fault-Injection Tool Land-               |

|     |                      | scape 5                                                                  |

|     | 1.2.3                | Fault-Injection Campaign Runtimes 8                                      |

|     | 1.2.4                | Fault-Space Pruning 8                                                    |

|     | 1.2.5                | Reducing Experiment Runtime on Real Hardware 10                          |

|     | 1.2.6                | Measuring and Comparing Program Susceptibility to Soft                   |

|     |                      | Errors 10                                                                |

|     | 1.2.7                | Fine-Grained Post-Injection Analysis and Result Visual-                  |

|     |                      | ization 11                                                               |

| 1.3 | Outline              | 12                                                                       |

| 1.4 | Author               | 's Contribution to this Dissertation 13                                  |

**T**<sup>N</sup> THE DECADES since the invention of semiconductor-based integrated circuits [Kil76], computer systems have pervaded all areas of technology. Fueled by constantly progressing miniaturization [Int13] accompanied by plummeting per-transistor prizes [Sch97], and – compared to earlier tube-based solutions – massively lower weight and energy consumption, computers have become omnipresent even in safety domains such as automotive, avionics, or space flight. In these domains, computing hardware and software not only must satisfy common nonfunctional requirements on properties such as *cost* and *energy efficiency*, but also *timeliness* and especially *dependability*.

As chip technology is continuously moving towards higher densities and lower operating voltages [Int13], its sensitivity to hardware faults caused by electromagnetic radiation, interfering impulses, aging and thermal effects, and process variations also increases dramatically [Cono2, SKK<sup>+</sup>o2, Cono3, Cono5, Boro5, Bauo5b, NXo6, DYdS<sup>+</sup>10, DW11]. Consequently, every new generation of hardware designs for embedded systems exhibits an increasing rate of permanent (remaining for indefinite periods), intermittent (reappearing after their first occurrence), and transient (appearing, and disappearing) hardware faults [Muko8].

Today, the magnitude of these effects are far from purely academic but can be observed in all areas of computing. For example, Santini et al. [SRCRW15] estimate 175,000 user-observable errors per year on iPhone 3 devices used Chapter 2 sheds more light on causes and effects of hardware faults. aboard airplanes, caused by cosmic radiation. With much more severe outcomes – including at least 89 casualties [CBS10], and monetary losses beyond one billion U.S. dollars for the car manufacturer, – several Toyota car models were reported to rarely accelerate unintendedly in the years between 2000 to 2010. Although the exact cause could not be proven, radiation-induced bit flips – and a lack of protection against them – were assumed to be probable culprits [Yos13, Wik13]. But even outside the world of embedded systems, for example in data centers [HSS12] or large-scale scientific computing [SG10], reports of hardware faults have accumulated over the years.

At the hardware-software boundary, the previously maintained illusion of always correctly functioning hardware vanishes step by step [HBB<sup>+</sup>11]. This trend towards what has been termed the "soft-error wall" [Muko8] or "reliability wall" [BJS07] creates new challenges for the development of reliable embedded systems, such as automotive control units. As a reaction to these new threats, certification authorities demand explicit measures to cope with transient faults in their functional safety standards, such as IEC 61508 [IEC98] or ISO 26262 [ISO11]. However, for cost-sensitive mass products – such as cars – manufacturers cannot deploy full-fledged hardware redundancy mechanisms. Examples for such hardware mechanisms are triplemodular redundant components with an additional voter, as common in avionic systems, or memory protected with an *Error-Correcting Code* (ECC) [Muko8, RTSM11].

Before dissecting the state of the art in fault injection, and identifying gaps therein that lead to the contributions of this dissertation in Section 1.2, the following Section 1.1 provides the motivating context for this dissertation – *software-implemented* hardware fault tolerance. Section 1.3 provides an outline for this dissertation, and Section 1.4 gives an overview of my own contributions to research results obtained in cooperation with other researchers.

#### 1.1 SOFTWARE-IMPLEMENTED HARDWARE FAULT TOLERANCE

A primary reason for the high cost of hardware-implemented fault tolerance is its generality, or, in other words, its obliviousness to application demands. For example, the redundancy necessary for the ECC protects memory cells regardless of the criticality of their contents for the application to function within parameters. This waste of resources cannot be avoided in *Commercial Off-The-Shelf* (COTS) systems if fault tolerance is implemented on the hardware level. Another argument against hardware-implemented fault tolerance is its severe impact on performance and energy consumption: For example, the developers of the ARGOS satellite concluded that their radiationhardened hardware was simply too slow for the "data processing job intended for it" [LWW<sup>+</sup> o2].

Instead, the problem has to be dealt with – at least partially – in the software [HBB<sup>+</sup>11]. To not diminish all gains from the aforementioned higher chip densities and lower operating voltages, embedded-software developers have to *selectively* place application-specific error detection [Hiloo, HJSo2a, OSMo2, NVo3, RCV<sup>+</sup>o5b, SHLR<sup>+</sup>o9, LCP<sup>+</sup>o9, HAN12] and recovery mechanisms [CCK<sup>+</sup>o6, PGZo8, BSS12, BSS13a, BSS13b, RMCJ13, HBD<sup>+</sup>14] (EDMs/ ERMs) in their mixed-criticality systems. Critical tasks and sensitive spots in the software stack must be hardened against hardware faults, while the remaining – less critical – components economize resource consumption by occasionally tolerating incorrect results.

The necessity to detect and recover from faults on the software level is not a vague possibility for the future anymore. For example, the German semiconductor manufacturer Infineon Technologies AG has been advocating PRO-SIL<sup>™</sup> [Kono8] – a library of SIHFT mechanisms – as a means complementary to the hardware mechanisms in their TriCore<sup>®</sup> embedded microcontroller architecture.

However, experience shows that the development and placement of EDMs/ ERMs is a difficult task in practice. Against intuition, software-based faulttolerance measures often cause more harm than good [GSRo5, MCR<sup>+</sup>12, BSS13a, SRJW14, SBS15], as their overhead in time and space also increases the figurative "attack surface" of the system for adverse environmental effects. Besides the measures' effectiveness and efficiency, especially their placement in the target system – the choice of which data structures or program modules to protect, and which to leave unprotected – is essential for the overall system's resiliency. Furthermore, even small changes to the functional part of the software, such as refactoring a pointer-based linked list into an array-based algorithm, can have dramatic impact on the robustness.

Hence, analogous to common practices in iterative software development, a developer and deployer of fault-tolerance measures must be equipped with techniques and tools to analyze, test, measure, and compare EDM/ERM implementations in their target environment. *Analysis* yields detailed information on the fault sensitivity of specific parts of the program – for example the most critical variables, or program sections, – a basis for the informed placement of fault-tolerance measures. *Testing* allows to find implementation flaws once the measures are placed. *Measurement* in turn allows to quantitatively observe the improvement – or deterioration – of both effectiveness and efficiency of fault-tolerance measures, and is a direct prerequisite for *comparison* of different implementations.

#### 1.2 FAULT INJECTION: TOOLS, TECHNIQUES, AND CONTRIBUTIONS OF THIS DISSERTATION

This dissertation focuses on analysis, testing, measurement, and comparison of hardware-fault resilience of software systems, in particular embedded system software. In this context, I mainly investigate the effect of *transient* hardware faults, also known as *Single Event Upsets* (SEUs) or *soft errors*, that manifest on the software level as single- or multi-bit faults – also known as *bit flips* – in main memory or in CPU registers. This section describes the

Section 2.4 explains more in detail how countermeasures against hardware faults work. problem statement and the chosen approach involving *Fault Injection* (FI) in detail, and explicitly lists the contributions of this dissertation, including

- the design and implementation of an FI tool that eliminates several shortcomings widespread in existing tools and the literature,

- two techniques to significantly speed up FI campaigns and experiments,

- a metric properly interpreting FI results for measurement and comparison, and

- new fine-grained analysis methods supporting the placement of EDMs/ ERMs.

#### 1.2.1 Fault Injection

For at least two decades, the primary testing and measurement technique in the field of SIHFT, which has to a certain degree also been used for analysis and comparison, has been Fault Injection (FI) [AAA<sup>+</sup>90, CP95, HTI97, ES98, BP03, ZAV04, Che10, KDN14]. Since the identification of primary and secondary physical causes for soft errors in the 1970s [BSH75, MW79], several techniques for the artificial injection of hardware faults have been devised. These techniques are used to mimic the effects of the original causes for hardware faults, but with extremely increased occurrence probability to trigger the fault-tolerance mechanisms often enough for sufficient evidence of their effectiveness.<sup>1</sup>

Nowadays, so-called *simulation-based* FI [BP03, KDN14] is one of the most favored FI techniques. The approach to inject faults into purely simulated hardware offers many advantages:

- The target system software does not need any modifications, which induce a "probe effect" in other FI approaches.

- Faults can be injected with high precision regarding space *where* to inject and time *when* to inject, and can reach any part of the hardware that is actually simulated.

- Experiments can be repeated deterministically, which is important for many optimization techniques.

- An FI *campaign*, consisting of a large number of individual FI experiments, can be sped up by running many simulator instances in parallel, for example making use of a computing cluster.

Despite these advantages, simulation-based FI also comprises a distinct set of drawbacks:

Chapter 3 discusses different FI techniques in detail, and describes existing tools implementing them.

<sup>1</sup> Note that, besides hardware faults, FI is also used to inject other types of faults, such as software bugs – or, "software faults" [Voa97, VGoo, MCVoo, DMo6, NCDM13], – which is outside the scope of this dissertation. Throughout this work, the term FI means the injection of *hardware* faults unless explicitly stated otherwise.

- Simulators are known to be very slow compared to the real hardware they simulate, especially in the case of detailed low-level simulations, resulting in long FI campaign runtimes.

- A simulator is only a sometimes very abstract approximation of the real hardware. Results obtained from simulations must be judged with the simulation accuracy in mind.

Before approaching the general problem of long campaign runtimes, I will first describe some basics in the context of simulation-based FI, and analyze shortcomings in the state of the art of simulation-based FI tools.

#### 1.2.2 Fault-Space Exploration and the Fault-Injection Tool Landscape

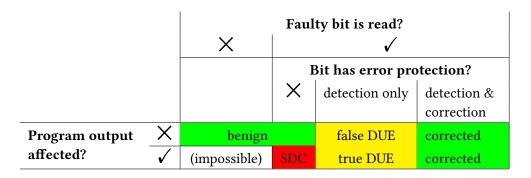

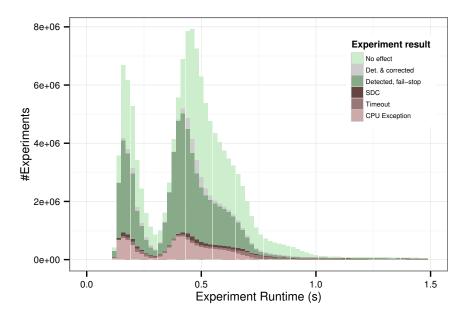

As mentioned above, an FI *campaign* consists of many individual FI experiments, each running the analyzed target software – often called the *workload* – in a similar way. In each experiment run, usually *one* fault is injected at a specific point in time after the workload start – measured, for example, in CPU cycles, – and at a specific location – for example, flipping one specific bit in main memory. After injecting the fault, the workload continues running, and the FI tool observes its behavior and its reaction to the injected fault. Depending on this observation, the FI tool categorizes the experiment result – or *outcome* – according to a predefined *failure model*, for example:

- NO EFFECT: The workload behaved the same way as in a run without FI, for example because the fault was masked by a subsequent operation.

- DETECTED: An EDM detected the fault, and initiated a recovery procedure, for example a reboot.

- SILENT DATA CORRUPTION (SDC): The workload's externalized state differed from the correct output, for example because the fault affected a calculation, and was not detected by an EDM.

- TIMEOUT: After injecting the fault, the workload did not finish within a predefined time limit, for example because it faultily entered an infinite loop.

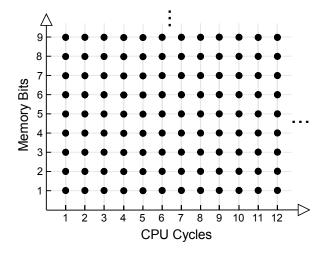

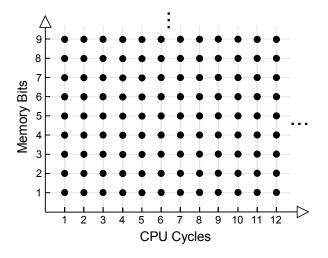

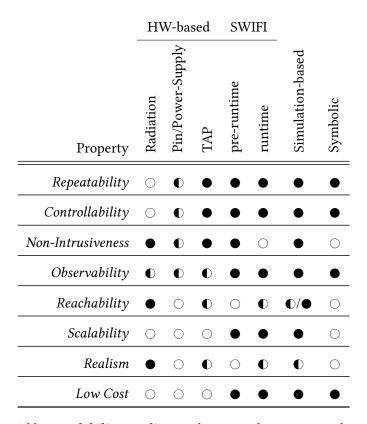

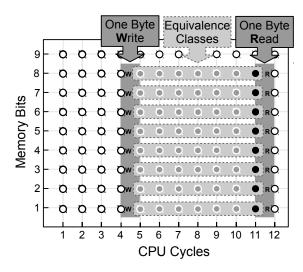

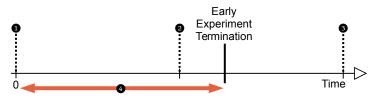

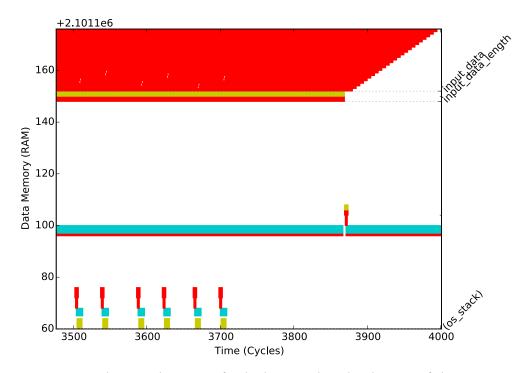

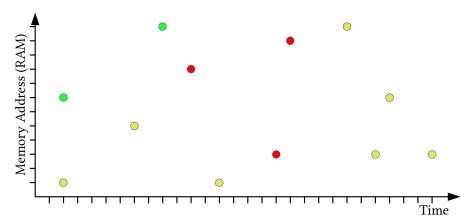

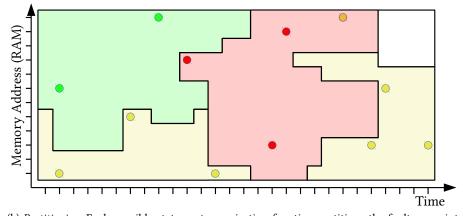

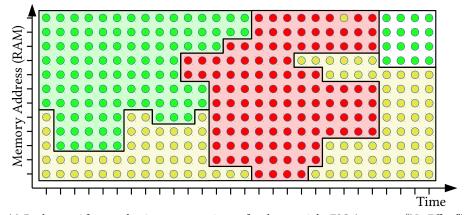

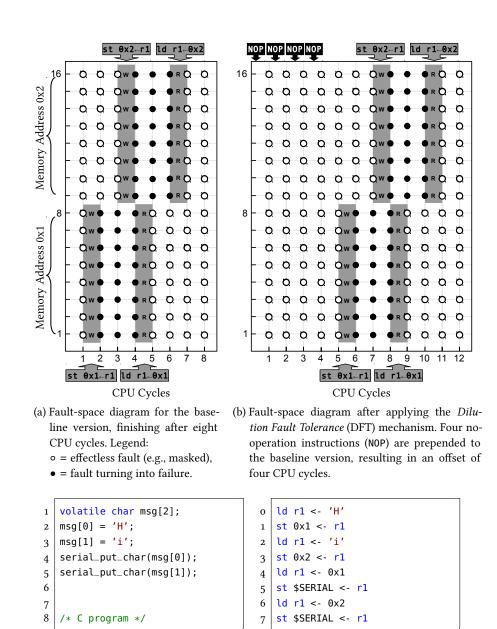

The difference between each experiment in an FI campaign is the point in time *when* a fault is injected, and the location *where* the fault is injected. These time and space coordinates span a so-called *fault space*, as depicted in Figure 1.1: Each coordinate, shown as a black dot, represents a possible individual FI experiment.

For detailed analyses, a *complete* fault-space exploration, yielding information on each and every possible fault-space coordinate, could be promising. Such detailed result data could be broken down to the level of single bits or individual program instructions to inform the developer about the criticality of single data objects, variables, modules, functions, source-code lines, or any other level of granularity deemed necessary for fault-tolerance related design decisions.

Figure 1.1: Single-bit flip fault space for a run-to-completion workload. Each dot represents a possible FI space/time coordinate. The workload proceeds until and stops at a specific point in time, the corresponding memory bit is flipped, and the workload resumes.

In spite of the potential, the state of the art in simulator-based FI tools only very recently started to provide complete fault-space exploration support in Relyzer [HANR12], or SmartInjector [LT13]. Nevertheless, these tools *do not introduce detailed analysis methods* that would make use of the detailed result data, but focus on methods how to obtain them. To my knowledge, all other FI tools in existence are only capable of randomly sampling the fault space, lacking the result detail for advanced analysis methods.

Separate from the drawbacks mentioned in the previous section, which are inherent to simulation-based FI in general, the existing FI tool landscape has several specific problems of its own:

- As explained above, all but the most recent [DBG<sup>+</sup>09, GDJ<sup>+</sup>11, HANR12, LT13] FI tools are incapable of complete fault-space exploration. There exists no FI tool that provides advanced analysis capabilities based on complete fault-space exploration down to the level of single data objects, variables, modules, functions, source-code lines, or any other level of granularity deemed necessary for fault-tolerance related design decisions.

- The vast majority of existing FI tools aims at *testing*, but lacks proper metrics for *measurement* and *comparison*. The latter is essential for driving design decisions in SIHFT.

- Most existing *simulators* do not have FI capabilities of their own. Researchers usually time-consumingly patch FI functionality into the code of an existing simulator [PTAB14], resulting in low code quality and maintainability issues. In some cases, they even write a completely new simulator with FI in mind [PSDC07, SPS09], spending resources on an engineering task that has already been solved by others, and

also resulting in scantly maintainable simulation code that is heavily intertwined with FI code [SHK<sup>+</sup>11].

- A side effect of this problem is that most simulation-based FI tools are limited to one specific simulator. This inflexibility becomes relevant when the requirements, for example regarding the CPU architecture, change during development.

- Most simulation-based tools cannot be used for FI techniques other than simulation-based FI. This forces a costly switch to a separate tool when in later development stages, FI experiments are supposed to be repeated on real prototype hardware, using, for example, *test-port based* FI<sup>2</sup>.

- Additionally, a practical observation is that most FI tools are not publicly available to other researchers for conducting own FI campaigns, or doing research on FI techniques. While Chapter 3 discusses possible reasons for this phenomenon, nevertheless its existence hinders own studies with and on FI.

The observation of these disadvantages in the tool landscape motivate the first contribution of this dissertation:

Contribution 1: Design and Implementation of Fail\*

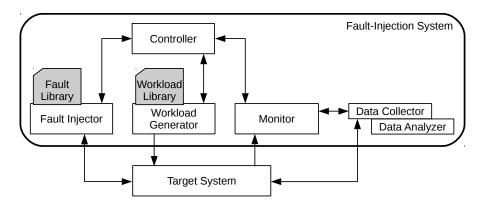

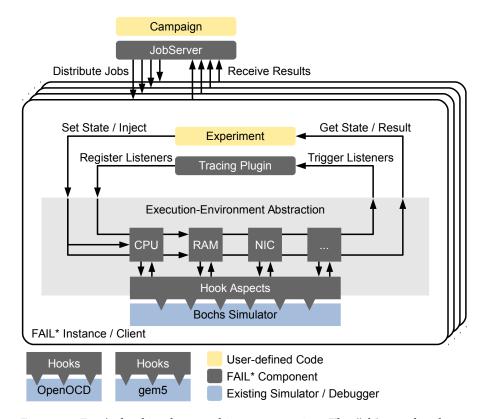

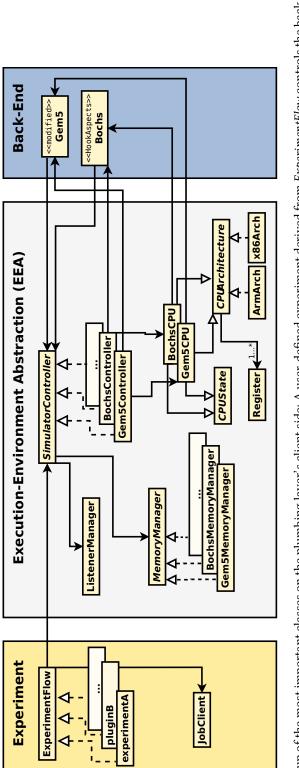

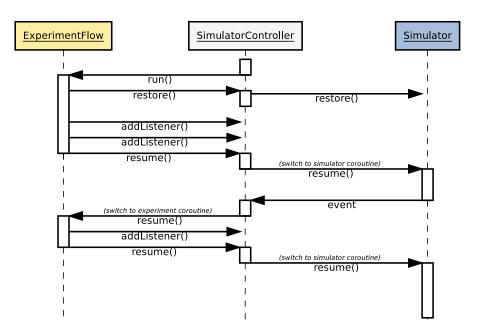

The first contribution of this dissertation is the *design and implementation of an FI tool*, named FAIL\*, that overcomes the aforementioned problems of existing tools in the field, and enables research on the general drawbacks of simulation-based FI.

- First and foremost, FAIL\* supports complete fault-space exploration, and analysis methods utilizing the detail level of the resulting data. These features will be covered by the following, separately described contributions 2, 3, and 5.

- FAIL\* explicitly supports measurement and comparison, and provides an appropriate metric for this purpose. This metric is separately described in contribution 4.

- By using minimally invasive software coupling techniques, FAIL\* attaches to existing simulator software without provoking serious maintainability issues.

- With the help of a carefully designed abstraction layer, FAIL\* can be – transparently to the experiment designer – used to inject faults in several target back ends (including both simulators and real prototype hardware) using two different FI techniques.

<sup>2</sup> In test-port based FI, faults are injected into prototype hardware via a test access port that is commonly available in embedded microcontrollers, such as JTAG [MT90, SZR03], BDM [How96, RSR99], or Nexus [II99, YdAL<sup>+</sup>03, FGAF06]. See Chapter 3 for more details on this FI technique.

#### 8 INTRODUCTION

• Additionally, FAIL\* is the basis for the other contributions of this dissertation, which were achieved by using and enhancing this tool.

Chapter 4 describes FAIL\*'s design and implementation in detail.

#### 1.2.3 Fault-Injection Campaign Runtimes

Another central problem of simulation-based FI is the amount of time and computing power that needs to be spent for FI campaigns, especially when aiming for complete fault-space exploration.

As explained in the previous section, for detailed analyses, information on each and every possible fault-space coordinate can be essential. In this case, the FI campaign exhaustively explores the fault space, running experiments for *every* coordinate. From Figure 1.1 it becomes clear that the fault-space size w – equaling the number of necessary experiments – grows quadratically with the amount of memory bits  $\Delta m$  it uses, and the workload's total runtime  $\Delta t$ : The size calculates as  $w = \Delta t \cdot \Delta m$ .

For a relatively small workload that runs for 1s or  $\Delta t = 10^9$  cycles on a 1 GHz CPU, and uses 1 MiB or  $\Delta m = 2^{23}$  bits of RAM, the fault-space has a size of  $w = 10^9 \cdot 2^{23} \approx 8.4 \cdot 10^{15}$ . If the experiment runtime  $T_{\text{experiment}}$  for one simulation run is known, we can calculate the campaign's total runtime  $T_{\text{campaign}} = w \cdot T_{\text{experiment}}$ . Even if a single FI experiment – involving the simulation of  $10^9$  CPU cycles – only takes  $T_{\text{experiment}} = 1$  s on the host CPU, the complete campaign would take  $T_{\text{campaign}} = 8.4 \cdot 10^{15} \cdot 1$  s, or about 266 million CPU years. Actually running this campaign is clearly infeasible even with large amounts of computing power at hand – a problem we call the *fault-space explosion* [HUD<sup>+</sup> 14b, HUD<sup>+</sup> 14a, SBS15].

Clearly,  $T_{campaign}$  must be reduced by many orders of magnitude to reach feasible CPU runtimes. As the FI experiments within a campaign can be conducted independently of each other, an obvious approach to cut down the *wall-clock time* from start to end of the campaign is to run multiple experiments in parallel on available computing hardware. Nevertheless, this solution is strongly limited by the number of available host CPUs, and therefore cannot reduce the runtime by more than a few orders of magnitude.

The remaining options of reducing  $T_{\text{campaign}} = w \cdot T_{\text{experiment}}$  are to either reduce the number of FI experiments N to an  $N \ll w$ , or to reduce the (average) runtime  $T_{\text{experiment}}$  for an individual experiment [GRSRVo6].

#### 1.2.4 Fault-Space Pruning

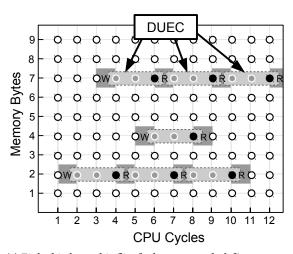

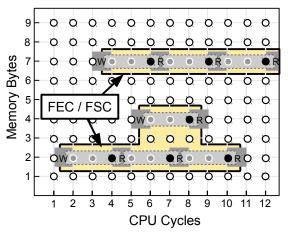

Section 3.3.1 explains the def/use-pruning technique – exploiting the equivalence of different fault-space coordinates – in detail. The first option, reducing the number of FI experiments, is a process called fault-list collapsing [BRIM98, BGC<sup>+</sup>o2], fault pruning [HANR12], or *fault-space pruning* [SBS14]. A very effective and widespread fault-space pruning technique based on additional information on memory accesses of the work-load is called *def/use pruning* [SJPB95, GS95]. It reduces the number of FI experiments by several orders of magnitude even without reducing precision.

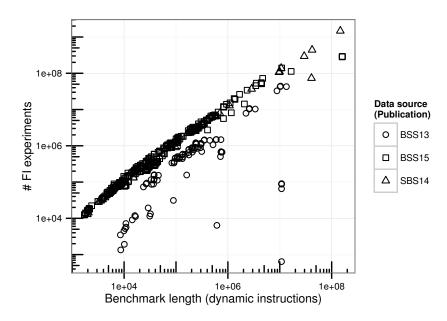

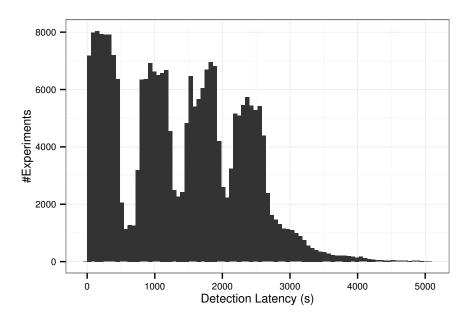

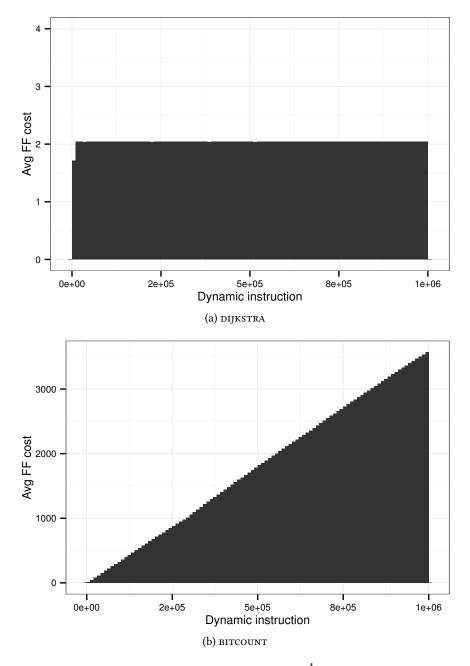

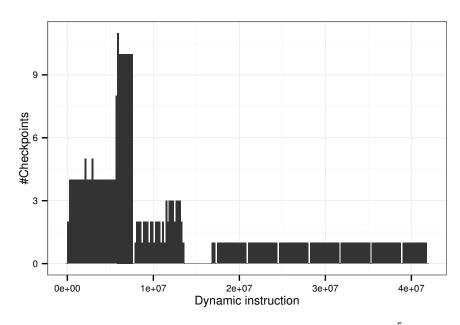

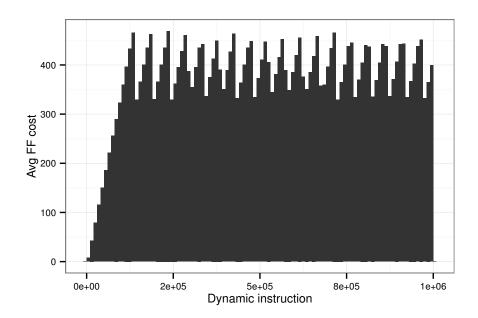

Figure 1.2: Workload lengths in dynamic instructions of benchmarks used in three different publications, and number of FI experiments after def/use faultspace pruning (log-log plot): The number of FI experiments necessary for an exhaustive fault-space exploration grows roughly linearly with the workload length – but is also influenced by the nature of the workload, explaining the outliers.

Using data from FI campaigns conducted for three of my publications [BSS13a, SBS14, BSS15], Figure 1.2 shows for each workload the length – in dynamic CPU instructions – and the number of FI experiments necessary for an exhaustive fault-space exploration *after def/use pruning*. The data shows that, for non-trivial workloads, the number of FI experiments is still large – with a maximum of about 1.5 billion experiments for one specific benchmark from [SBS14], – and grows about linearly with the number of dynamic instructions in the workload.

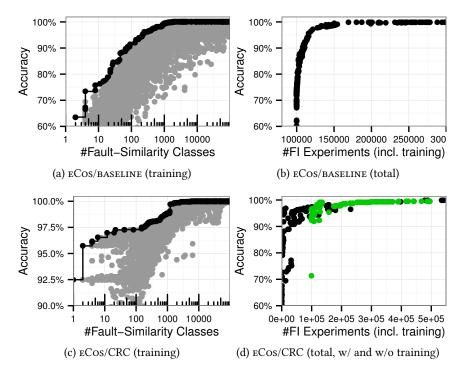

Contribution 2: A Heuristical Fault-Space Pruning Technique

The second contribution of this dissertation directly addresses the problem of exhaustive fault-space exploration and the accompanying large number of necessary FI experiments:

- I contribute *a novel, heuristical fault-space pruning technique* called Fault-Similarity Pruning.

- The heuristic allows to freely trade the FI-experiment count for result accuracy, and unlike prevalent sampling techniques provides information on *all* possible fault-space coordinates.

Chapter 5 describes the *Fault-Similarity Pruning* (FSP) heuristic and its implementation in FAIL\*, and evaluates it in detail.

#### 1.2.5 Reducing Experiment Runtime on Real Hardware

As explained in Section 1.2.3, the second option of reducing  $T_{\text{campaign}} = w \cdot T_{\text{experiment}}$  is to reduce the second multiplication factor, the average runtime  $T_{\text{experiment}}$  for an individual experiment. This can be achieved by either reducing the number of workload instructions *actually executed* on the target – be it a simulator, or another execution environment, – or by increasing the target's execution speed.

The literature describes solutions to the *first* problem, reducing the number of executed instructions in the experiment phase before [PRSRVoob, PRSRVooa, BGC<sup>+</sup>02, HVAN14, PTAB14] and after [BGC<sup>+</sup>02, LT13, HVAN14] the fault is injected. Approaching the *second* problem by increasing the execution speed *for hardware simulators* is *not* the focus of this dissertation: FAIL\* has been developed with loose coupling of exchangeable target back ends in order not to be distracted by reinventing or improving existing simulator technology.

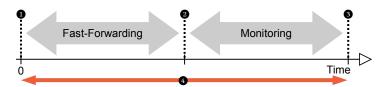

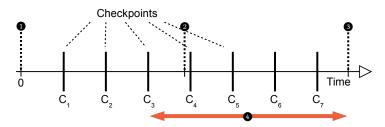

Contribution 3: Smart-Hopping – A Fast-Forwarding Technique for Fault-Injection Experiments on Real Hardware

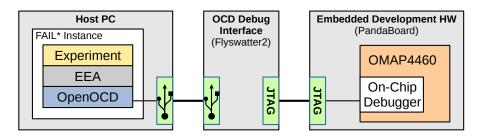

The third contribution of this dissertation addresses the runtime of individual FI experiments on real prototype hardware, controlled via a *Test-Access Port* (TAP):

- The *fast-forwarding operation* advancing a workload to the specific CPU cycle in its instruction stream when the fault is injected

is a major bottleneck in the runtime of an FI experiment running on TAP-controlled COTS prototype hardware.

- Consequently, I contribute a novel trace-based *fast-forwarding technique for TAP-based FI* termed Smart-Hopping. The technique increases the speed of the fast-forwarding operation *by several orders of magnitude* for most workloads.

Chapter 6 describes Smart-Hopping in detail, explains how it blends into the FAIL\* infrastructure, and evaluates it with a widely used benchmark suite.

#### 1.2.6 Measuring and Comparing Program Susceptibility to Soft Errors

The remaining two contributions of this dissertation address the state of the art on interpreting, analyzing, and presenting the *results* obtained from FI campaigns.

In the overwhelming majority of existing publications describing SIHFT solutions (for example, [Fuc96, RSRVT01, OSM02, NSV04, RCV<sup>+</sup>05b, CRA06, CCK<sup>+</sup>06, BSS12, HAN12]), program susceptibility to soft errors is measured and compared using the *fault-coverage factor* – or short: fault coverage – metric [BCS69]. This metric, "defined as the probability of system recovery given that a fault exists" [PMAC95], can be calculated with only a sample of

Section 3.1.2.5 discusses the fault-coverage factor metric more in detail.

Section 3.3.2 discusses related work on FI-experiment speedup. the fault space,<sup>3</sup> and reduces the FI results to percentages of each outcome defined in the failure model (see Section 1.2.2). For example, if F = 80 out of N = 1000 sampled FI experiments yield a result where the fault was neither detected nor masked – in the example of Section 1.2.2, either Silent Data Corruption (SDC) or timeout, – the fault coverage *c* can be calculated as

$$c = 1 - \frac{F}{N} = 1 - \frac{80}{1000} = 92\%$$

Contribution 4: A Comparison Metric for Soft-Error Susceptibility of Programs

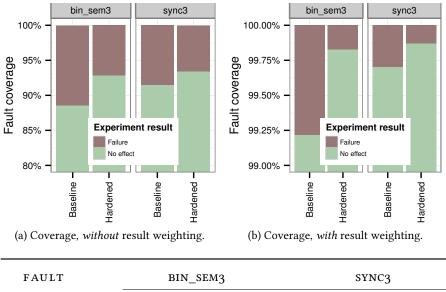

The fourth contribution of this dissertation addresses this and several other problematic measurement practices in the field of SIHFT:

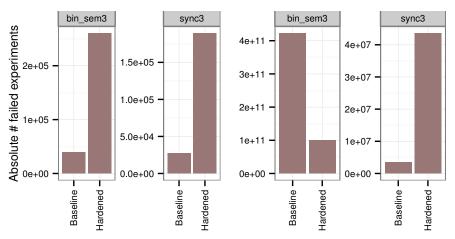

- After uncovering another two ill-advised practices in the interpretation of FI results, I demonstrate that *the fault-coverage factor metric is unsound* for the comparison of soft-error susceptibility of programs, and can lead to wrong design decisions.

- These findings are substantiated by an illustrative thought experiment and results from an FI campaign conducted with FAIL\*.

- Based on these insights, *I construct an objective metric usable for comparison* using extrapolated absolute failure counts, and introduce the mathematical foundation supporting this proposition.

Chapter 7 analyzes common measurement and comparison practices in the field in detail, reveals the unsoundness of the fault-coverage metric for a widely-used purpose, and provides the mathematical foundation for the new comparison metric.

#### 1.2.7 Fine-Grained Post-Injection Analysis and Result Visualization

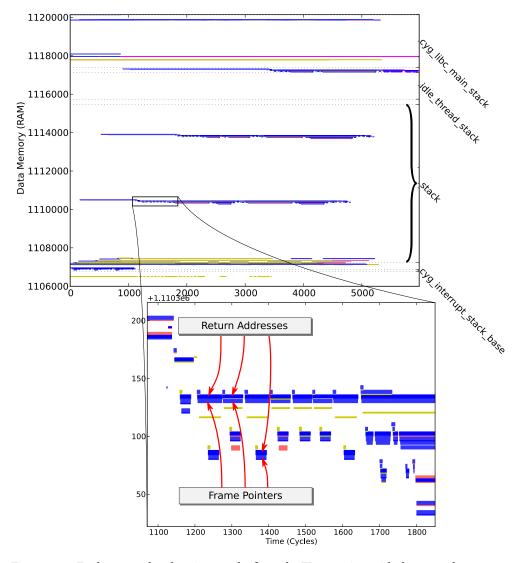

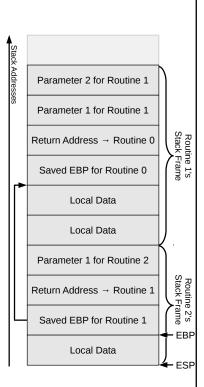

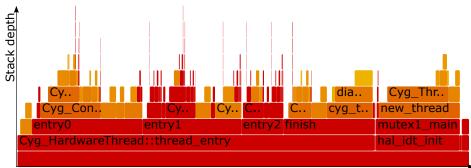

With a metric at hand to measure and compare the *global* susceptibility of programs to soft errors, the fifth and final contribution of this dissertation addresses fine-grained analysis and result visualization on the *local* level. As explained in Section 1.2.2, the state of the art in FI tools presents a prominent gap by lacking advanced analysis capabilities based on complete fault-space exploration. This dissertation takes first steps to gauge this dormant potential.

Several researchers already addressed the problem of locating particularly vulnerable – or *critical* – spots of the program [HJS01, HJS02a, BDCDN<sup>+</sup>03, HJS04, PKI05, PKI07, PNKI08, SK08b, SK09b, SSSF10b, PSC<sup>+</sup>11, PKI11, LJ11, HAN12, PNKI13]. These critical spots are either logical candidates for the placement of EDMs/ERMs, or drive other dependability-related design decisions – like choosing a different algorithm for a particular functional requirement. Most of these existing works are specific to certain classes of EDMs/

Section 3.4 discusses fine-grained criticality-analysis methods in detail.

<sup>3</sup> Of course, results from exploring the complete fault space can also be used, but are unnecessarily costly if only the fault coverage is calculated.

ERMs, or limited to one specific, sometimes very coarse level of granularity – which already strongly predetermines and limits the analysis results, and, consequently, possible placements. Almost all use the aforementioned, problematic fault-coverage factor metric for either measuring criticality, or for the evaluation of their approach after the placement of EDMs/ERMs in the spots deemed most critical.

**CONTRIBUTION 5: FAULT-INJECTION RESULT ANALYSIS**

Hence, the fifth and last contribution of this dissertation introduces *analysis methods at different levels of granularity, operating on the results from complete fault-space exploration.*

- By collecting data on the whole fault space, the decision on the analysis granularity in space and time can be postponed until after the FI campaign.

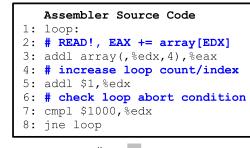

- The detail level of the result data allows to run analyses aiding design decisions on the level of variables, program phases, modules, functions, source-code lines, or single instructions, and opens up potential for more analysis types in the future.

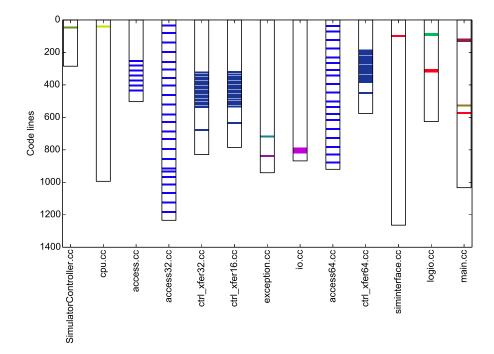

The FAIL\* case studies in Chapter 4 take first steps at gauging the dormant potential of analyses of FI results from complete fault-space exploration, and present different analysis methods.

#### 1.3 OUTLINE

This section gives an outline of this dissertation, and assigns the five contributions from Section 1.2 to chapters.

- Chapter 2 provides more background by shedding light on the causes and effects of hardware faults, and defines basic terms and metrics. The chapter also describes possible countermeasures on both the hardware and software levels, with a focus on the basic principles of *software*-implemented hardware fault tolerance (SIHFT) and *soft errors*.

- Chapter 3 surveys the state of the art in hardware FI: First, the chapter discusses the possible goals of injecting hardware faults and which of these this dissertation focuses on, and how faults from the real world are mapped to artificial injection using *fault models*. Subsequently, further basic terms and definitions in the context of FI are introduced, and an overview on the FI tool landscape is provided. After drawing conclusions on the capabilities and properties of existing tools, I describe optimization techniques from the literature that help reducing the efforts spent in FI campaigns. The chapter ends with a discussion of metrics used in the domain of FI, and principal limitations inherent to FI.

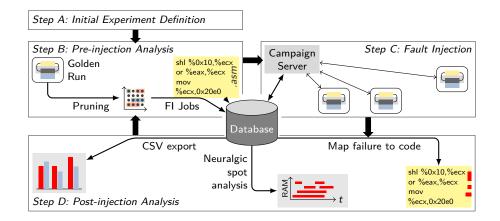

- Chapter 4 describes the first contribution of this dissertation: The design and implementation of the FAIL\* FI tool. Addressing major shortcomings in the tool landscape identified in the previous section and Chapter 3, FAIL\* supports complete fault-space exploration, susceptibility analyses on several levels of granularity, and the comparison of different programs. I describe the design decisions making these properties possible, and provide details on FAIL\*'s implementation and extension points. Additionally, Chapter 4 presents case studies with FAIL\*, highlighting analysis methods at different levels of granularity that operate on the results from complete fault-space exploration.

- Chapter 5 addresses the second contribution: A heuristical fault-space pruning technique reducing the computing efforts for complete fault-space exploration by freely trading the number of FI results for result accuracy. After explaining the basic idea of *fault similarity*, I give details of the pruning technique's implementation as an extension to FAIL\*, and evaluate the approach on a set of benchmarks.

- Chapter 6 provides a complementary approach to reduce FI campaign runtimes by describing the third contribution: A technique I call *Smart-Hopping* that increases the speed of the fast-forwarding operation, which is essential for systematic, fault-space exploring FI experiments on real prototype hardware. After discussing conventional approaches for fast-forwarding on real hardware, the chapter describes the Smart-Hopping technique and its implementation in FAIL\*. Its evaluation with a similar set of benchmarks shows an improvement of up to several orders of magnitude compared to the state of the art.

- Chapter 7 describes the fourth contribution: A metric for the *comparison* of the soft-error susceptibility of programs. After analyzing illadvised practices in the field of SIHFT and uncovering the unfitness of metrics (introduced in Chapter 3) widely used to compare the fault susceptibility of different programs, I construct a new metric usable for this purpose, and provide the mathematical foundation supporting this proposition.

Chapter 8 concludes the dissertation, summarizing key results and current limitations, and suggests opportunities for future research.

#### 1.4 AUTHOR'S CONTRIBUTION TO THIS DISSERTATION

According to §10(2) of the "Promotionsordung der Fakultät für Informatik der Technischen Universität Dortmund vom 29. August 2011", a doctoral dissertation has to contain a separate list that highlights the author's contributions to research results obtained in cooperation with other researchers. Therefore, the following overview lists the contribution of the author on the presented results for each chapter:

- Chapter 3 provides an overview on FI techniques, tools, and gaps in the state of the art. The FI-tools and techniques summaries are partially adapted from publications at PRDC 2011 [SHK<sup>+</sup>11], ARCS 2012 [SHK<sup>+</sup>12], ETS 2014 [SRS14], SAFECOMP 2014 [SBS14], DSN 2015 [SBS15], and EDCC 2015 [SHD<sup>+</sup>15]. The discussion on FI-tool generalists and specialists was already published at PRDC 2011 [SHK<sup>+</sup>11] and ARCS 2012 [SHK<sup>+</sup>12]. FI optimizations were already discussed at ETS 2014 [SRS14], SAFECOMP 2014 [SBS14], DSN 2015 [SBS15], and EDCC 2015 [SHD<sup>+</sup>15]. In each of these publications, I was the principal author, and contributed the related-work discussions adapted in Chapter 3.

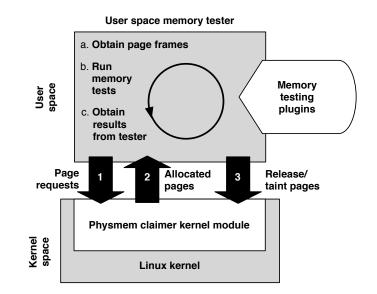

- Chapter 4 describes the design and implementation of the FAIL\* FI tool, and demonstrates its capabilities in four case studies. Details on FAIL\* were already published at ARCS 2012 [SHK<sup>+</sup>12] and EDCC 2015 [SHD<sup>+</sup>15], where I was the principal author and provided the majority of FAIL\*'s concepts, design, and implementation. The RAMpage case study was published at PRDC 2011 [SNK<sup>+</sup>11] and in IJCCBS [SKSE13], where I was the principal author, conducted all FI-related evaluation steps, and coordinated RAMpage's implementation reworking and efficiency evaluation by Ingo Korb. RAMpage's initial prototype implementation was a result of Jens Neuhalfen's diploma thesis [Neu10]. The Generic Object Protection (GOP) case study was published at DSN 2013 [BSS13a] and in IEEE TDSC [BSS15], which I co-authored. I contributed the FI setup with FAIL\*, and the FI-related evaluation results and simulator-runtime measurements. The Return-Address Protection (RAP) was published at SOBRES 2013 [BSS13b], which I co-authored. Again, I contributed the FI setup with FAIL\*, and the FI-related evaluation results and simulator-runtime measurements.

- Chapter 5 describes the *Fault-Similarity Pruning* (FSP) approach for FI-experiment count reduction. The approach was published at SAFE-COMP 2014 [SBS14]. I was the principal author and contributed concepts, design, implementation, and evaluation of the approach.

- Chapter 6 describes the *smart-hopping* approach for fast-forwarding FI workloads in a high-latency execution environment. The approach was published at ETS 2014 [SRS14]. I was the principal author and contributed the concepts behind the *smart-hopping* approach and its checkpointing extension, the related-work dissection including the identification of the *simple-hopping* approach we used as the comparison baseline, details of the smart-hopping algorithm, and the evaluation setup. The implementation was contributed by Lars Rademacher in his master's thesis [Rad13].

- Chapter 7 dissects current practices in simulation-based FI, identifies common pitfalls regarding result interpretation, and constructs a result metric that can be used to compare hardened programs. The re-

sults were published at DSN 2015 [SBS15], where I was the principal author. I contributed the study design, the related-work dissection and resulting pitfall identification, the thought experiment, and the derivation and formalization of the *absolute failure count* metric. The identification of the underlying issues with the *fault-coverage factor* metric, and the foundations for the presented, new comparison metric were developed in cooperation with Christoph Borchert.

# HARDWARE FAULTS AND FAULT-TOLERANT COMPUTING

"The cheapest, fastest, and most reliable components are those that aren't there."

Gordon Bell

#### Contents

| 2.1 | Moore   | e's Law and the Evolution of Semiconductor Technology  | 18 |

|-----|---------|--------------------------------------------------------|----|

| 2.2 | Depen   | adable Systems: Attributes, Threats, and Means 19      |    |

|     | 2.2.1   | Dependable Systems 19                                  |    |

|     | 2.2.2   | Dependability Threats: Faults, Errors, and Failures 20 | D  |

|     | 2.2.3   | Means to Achieve Dependability 21                      |    |

|     | 2.2.4   | Dependability Metrics 22                               |    |

|     | 2.2.5   | Summary 24                                             |    |

| 2.3 | Hardw   | vare Faults at the Transistor Level <b>24</b>          |    |

|     | 2.3.1   | MOSFETs and CMOS Circuitry 25                          |    |

|     | 2.3.2   | Radiation-Induced Transient Faults 26                  |    |

|     | 2.3.3   | Permanent Faults 32                                    |    |

|     | 2.3.4   | Summary 33                                             |    |

| 2.4 | Fault-7 | Tolerant Computing 34                                  |    |

|     | 2.4.1   | Redundancy 34                                          |    |

|     | 2.4.2   | Hardware-Implemented 36                                |    |

|     | 2.4.3   | Software-Implemented 38                                |    |

| 2.5 | Summ    | ary <b>45</b>                                          |    |

|     | 2.5.1   | Fault Tolerance 45                                     |    |

|     | 2.5.2   | Reliability Analysis, Measurement, and Test 46         |    |

|     |         |                                                        |    |

This CHAPTER PROVIDES MORE BACKGROUND on the context of this dissertation by shedding light on the causes and effects of hardware faults. It subsequently defines basic terms and metrics in the context of fault tolerance, and describes possible countermeasures to hardware faults on both the hardware and software levels.

Throughout this chapter, I will focus on transient faults, also known as *soft errors*, as they are the primary focus of this work, and only scratch the surface on other fault types and their effects. Similarly, the basic principles of *software*-implemented hardware fault tolerance (SIHFT) will be described more thoroughly than their hardware-implemented pendants.

This chapter is partially based on knowledge from Shubu Mukherjee's book *Architecture Design for Soft Errors* [Muko8] and Olga Goloubeva et

al.'s *Software Implemented Hardware Fault Tolerance* [GRSRVo6], and complements the information with newer developments in many places where appropriate.

#### 2.1 MOORE'S LAW AND THE EVOLUTION OF SEMICONDUCTOR TECH-NOLOGY

As the introduction already outlined, the continuing exponential growth in the number of transistors per semiconductor chip – popularly known as Moore's Law [Sch97] – is accompanied by limits in chip-area sizes and power consumption. The industry's primary approach to accommodate these constraints is a permanent, iterative improvement process pushing lithography – the fabrication technology used to "print" circuits onto silicon wafers – to higher structure densities. Moore's law, of course, is no "law" in the original meaning. It was an *observation* of a trend to continuously add more transistors to integrated circuits, and a – nevertheless quite accurate – estimation of the pace of this process. Among the real intentions behind structure scaling are lower per-transistor and chip prizes [Sch97], higher switching speeds, and reduced power consumption.

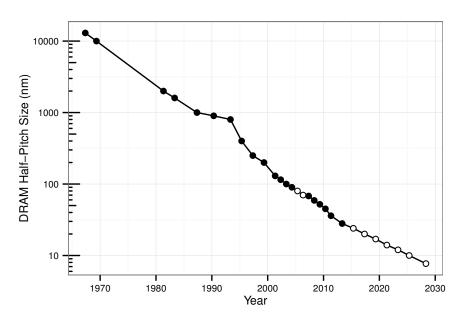

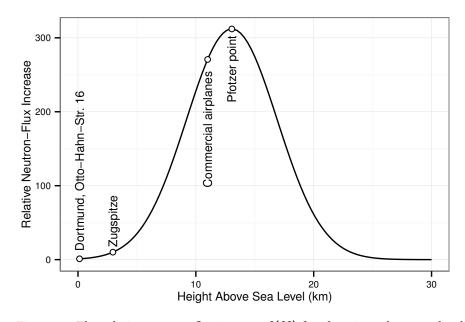

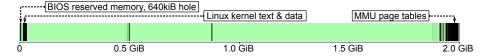

Figure 2.1 shows the evolution of a specific semiconductor structure-size metric – the so-called Dynamic Random-Access Memory (DRAM) *half-pitch size*, representing half the distance between identical features in DRAM memory cells – over the last 45 years. The plot gives an impression of the steadiness of this exponential evolution, in spite of ever-repeating announcements of Moore's law coming to an end due to emerging obstacles that were assumed indomitable [Sch97].

Two examples for obstacles thought to bring Moore's prediction to an end are the "memory wall" and "power wall" problems [BJS07, Muko8]: The former was the observation that off-chip DRAM memories continuously slowed down compared to microprocessors over the years, the latter that the extreme rise in the power dissipation led to growing overheating problems. These obstacles were countered by architectural solutions, such as prefetching and multi-threading, advanced process technologies, and powermanagement solutions like reduced supply voltages or clock frequencies [Muko8, Mit14].

The literature expects – and already observes – that the "soft-error wall" [Muko8] or "reliability wall" [BJSo7] is the next challenge in the line of obstacles on the way following Moore's law: The structure-size shrinking causes a rise in hardware-fault rates affecting the functionality of semiconductor devices. The "power wall" even exacerbates this problem: On the one hand, lower supply voltages increase the susceptibility to radiation-induced faults. On the other hand, fault-tolerance mechanisms such as *Triple-Modular Redundancy* (TMR) of critical hardware structures (see Section 2.4.2.3) consume additional power, and may be impossible to implement within given power and performance constraints [CMR15].

Figure 2.1: The chip industry's history and projection of the development of a central structure-size metric: The DRAM half-pitch size (log scale), representing half the distance between identical features in DRAM memory cells. [Kuro5, Into8, Int10, Int11, Int13]

#### 2.2 DEPENDABLE SYSTEMS: ATTRIBUTES, THREATS, AND MEANS

Before describing the cause and effects of hardware faults more in detail, I will first introduce basic terms and definitions from the fault-tolerance domain, used in the literature and throughout this dissertation. Some of these terms were already introduced and used intuitively in Chapter 1, but are defined more precisely here.

#### 2.2.1 Dependable Systems

As defined by Avižienis et al., "a system is an entity that interacts with other entities, i.e., other systems, including hardware, software, humans, and the physical world with its natural phenomena" [ALRLo4] – its environment. A system has a specified functionality, exhibits behavior to fulfill that functional specification, has a state at any point in time, and may (recursively) be composed of subsystems or components. The service a system delivers "is its behavior as perceived by its user [... which is] another system that receives service" [ALRLo4] from the provider at its interface.

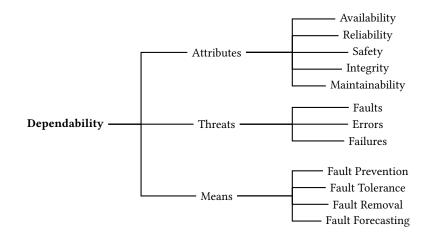

Dependability integrates several attributes for dependable systems [ALRLo4]:

- AVAILABILITY is generally defined by the system's *"readiness for correct service"* [ALRLo4]. The system is not ready during scheduled or unplanned downtimes.

- RELIABILITY is the "continuity of correct service" [ALRLo4]. This means that that the system correctly answers to requests within the specified response time it does not fail. [ALRo4]

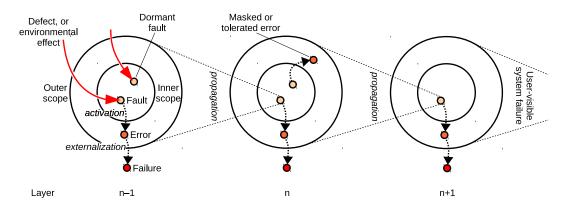

Figure 2.2: The chain of dependability threats [ALRo1, ALRLo4]: A *fault* may be *activated*, and turns into an *error*. An error can be externalized and turns into a *failure*, which propagates upwards as a fault on the next layer. *Figure based on* [*Ulb14*, *Muko8*, *Döb14*].

- SAFETY describes the "absence of catastrophic consequences" [ALRLo4] on both users and environment. This means that a passive ("fail-stop") behavior can still be "safe",<sup>1</sup> even if the system does not do anything useful anymore [Ech90, Muk08] – it may fail, but not in a particularly catastrophic way. [ALR04]

- INTEGRITY is defined by the "absence of improper system [state] alterations" [ALRLo4].

- MAINTAINABILITY is the system's "ability to undergo modifications and repairs" [ALRL04].

This dissertation focuses on the dependability attribute *reliability* and its assessment. Nevertheless, reliability directly affects both *availability* and *safety*, and depends on the system's *integrity*. Maintainability is generally outside the scope of this dissertation, although I will discuss the *maintainability of FI tools* in Chapter 3 and 4.

#### 2.2.2 Dependability Threats: Faults, Errors, and Failures

A complex hardware/software system can be understood as a stack of abstraction layers, each only observing the external state of the layer directly below. In this setting, the terms *fault, error*, and *failure* – dependability *impairments* [Lap85, LAK92] or *threats* [ALR04, ALRL04] – can be explained and put into context.

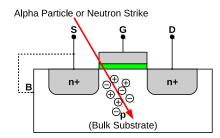

Figure 2.2 shows how a defect or an interaction with the external environment – such as the impact of energetic particles – can cause a *fault* in a

<sup>1</sup> In his classic 1985 paper, Gray calls this "not doing the wrong thing" [Gra85] behavior Reliability instead of Safety [ALR04], and "doing the right thing within the specified response time" [Gra85] Availability instead of Reliability [ALR04]. Since then, the community has put considerable efforts into agreeing upon a common taxonomy and clear definitions of the terms used [Lap85, LAK92, ALR01, ALR04, ALR04].

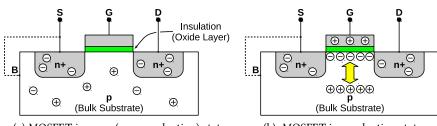

hardware structure or software module. An example on the circuit level is an energetic particle hitting a transistor. A fault does not necessarily mean that the device – as seen on abstraction layer n – has an (internal) error yet: Unless the fault gets *activated*, it stays *dormant* or *passive*. [LAK92, ALR01, ALRL04, GRSRV06]

A fault is activated and becomes an *error* if it affects the layer's internal state, residing in its *inner scope* (Figure 2.2). If, in the example, the transistor is hit "strong enough", it may change its switching behavior.

If the layer's internal state is modified due to an error, it may not be able to provide its service to a layer above correctly – the error escalates to the *outer scope*. This externally visible deviation from the expected service is called a *failure*.<sup>2</sup> In the example, the transistor may be part of a DRAM circuit: The state it helped holding could be inverted – a *bit flip* occurs, constituting a *failure* on that layer.

Instead of turning into a failure, errors can also be *masked* – for example, overwritten before they are read – or *tolerated* – for example, due to a redundancy mechanism bringing the flipped bit back to its correct state before escalation.

Once a service failure on layer n occurred, the failure can *propagate* to the layer n + 1 above. From the perspective of layer n + 1, the layer n failure is a *fault*, possibly again being activated and turning into an error on layer n + 1. Hence, the "notion of an error [...] is fundamentally tied to the notion of a scope" [Muko8]. A *fault-tolerance mechanism* (see Section 2.4) on layer n can prevent a fault from propagating to layer n + 1 by preventing the corresponding error to turn into a failure on layer n.

Faults can further be categorized by their *lifetime. Transient faults* – also known as *soft faults* – appear and disappear again. *Intermittent faults* first behave similarly, but then reappear: They are considered *"early indicators of impending permanent faults"* [Muko8]. These faults, as their name already indicates, remain for an indefinite period of time, and can often only be corrected by replacing – or repairing – the affected component.

#### 2.2.3 Means to Achieve Dependability

The literature categorizes *means* to actually achieve the different dependability attributes from Section 2.2.1 into four categories [ALRLo4]:

FAULT PREVENTION (or FAULT AVOIDANCE) aims at *preventing* the occurrence of faults. This can, for example, be achieved by improving Section 2.3 describes hardware faults at the transistor level in detail.

Section 2.4 gives an overview on fault-tolerance mechanisms explicitly preventing errors from becoming failures.

<sup>2</sup> Parts of the literature [Lap85, LAK92, Muk08] only call service deviations visible to the user a failure, and use the term error for all other layers. As this can lead to confusion when and how exactly an error is externalized to the upper abstraction layers, I use the term failure for the externalization of errors on any of the system's layers or subsystems (following a majority of other works, e.g., [ALR01, ALRL04, ALR04, Döb14, Ulb14]). Prasad et al. [PMW96] discuss similar dependability terminology disagreements in the community. Note, though, that the literature often uses the term soft error for a failure on the hardware layer, meaning a transient fault from the perspective of a software layer.

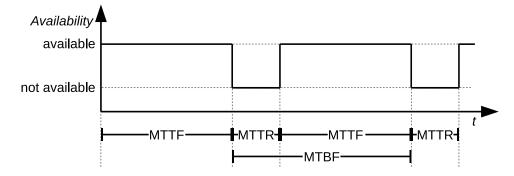

Figure 2.3: The relationship between MTTF, MTTR, and MTBF. *Figure based on* [Mar11].

chip manufacturing processes towards using packaging materials emitting less alpha radiation [Cono3].

- FAULT TOLERANCE is a means to "avoid service failures in the presence of faults" [ALRLo4]. Example techniques can be found on both the hardware and software level – for example, ECC memory respectively duplication of important variables, – and include introducing some sort of redundancy into the system (see Section 2.4).

- FAULT REMOVAL reduces the number and severity of faults. Fault removal can be applied at development time, for example by localizing insufficiently fault-tolerant parts of the system, and hardening them. At runtime, fault removal is achieved by conducting maintenance work, such as replacing physically damaged parts, or applying patches [ALRLo4].

- FAULT FORECASTING estimates the present number, the future incidence, and the expected consequences of faults. This kind of (either qualitative or quantitative) system evaluation can, for example, involve FI experiments.

In this dissertation, I focus on *fault forecasting* – the assessment and quantification of the *reliability* attribute (Section 2.2.1) – and techniques to provide information aiding *fault removal* by directed application of *fault tolerance* mechanisms.

#### 2.2.4 Dependability Metrics

The literature defines several metrics to capture and quantify particular dependability attributes. One of the most basic metrics is *Time To Failure* (TTF), expressing fault or error rates. If in a specific device an error occurs after nyears, this is its TTF. A more practical metric is derived when the TTFs of multiple devices – or multiple errors in the same device – are measured and averaged, yielding the *Mean Time To Failure* (MTTF). [Muko8]

Directly related to MTTF are *Mean Time To Repair* (MTTR) and *Mean Time Between Failures* (MTBF), as illustrated in Figure 2.3. MTTR measures the

mean time to repair the device after the error was detected. MTBF accounts for the mean total time between one error and the next error, including the repair time: MTBF = MTTF + MTTR.

A metric related to MTTF is *Failure In Time* (FIT) [JED01], where 1 FIT *"represents an error in a billion*  $(10^9)$  *hours"* [Muko8]. A device's error rate is often referred to as its *FIT rate*. An advantage over MTTF is the fact that FIT rates are additive when composing a device from multiple components under specific assumptions<sup>3</sup> [Muko8, Mar11]:

$$\text{FIT}_{\text{device}} = \sum_{i=0}^{n} \text{FIT}_{\text{component } i}$$

FIT rate and MTTF<sup>4</sup> are reciprocally related [KK07, Muk08, Sor09, Mar11] (again, under the aforementioned assumptions):

$$MTTF = \frac{10^9 h}{FIT rate}$$

The dependability attribute *availability* (see Section 2.2.1) is directly associated with a metric quantifying it as *"the probability that a system is functioning correctly at a particular instant of time*" [Muko8]. It can be calculated as a fraction of the device's uptime and its total lifetime, or by using MTTF and MTBF:

Availability =

$$\frac{\text{system uptime}}{\text{system uptime} + \text{system downtime}} =$$

=  $\frac{\text{MTTF}}{\text{MTTF} + \text{MTTR}} = \frac{\text{MTTF}}{\text{MTBF}}$

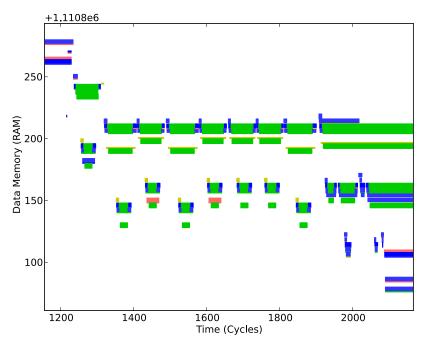

In this context, the term "five nines" – or any other number of "nines" – is often used to refer to an availability of 0.99999, or 99.999 percent.