# Optimized Commutation Circuit for Improved Utilization of SiC

A thesis approved for the academic degree of

Doktor der Ingenieurwissenschaften (Dr.-Ing.)

at the

Faculty of Electrical Engineering and Information Technology

TU Dortmund University

by

M.Sc. Michael Schlüter born on 08.07.1986 in Büren

Supervisor: Univ.-Prof. Dr.-Ing. Martin Pfost, TU Dortmund University Co-Advisor: Univ.-Prof. Dr.-Ing. Andreas Lindemann, Otto-von-Guericke-Universität

Day of Oral Examination: 08.12.2023

# Contents

| 1 | Intr | oduction                                                  | 1  |

|---|------|-----------------------------------------------------------|----|

|   | 1.1  | Thematic Classification                                   | 2  |

|   | 1.2  | Problem Description                                       | 2  |

|   | 1.3  | Hypothesis and Research Questions                         | 5  |

|   | 1.4  | Structure of the Thesis                                   | 5  |

| 2 | Bas  | ics and Technology Review                                 | 7  |

|   | 2.1  | Power Semiconductor Devices                               | 7  |

|   |      | 2.1.1 A Short Introduction to Semiconductor Materials     | 7  |

|   |      | 2.1.2 Introduction to Diodes                              | 8  |

|   |      | 2.1.3 Introduction to MOSFETs                             | 10 |

|   | 2.2  | Parasitic Inductances in Power Electronics                | 13 |

|   |      | 2.2.1 Basic Geometries and Their Characteristics          | 13 |

|   |      | 2.2.2 Consequences for Low- and High-Power Applications   | 14 |

|   | 2.3  | Hard and Soft Switching                                   | 15 |

|   |      | 2.3.1 Description of the Turn-On Event                    | 17 |

|   |      | 2.3.2 Description of the Turn-Off Event                   | 18 |

|   |      | 2.3.3 Resonant Switching                                  | 19 |

|   | 2.4  | Introduction to Snubbers                                  | 22 |

|   |      | 2.4.1 DC-Snubber $\ldots$                                 | 22 |

|   |      | 2.4.2 Turn-Off Snubber                                    | 25 |

|   |      | 2.4.3 Power Loss Estimation                               | 25 |

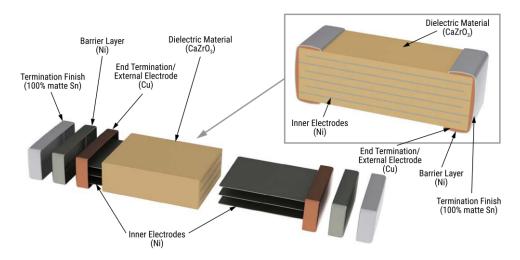

|   | 2.5  | Ceramic Capacitors                                        | 26 |

|   |      | 2.5.1 Mechanical Construction                             | 27 |

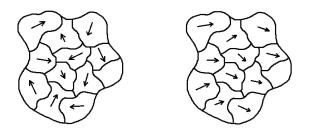

|   |      | 2.5.2 Dielectric Materials                                | 27 |

|   |      | 2.5.3 Electrical Characteristics                          | 29 |

| 3 | Intr | oduction and Modeling of an Optimized Commutation Circuit | 31 |

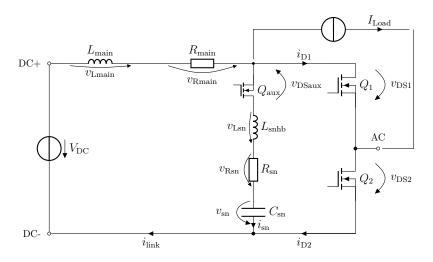

|   | 3.1  | 1                                                         | 32 |

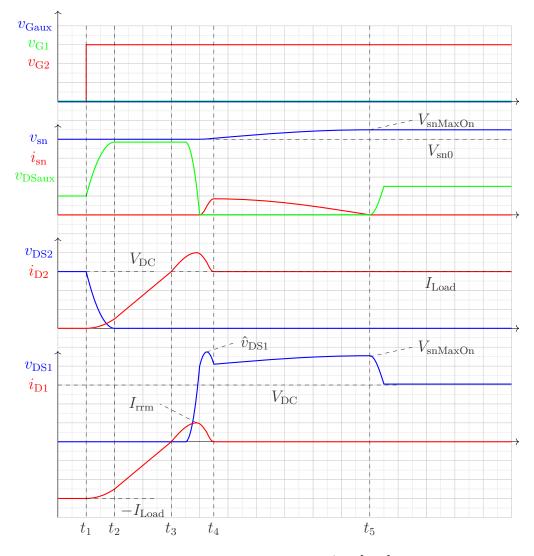

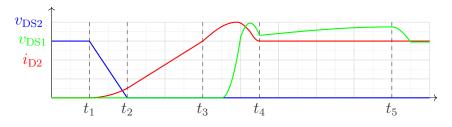

|   | 3.2  | Operation at Turn-On and Diode Recovery                   | 33 |

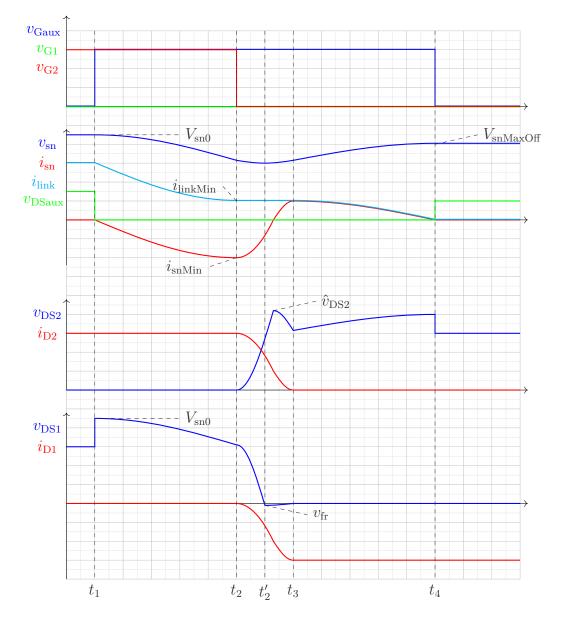

|   | 3.3  | Operation at Turn-Off                                     | 36 |

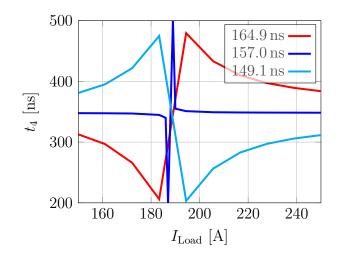

|   | 3.4  | Modeling the Turn-On Event                                | 39 |

|   | 3.5  | Modeling the Turn-Off Event                               | 43 |

| 4 | Мо   | del Validation and Application                            | 48 |

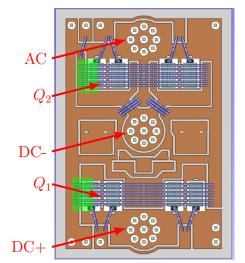

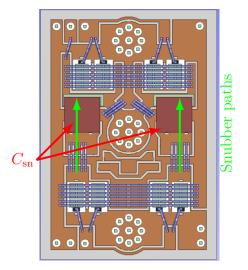

|   | 4.1  | Module Assembly and Measurement Description               | 48 |

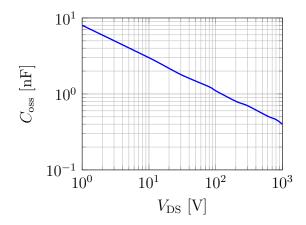

|   |      | 4.1.1 Capacitor Selection                                 | 48 |

|   |      | 4.1.2 Conventional Halfbridge                             | 50 |

|   |      | 4.1.3 Halfbridge with DC-Snubber                          | 50 |

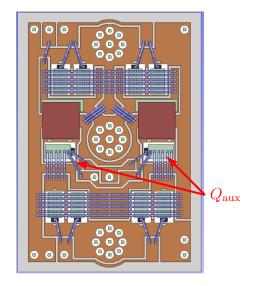

|   |      | 4.1.4 Halfbridge with Active Snubber                      | 52 |

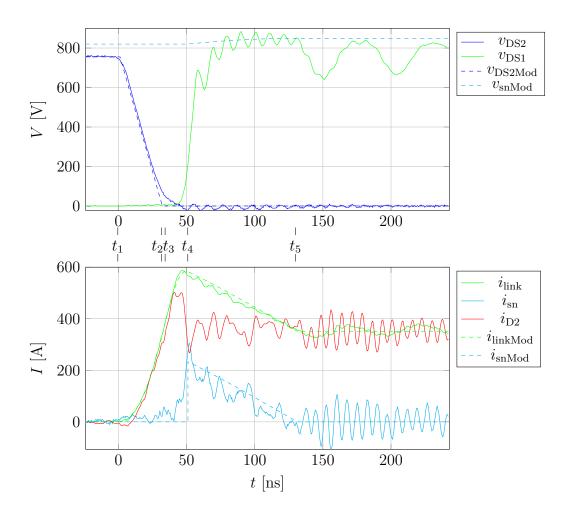

|   | 4.2  | Turn-On Model Validation for High Operation Currents      | 53 |

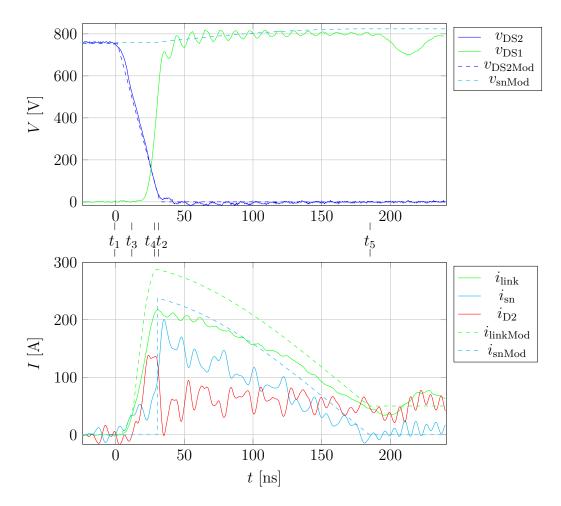

|   | 4.3  | Turn-On Model Validation for Low Operation Currents       | 58 |

|   | 4.4  | Turn-Off Model Validation for High Operation Currents     | 62 |

|   | 4.5               | Turn-Off Model Validation for Low Operation Currents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 68                                            |

|---|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|   | 4.6               | Continuous Operation at High Load Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 74                                            |

|   | 4.7               | Continuous Operation at Low Load Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 77                                            |

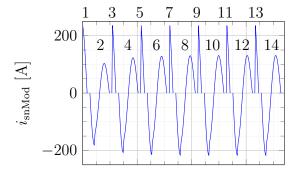

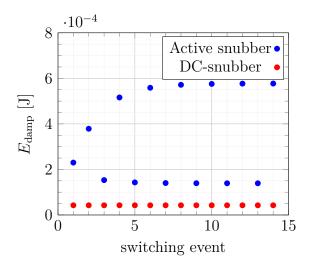

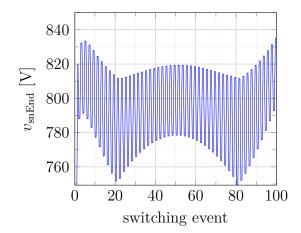

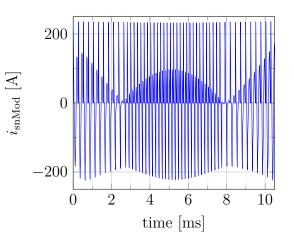

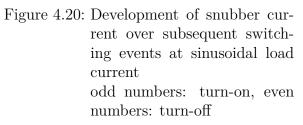

|   | 4.8               | Continuous Operation at Sinusoidal Load Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80                                            |

| 5 | Sati              | up Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 84                                            |

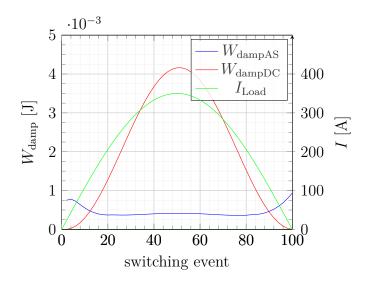

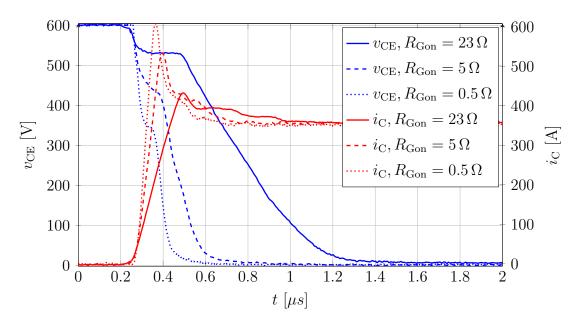

| 5 | 5.1               | Finding Appropriate Gate Resistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                                             |

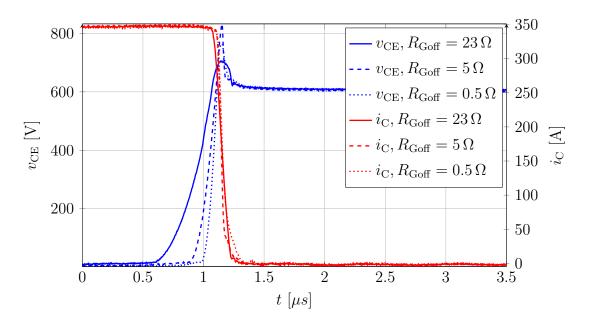

|   | 0.1               | 5.1.1 Turn-Off Event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |

|   |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                               |

|   | 5.0               | J.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                               |

|   | 5.2               | Comparing Switching Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |

|   |                   | 5.2.1 Comparison of the Turn-Off Event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                               |

|   |                   | 5.2.2 Comparison of the Turn-On Event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                               |

|   | -                 | 5.2.3 Comparison of the Diode-Recovery Event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                               |

|   | 5.3               | Behavior within Operation Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                               |

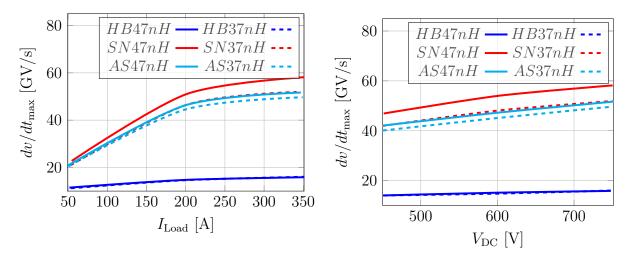

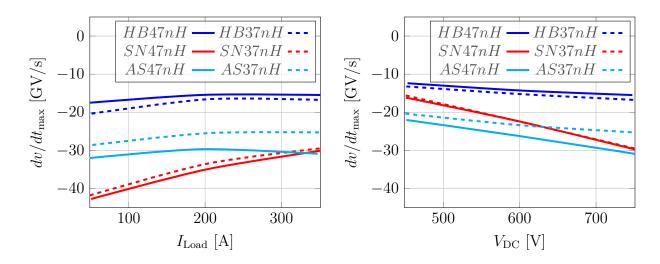

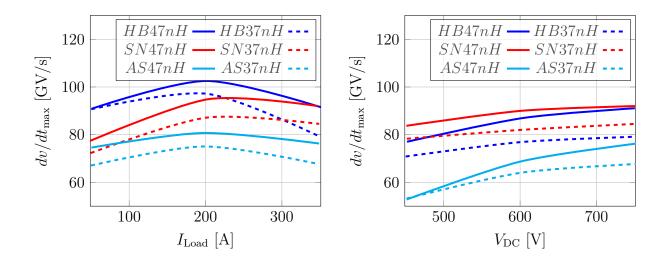

|   |                   | 5.3.1 Voltage Gradients                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                               |

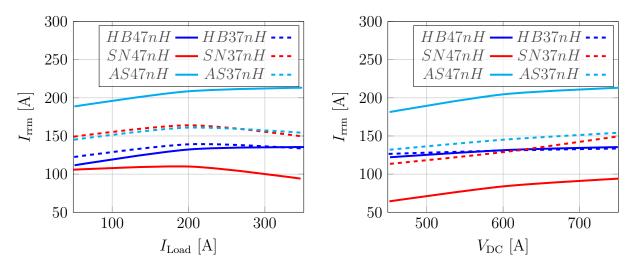

|   |                   | 5.3.2 Reverse Recovery Peak Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                               |

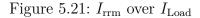

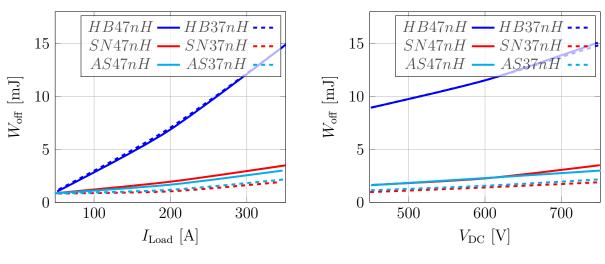

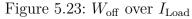

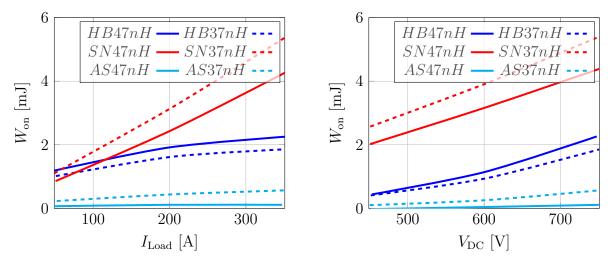

|   |                   | 5.3.3 Switching Losses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                               |

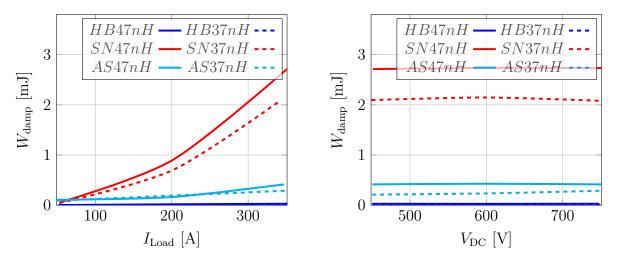

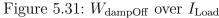

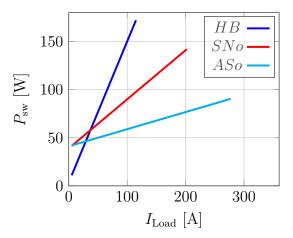

|   |                   | 5.3.4 Damping Losses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 107                                           |

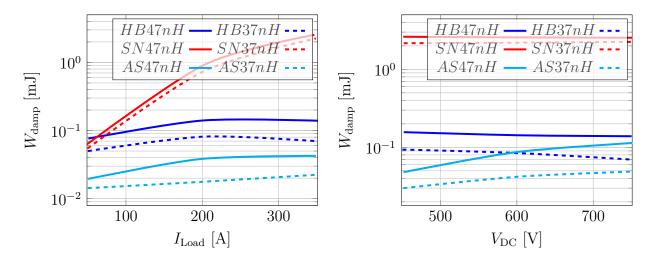

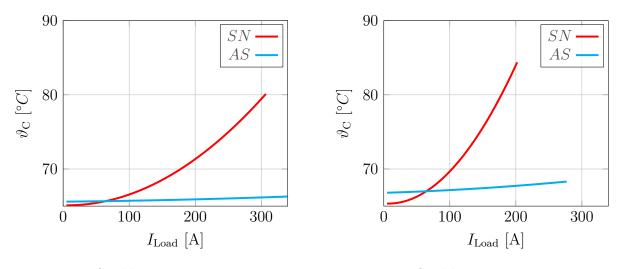

|   |                   | 5.3.5 On-State Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |

|   | 5.4               | Achievable Output Power for Inverter Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |

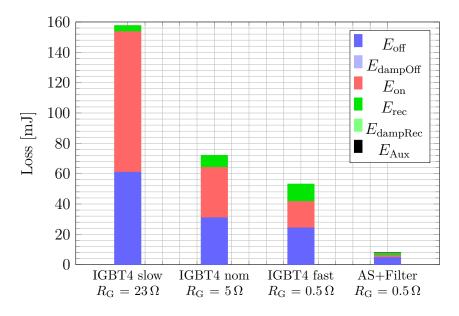

|   |                   | 5.4.1 Evaluation of Losses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 110                                           |

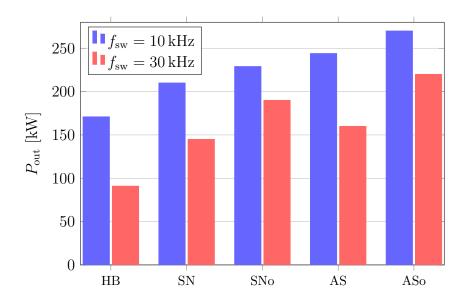

|   |                   | 5.4.2 Achievable Inverter Output Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 113                                           |

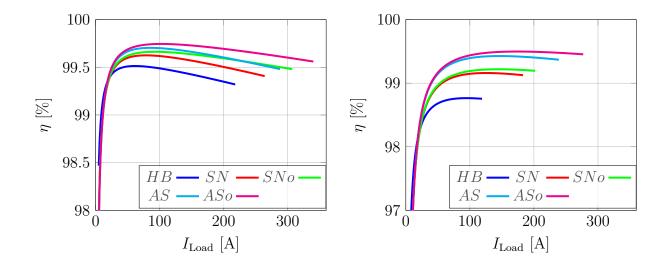

|   |                   | 5.4.3 Inverter Efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 114                                           |

| 6 | 0                 | wation with Duland I C filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 117                                           |

| 6 | <b>Оре</b><br>6.1 | eration with Pulsed LC filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                             |

|   |                   | Active Filter Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                               |

|   | 6.2               | Filter Dimensioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                               |

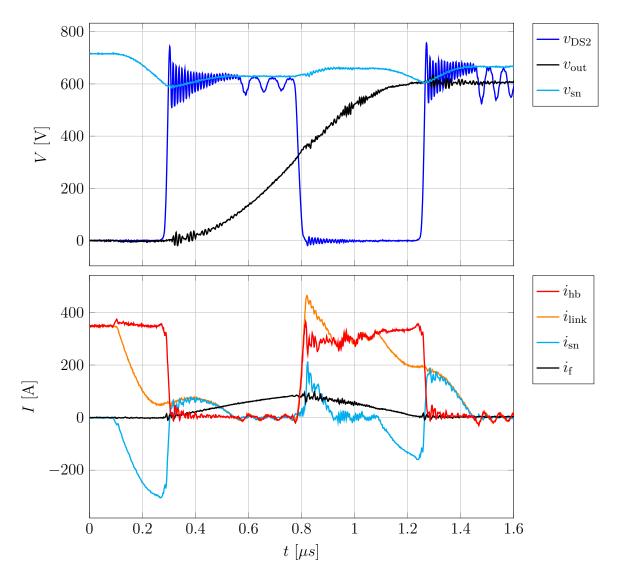

|   | 6.3               | Discharge Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                               |

|   | 6.4               | Charge Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                               |

|   | 6.5               | Comparison to IGBT-Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 123                                           |

| 7 | Sun               | nmary and Outlook                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 127                                           |

|   | 7.1               | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 127                                           |

|   | 7.2               | Outlook                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 129                                           |

| Α | Mat               | hematical derivations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 131                                           |

| A | A.1               | Calculation of Density of States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -                                             |

|   |                   | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               |

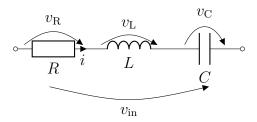

|   | A.2               | Equations of an RLC Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                               |

|   | 1 9               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 194                                           |

|   | A.3               | Analytical Derivation of Active Snubber Turn-On                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                               |

|   | A.3               | Analytical Derivation of Active Snubber Turn-OnA.3.1Fundamental EquationsControlFundamental EquationsControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControlControl </td <td>134</td> | 134                                           |

|   | A.3               | Analytical Derivation of Active Snubber Turn-OnA.3.1Fundamental EquationsA.3.2Solution for the First Interval                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 134<br>135                                    |

|   | A.3               | Analytical Derivation of Active Snubber Turn-OnA.3.1Fundamental EquationsA.3.2Solution for the First IntervalA.3.3Solution for the Second Interval                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 134<br>135<br>136                             |

|   | A.3               | Analytical Derivation of Active Snubber Turn-OnA.3.1Fundamental EquationsA.3.2Solution for the First IntervalA.3.3Solution for the Second IntervalA.3.4Solution for the Third Interval                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 134<br>135<br>136<br>137                      |

|   | A.3               | Analytical Derivation of Active Snubber Turn-OnA.3.1Fundamental EquationsA.3.2Solution for the First IntervalA.3.3Solution for the Second Interval                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 134<br>135<br>136<br>137                      |

|   | A.3<br>A.4        | Analytical Derivation of Active Snubber Turn-OnA.3.1Fundamental EquationsA.3.2Solution for the First IntervalA.3.3Solution for the Second IntervalA.3.4Solution for the Third Interval                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 134<br>135<br>136<br>137<br>139               |

|   |                   | Analytical Derivation of Active Snubber Turn-OnA.3.1Fundamental EquationsA.3.2Solution for the First IntervalA.3.3Solution for the Second IntervalA.3.4Solution for the Third IntervalA.3.5Solution for the Fourth Interval                                                                                                                                                                                                                                                                                                                                                                                                                                   | 134<br>135<br>136<br>137<br>139<br>142        |

|   |                   | Analytical Derivation of Active Snubber Turn-OnA.3.1Fundamental EquationsA.3.2Solution for the First IntervalA.3.3Solution for the Second IntervalA.3.4Solution for the Third IntervalA.3.5Solution for the Fourth IntervalAnalytical Derivation of Active Snubber Turn-Off                                                                                                                                                                                                                                                                                                                                                                                   | 134<br>135<br>136<br>137<br>139<br>142<br>142 |

|     |        | A.4.4 Solution for the Third Interval  | 150                                                                                                                                                                                                                                                                                         |

|-----|--------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

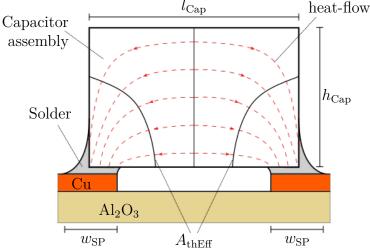

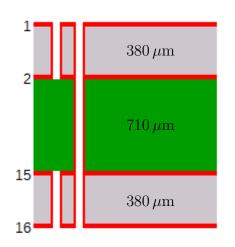

|     | A.5    | Determining the Thermal Resistance     | 156                                                                                                                                                                                                                                                                                         |

|     | A.6    | Inverter Calculation Scheme            | 159                                                                                                                                                                                                                                                                                         |

| В   | Deta   | ailed Setup Description                | 162                                                                                                                                                                                                                                                                                         |

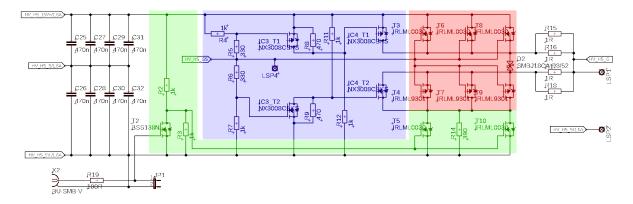

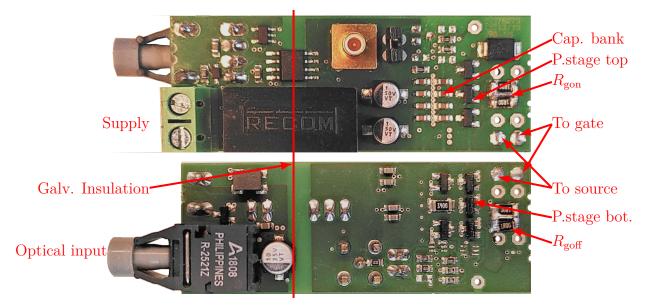

|     | B.1    | Gate Driver                            | 162                                                                                                                                                                                                                                                                                         |

|     | B.2    | Basic Measurement Setup                | 164                                                                                                                                                                                                                                                                                         |

| С   | Doc    | umented Data                           | 166                                                                                                                                                                                                                                                                                         |

|     | C.1    | Model Coefficients for Loss Estimation | 166                                                                                                                                                                                                                                                                                         |

| Lis | t of   | Figures                                | 167                                                                                                                                                                                                                                                                                         |

| Lis | t of   | Tables                                 | 170                                                                                                                                                                                                                                                                                         |

| Lis | t of   | Symbols                                | 171                                                                                                                                                                                                                                                                                         |

| Lis | t of   | Abbreviations                          | and the Thermal Resistance       156         alculation Scheme       159         Description       162         er       162         surement Setup       164         Pata       166         fficients for Loss Estimation       166         167       170         pms       179         180 |

| Bil | oliogi | raphy                                  | 180                                                                                                                                                                                                                                                                                         |

| Lis | tof    | own Publications                       | 193                                                                                                                                                                                                                                                                                         |

# Kurzfassung

MOSFETs aus Siliziumcarbid setzen sich zunehmend als sinnvoller Ersatz für etablierte Silizium-IGBTs durch. Dennoch kann als großer Nachteil die weiterhin hohe Defektdichte im Rohmaterial genannt werden. Um die Ausnutzung des Halbleitermaterials zu verbessern, bietet sich insbesondere die Reduktion von Halbleiterverlusten an. Diese setzen sich aus Schaltverlusten und Durchlassverlusten zusammen. Hierbei sind die Durchlassverluste durch den Einschaltwiderstand abhängig von der Durchbruchspannung des Bauteils und die Schaltverluste von der erreichbaren Schaltgeschwindigkeit. Letztere ist dabei limitiert durch die maximale Abschaltüberspannung, welche ebenfalls von der Durchbruchspannung sowie der Streuinduktivität abhängt. Somit ist bei signifikanter Reduktion der Streuinduktivität eine Reduktion der Gesamthalbleiterverluste zu erwarten.

In dieser Arbeit werden dabei zunächst der Stand der Technik dargelegt und wesentliche Bauteileigenschaften und Aufbaulimitierungen erklärt. Entscheidende Limitierungen in der Reduktion der Streuinduktivität stellen dabei dessen Verteilung auf Zwischenkreis und Leistungsmodul, die Verbindung zwischen beiden sowie Anforderungen an automatisierte Fertigung dar. Als mögliche Lösung werden DC-Snubber diskutiert, wobei diese durch hohe Dämpfungsverluste für höhere Ströme uninteressant werden.

Darauf aufbauend wird ein aktiv gesteuerter Snubber vorgestellt und dessen Betriebsweise am Beispiel einer Halbbrücke beschrieben. Die Schaltung erlaubt dabei eine starke Reduktion der Streuinduktivität im Abschaltmoment, wodurch Abschaltverluste und Durchlassverluste verbessert werden. Zudem besitzt die Schaltung eine große Streuinduktivität im Einschaltvorgang, wodurch Einschaltverluste vernachlässigbar werden. Desweiteren wird die Betriebsweise analytisch beschrieben, wodurch sich Optimierungsmöglichkeiten für zero-current-switching des Hilfsschalters aufzeigen.

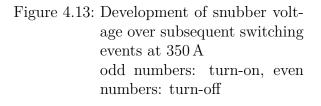

Anschließend wird das hergeleitete Modell mit Messungen validiert, mit dessen Hilfe das Schaltungsverhalten für aufeinanderfolgende Schaltvorgänge berechnet und mit einem DC-Snubber verglichen. Hierbei zeigt sich, dass die Spannung des Snubber-Kondensators alternierend um einen stabilen Endwert konvergiert und für gleiche maximale Kondensatorspannung die Snubberkapazität der Hälfte eines DC-Snubbers entspricht.

Für eine Bewertung der Ausnutzung werden exemplarisch Drei-Phasen-Inverter mit Hilfe messtechnisch bestimmer Charakterisierungsdaten für Schaltfrequenzen von 10 kHz und 30 kHz ausgelegt. Neben einer konventionellen Halbbrücke, einer Halbbrücke mit DC-Snubber und der Schaltung mit aktivem Snubber werden Setups für optimiertes Durchlassverhalten abgeschätzt. Um unbekannte Temperatureinflüsse optimierter Halbleiter zu vernachlässigen, wird dabei nur die Stromabhängigkeit des Einschaltwiderstandes berücksichtigt. Für 10 kHz zeigt sich dabei eine mögliche Steigerung der Ausgangsleistung von 35 % für nicht optimierten MOSFET und von 59 % für optimierten MOSFET.

Zuletzt wird mit der vorgestellten Schaltung ein LC-Filter aktiv angesteuert. Dabei soll der Einsatz für Anwendungen mit Begrenzungen in der Spannungssteilheit und ein Austausch konventioneller IGBTs geprüft werden. Hierbei konnte ein Zusammenhang mit der Snubberspannung und dem Timing des Pulsmusters für den Filter festgestellt werden. Ein Vergleich der Schaltverluste zu einem IGBT-Setup ähnlicher Leistung zeigte dabei eine Verlustreduktion von bis zu Faktor 20 bei gleichzeitig flacherer Flanke. Als nachteilig zeigte sich jedoch das Timing des aktiven Snubbers für die Minimierung des Filters.

# Abstract

Silicon carbide MOSFETs have gained popularity over established silicon IGBTs. However, a major drawback is a still high defect density in the raw material. To improve the utilization of the semiconductor material, especially the reduction of semiconductor losses is reasonable. The semiconductor losses can be separated into conduction and switching losses. The conduction losses with the on-state resistance are dependent on the device breakdown voltage and switching losses from the achievable switching speed. Latter is limited by the maximum turn-off voltage overshoot, which is also dependent on the breakdown voltage and from the system stray inductance. Hence, significantly reducing the stray inductance impacts both conduction and switching losses.

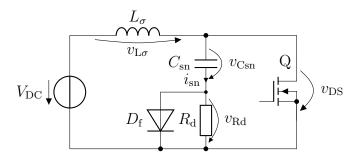

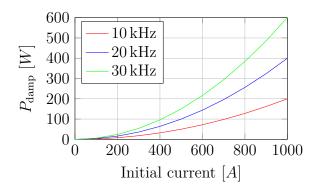

In this work, the current state-of-the-art is stated, important device properties and setup limitations are outlined. It is shown that the distribution of the stray inductance above the DC-link, the power module and the interconnection of both as well as requirements for automated production are major limitations for its reduction. As a potential solution DC-snubbers are discussed but due to increasing damping losses they become uninteresting for higher currents.

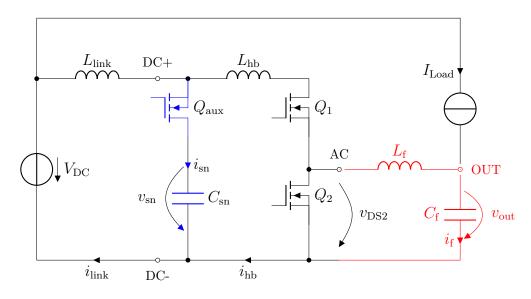

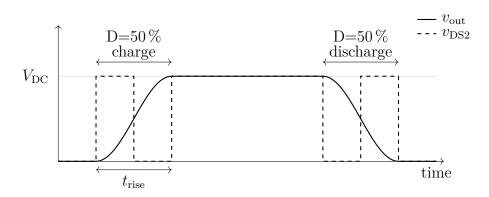

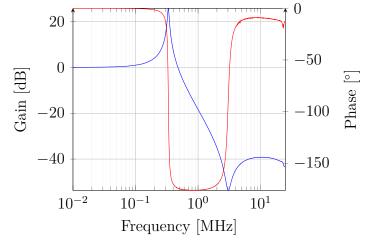

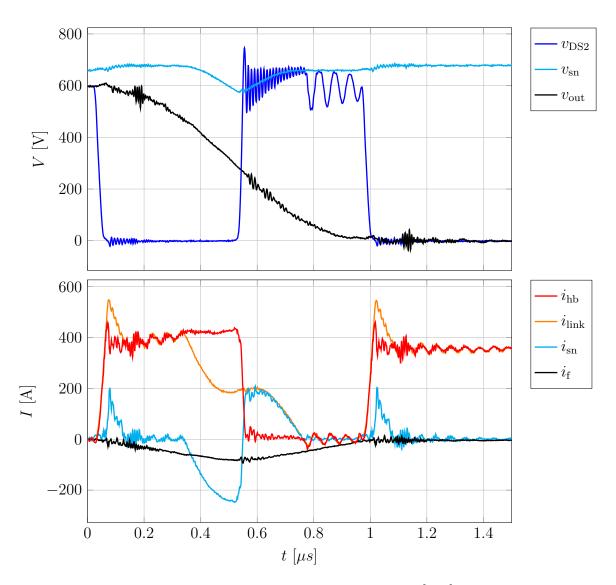

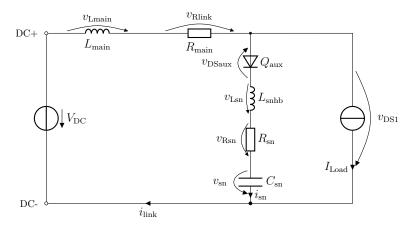

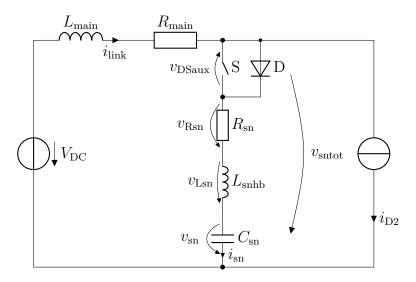

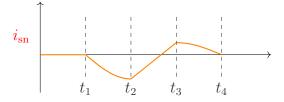

Considering this, an active controlled snubber is introduced and its manner of operation with a halfbridge is described. The setup allows a strong reduction of the stray inductance for turn-off, which allows improvement of turn-off and conduction losses. Additionally, the setup provides a large stray inductance for turn-on, whereby the turn-on losses become negligible. Further, the manner of operation is described analytically, which shows opportunities for zero-current-switching of the auxiliary switch. Afterwards, the derived model is validated using measurements and is used to predict the behavior for subsequent switching events.

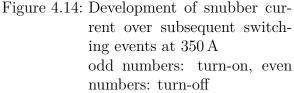

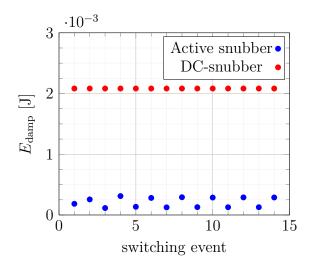

The results are compared with a similar DC-snubber setup. It could be found that the snubber voltage shows an alternating but stable behavior and, a maximum snubber voltage, which is half of that of a similar DC-snubber.

To judge the utilization, three-phase inverters have been designed for switching frequencies of 10 kHz and 30 kHz based on data measured with reference designs. In addition to a conventional halfbridge, a halfbridge with DC-snubber and the active snubber setup, further setups with an optimized conduction behavior are estimated. To neglect unknown temperature dependencies of hypothetically optimized semiconductors, only the current dependency is considered. For a switching frequency of 10 kHz, a possible increase in the inverter output power of 35 % could be found for a non-optimized semiconductor and 59 % for an optimized MOSFET.

Finally, the introduced setup is used to actively drive a small LC-filter. Here, the usage in applications with restrictions on the maximum voltage slope shall be evaluated. A dependency of the snubber voltage and the timing of the filter pulses could be found. A comparison to a state-of-the-art IGBT setup with similar output power showed a reduction in switching losses by a factor of 20 with a simultaneously lower voltage slope. However, it could be found that the time constants of the snubber circuit limit the minimization of the LC-filter.

# **1** Introduction

Power electronics are a key technology for efficient processing of electrical energy. In the past, increasing energy costs were a major driver for continuous improvements in semiconductor and material technology. Today, the increasing awareness of resource depletion and environmental pollution together with the increasing demand for energy presupposes the use of evolved energy conversion and storage technologies. This has led to a transformation process from using fossil-based energy sources to electrification powered by renewable energies, see [1]. Power electronics is a key technology for increased energy efficiency and e-mobility is an accelerator for further technology development, see [2]. While in most applications power electronic devices are used as switches, this allows an efficient processing of electrical energy, which is a major driver for success of power electronics in recent decades. During the development of a power electronic device the reduction of losses is one of the most important goals because it affects the achievable output power and efficiency immediately. Besides the conduction losses of a turned-on semiconductor, the switching losses are relevant, especially in applications with higher switching frequencies. Today, in most low-voltage applications up to approximately 1 kV metaloxide-semiconductor field-effect-transitors (MOSFETs) are the preferred switches. Because of low switching losses, it allows the highest switching frequencies, but the conduction losses caused by a high on-state resistance increase if the device is rated for higher voltages, see [3, 4]. For higher voltage ratings up to approximately 6.5 kV the insulated gate bipolar transistor (IGBT) shows acceptable conduction losses. Because of the bipolar behavior, conduction losses for high current operation points are lower. To limit the overall losses, an IGBT used at high switching frequencies must be rated for low current and voltage, [4] S.3ff.

As in other areas, silicon (Si) is still the most commonly used material for power semiconductors, see [5]. It is the most mature material in terms of production, technical expertise and low cost. Nevertheless, the physical characteristics of silicon make further significant improvements challenging. Devices made from silicon show some important limitations in switching speed, the capability of blocking voltage and the maximum operation temperature.

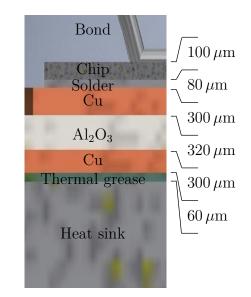

Since several years, materials with higher bandgap, such as silicon carbide (SiC) or gallium nitride (GaN) are subject of research or are even available on the market. Their advantages compared to silicon are well known, cf. [5–7]. Due to the availability of vertical SiC-MOSFET devices allowing higher breakdown voltages compared to lateral GaN devices, SiC is interesting for higher power applications [8]. Nevertheless, excessive material cost, cf. [9], and a strong tendency to oscillations, cf.[10], may limit the possible substitution of Si-IGBTs in many classic applications with SiC-MOSFET devices. Therefore, several laborious approaches are considered to increase the output power per chip area or the power density respectively. One approach is a better cooling structure, which allows higher losses and in conclusion, a higher power output per volume. Power modules as assemblies of several semiconductor dies usually soldered on a ceramic substrate with advanced cooling structures such as PinFin base plates and double-sided cooled devices or combinations have been topic of research and are available on the market [11, 12]. Other approaches for loss reduction are to influence the switching behavior, see e.g. [13, 14], or optimizing the commutation circuit, e.g. [15, 16]. For example, a reduction of the stray inductance has a positive effect towards a clean switching event [17] with less ringing and reduction of voltage overshoot at turn-off. Hence, the switching speed can be increased - with similar overvoltage - to reduce switching losses, or an operation at higher DC-link voltage can be allowed to improve the possible power output of an inverter.

Because the stray inductance of the switching cell consists of several partial inductances, like the equivalent series inductor (ESL) of the DC-link capacitor, the inductance of the power module and the connection between both, a reduction is challenging. Major challenges are e.g. the suitable assembly technologies or materials and creepage distances for higher voltage classes. Additionally, acceptable efforts for production and space limitations, have a significant influence on the total production cost. Therefore, for an optimal result the collaboration of capacitor and power module vendors might be required.

# 1.1 Thematic Classification

This work belongs to the field of electrical engineering with a focus on power electronics. It deepens the topics of minimizing switching losses and characteristics of SiC-MOSFETs and optimization of the switching behavior related to circuit parasitics at higher power classes. The overall goal is to develop an improved switching cell for the used switching technology at fastest switching for highest possible power output and efficiency. To achieve this goal, this work concerns with the corresponding technologies, e.g. trade-offs in semiconductor device dimensioning, optimizing circuit parasitics and the usage of snubber capacitors. Finally, an optimized commutation circuit is proposed focusing to enhance the achievable power output by allowing both higher switching speed and simultaneously higher DC-Link voltage.

# **1.2 Problem Description**

As already mentioned, SiC-MOSFETs are a reasonable substitute for Si-IGBT in many applications. Since several years, SiC-MOSFETs have been available on the market [18]. Compared to Si-IGBTs in the 1.2 kV class, SiC-MOSFETs allow much faster switching speed and lower conduction and switching losses. However, while common system assemblies are designed for IGBTs, a simple replacement of the semiconductor dies may not lead to the optimal utilization of the expensive SiC-material. This is mainly related to the stray inductance of the switching cell limiting the switching performance as explained below for a common drive inverter.

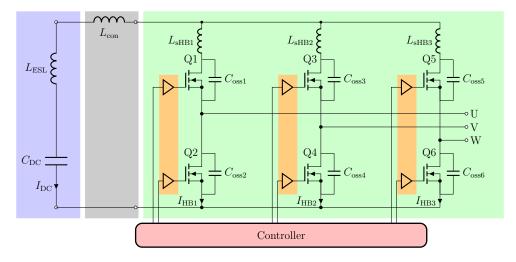

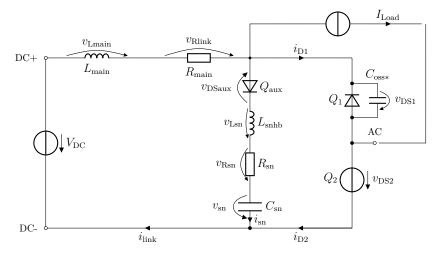

A drive inverter consists of at least a power semiconductor arrangement, cf. Fig. 1.1 (green), connected to the driver electronic (orange), and a control unit (red). Depending on the application and power range, the connection (gray) to a DC capacitor (blue) can be carried out directly or through an arrangement such as a printed circuit board (PCB) (low-power) or a copper plate busbar arrangement (mostly high-power). The most common power semiconductor arrangement for this application is a three phase-leg configuration consisting of three halfbridges, see Fig. 1.1. For power levels above 10 kW power module assemblies are available, which provide a more compact design compared to a discrete assembly and usually a better cooling structure.

Figure 1.1: Basic inverter schematic with components

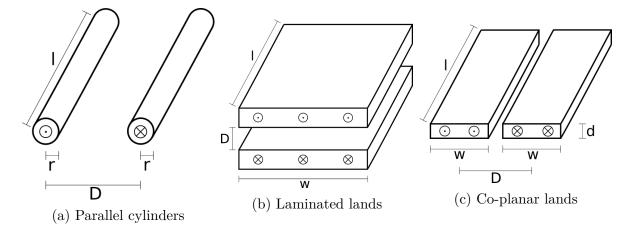

An important goal during construction is a low stray inductance between the DC-link capacitance  $C_{\rm DC}$  and the semiconductor being a key factor for clean switching [17] and low voltage overshoot [19]. A major challenge in reducing stray inductance is that this inductance is distributed over the capacitor, connection and the power module halfbridge. Confer Fig. 1.1, with the ESL of the capacitor  $L_{\text{ESL}}$ , the connection inductance  $L_{\text{con}}$  and the inductance of a halfbridge  $L_{\rm sHBn}$ , which is depicted as a lumped inductance. Because the inductance of a common planar conductor arrangement, cf. Fig. 2.6b, increases with conductor length and with the distance between the conductors or decreases with the width of a conductor, cf. Sect. 2.2.1, the problem can be derived by rationality. An inductance goal of zero can be achieved in theory by reducing distance and length to zero and increasing the width to infinity. Because of an infinite width immediately leads to an infinite effort in terms of material, cost and space, a widening of the width is very limited. Similarly, the minimum distance is usually limited by the maximum insulation voltage. Hence, further reduction relates also to the availability of better insulation material. In conclusion, only a reduction in the distance between the DC-link capacitor and the power semiconductor described by the conductor length is a reasonable solution.

However, the dimensioning of DC-link capacitance is related to the allowed current ripple and voltage ripple and the switching frequency [20]. Thus, common DC-link capacitors are comparatively large, see [21] and a small proximity between the capacitor and the semiconductor might be hard to achieve considering the requirement for a manageable inverter assembly into account. In summary, an optimal design is limited by the available capacitor technology, the design of the power module and a connection technology which must be acceptable for series production in terms of effort and costs. Thus, a close collaboration between capacitor supplier, power semiconductor supplier and potential customer is necessary.

For improved switching performance, on the one hand, a low stray inductance reduces the voltage overshoot during the negative current slope and thus, enabling faster switching at turn-off, the use of a higher DC-link voltage or alternatively a semiconductor technology with lower breakdown voltage and lower on-state resistance. On the other hand, a lower stray inductance increases the switching losses at turn-on [22, 23]. While a high stray inductance leads to a voltage drop during turn-on, this voltage drop is lower with a small inductance. Hence, the semiconductor voltage during the current slope is higher with lower stray inductance and the losses are increased.

Consequently, for optimal efficiency, a compromise between switching and conduction losses, electromagnetic interference (EMI), DC-link voltage and acceptable manufacturing effort has to be made.

Another limitation of further switching loss reduction is the voltage slope allowed by the electric motor. A high voltage slope leads to stress on motor windings [24] as well as higher bearing currents [25] with a negative effect on the motor lifetime. Additionally, depending on the cable length between the motor and inverter, an edge reflection may occur on the motor terminals, leading to high peak voltages [26] and also higher insulation stress.

In conclusion, besides the allowed voltage slope, the energy in the stray inductance as root cause of overvoltage and ringing is one of the major obstacles for optimized switching behavior in terms of losses and oscillations.

In this work, a setup is presented, which actively makes use of this energy to significantly reduce the voltage overshoot, oscillation amplitude and switching losses. This allows a higher DC-link voltage and a better utilization of the wide-bandgap material (WBM) semiconductor device. Furthermore, it separates the requirements of a high capacitance and low inductance of the DC-link capacitor and therefore, it allows the usage of a less advanced DC-link capacitor and connection technology with higher stray inductance. Furthermore, it is shown that the proposed setup is compatible with the actively pulsed filter presented by [27]. Thus, it is also suitable for applications with a demand for very slow voltage slopes.

# 1.3 Hypothesis and Research Questions

In this chapter, the research hypotheses are derived from the problem description mentioned above. The research questions serve as a basis for the investigations carried out in this work.

- An optimized switching behavior can be achieved by an active management of the energy stored in the stray inductance.

- This has a significant contribution to increasing the efficiency and output power.

- Through the active energy management the semiconductor utilization is increased.

- With an active management of the energy stored in the stray inductance, concepts with larger stray inductance are possible and reasonable.

- The switching losses can be reduced and thus, higher switching frequencies and the operation of filters actively driven by the halfbridge for a reduced voltage slope are possible.

The above-listed hypotheses allow the formulation of the research questions.

- How can the energy in the stray inductance be used actively for improved switching characteristics?

- What influence does the found method have on the switching behavior?

- How large is the achievable influence on the system performance?

- Are the additional measures disadvantageous for the application?

Goal of this work is to develop a system with significantly increased performance, efficiency and improved utilization of WBM semiconductors. The system shall serve as a substitute for conventional power semiconductor modules used in inverters, as outlined in Chapter 1.2.

# 1.4 Structure of the Thesis

At this point, a short overview of the following chapters shall be given.

First, an introduction into related topics and technology is given with focus on effects and characteristics which are relevant for this work.

Subsequently, an optimized commutation circuit is presented. Further, its principle of operation to manage the energy in the stray inductance is described and a mathematical model for the turn-on and turn-off event is derived.

Then, the power modules used for measurements are introduced, two module variants serving as reference types and the module with the introduced optimized commutation circuit. Afterwards, the mathematical models are compared with measurements, and significant effects are discussed. Subsequently, the derived mathematical model is used to predict the circuit behavior during different types of operation.

The next chapter compares the characteristics of two reference module variants with the optimized type. The switching behavior is compared at different operation points and the achievable output power during inverter operation is estimated by calculation.

The next to last chapter shows the operation of a LC-filter actively driven by the optimized circuit to present a substitute for conventional IGBT inverters where, due to a switching speed constraint, WBM semiconductors may not be reasonable. Therefore, a comparison with a state-of-the-art IGBT module is given.

Finally, a summary of the work and it's important findings is given and an outlook shall point out future research directions.

# 2 Basics and Technology Review

# 2.1 Power Semiconductor Devices

For a better understanding of the effects observed in this work, a basic introduction in common power semiconductors, the materials and their properties is given below. First, semiconductor materials with their characteristics which are important for power applications are outlined with special focus on the advantages of WBM compared to Si. Afterwards, characteristics of bipolar diodes as well as MOSFETs are described. In particular, attention was paid on device related effects which might have a strong influence in the circuit presented in this work and which should be considered for proper dimensioning.

## 2.1.1 A Short Introduction to Semiconductor Materials

In power electronics, Si is still the most common material. Its characteristics are wellknown and as a result the technology is well established. However, silicon shows some limitations, cf. Tab. 2.1, effecting the achievable performance of the semiconductor device. To overcome these limitations, WBM are an interesting and emerging solution. In the recent years, silicon carbide in 4H configuration (4H-SiC) and GaN have gained popularity and are the most suitable wide-bandgap materials in terms of technological maturity. Nevertheless, both materials are still facing problems in material quality [3, 28]. However, SiC has the highest level of development for vertical devices allowing higher breakdown voltages, see [5], which makes it the preferred material for higher power devices.

In Table 2.1 some important material properties of the mentioned semiconductors are listed. However, it should be mentioned that the material parameters strongly variate for WBM in the literature which might be explained by variances in the quality of the investigated material.

| 1 1                                      |                      |                             |                             |

|------------------------------------------|----------------------|-----------------------------|-----------------------------|

|                                          | Si                   | 4H-SiC                      | GaN                         |

| $W_{\rm G}  [{\rm eV}]$                  | 1.12 <sup>D</sup>    | $3.25^{\mathrm{D}}$         | $3.44^{\mathrm{C}}$         |

| $E_{\rm crit}$ *[V/cm]                   | $200k^{A},300k^{C}$  | $2 M^{A}, 3.18 M^{C}$       | $3M-3.5M^{C}$               |

| $v_{\rm sat}  [{\rm cm/s}]$              | $1.05 \cdot 10^{7A}$ | $2 \cdot 10^{7 \mathrm{A}}$ | $2.5\cdot 10^{7\mathrm{A}}$ |

| $\mu_{\rm n}  [{\rm cm}^2/{\rm Vs}]$     | $1400^{\rm C}$       | $500^{\rm B}, 1000^{\rm A}$ | $900^{\rm C}, 2000^{\rm B}$ |

| $\mu_{\rm p}  [{\rm cm}^2/{\rm Vs}]$     | $470^{A}$            | $50^{\rm B}, 115^{\rm A}$   | $10^{\rm C}$                |

| $\varepsilon_{\rm r}$ [1]                | $11.8^{\rm B}$       | $9.8^{\mathrm{B}}$          | $7.8^{\mathrm{B}}$          |

| $CTE [1 \cdot 10^{-6} ^{\circ}\text{C}]$ | $2.59^{A}$           | $4.3^{A}$                   | $5.4-7.2^{\circ}$           |

Table 2.1: Semiconductor properties at 300K

$E_{crit}$  is a function of doping. Thus, it should be understood as an estimation. References: A:[4], B:[28], C:[29], D: Appendix A.1

A higher bandgap between valence and conduction band makes the semiconductor more robust against thermal charge carrier generation and other extrinsic influences like an

electric field. This results in a significantly lower intrinsic concentration of charge carriers

at a given temperature. According to [30] p.21ff, the intrinsic carrier concentration can be calculated with a known density-of-states in the conduction,  $N_{\rm C}$ , and valence band,  $N_{\rm V}$ , with

$$n_{\rm i} = \sqrt{N_{\rm C} N_{\rm V}} e^{-\frac{W_{\rm G}}{2k\vartheta}} \tag{2.1}$$

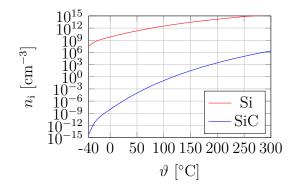

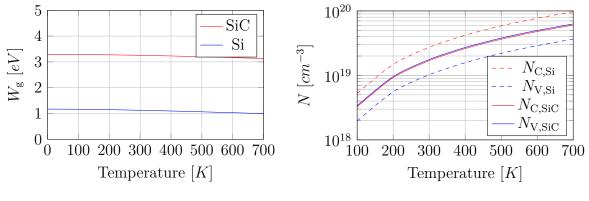

where k is the Boltzmann constant,  $W_{\rm G}$  is the bandgap energy and  $\vartheta$  is the absolute temperature. Figure 2.1 shows the intrinsic carrier concentration as a function of temperature for silicon and SiC with the density of states calculated in Appendix A.1.

In Fig. 2.1 it can be seen that with an exemplary chosen doping concentration of  $1 \cdot 10^{15}$  cm<sup>-3</sup>, see [4, 30], the intrinsic charge generation becomes significant for a silicon device at temperatures above 300 °C. In comparison, SiC allows higher temperatures and thus, - due to a higher temperature gradient - a higher heat dissipation and power density. However, a possible limitation might be the robustness against high temperatures of the used packaging materials.

Figure 2.1: Intrinsic carrier concentration

### 2.1.2 Introduction to Diodes

By combining a P and N doped semiconductor an abrupt PN junction is formed. The concentration of donor and acceptor atoms,  $N_{\rm D}$  and  $N_{\rm A}$ , which are for silicon usually ionized at room temperature [30], leads to a diffusion current and a charge displacement. This results in an electric field which drives a current in the opposite direction. For a P-N junction without external current and field, the diffusion and field driven current cancel each other out, so that a diffusion voltage can be calculated along the P-N junction width. By using  $n_{\rm i}$  the diffusion potential for an abrupt P-N junction can be calculated according to [30] p.81 with

$$V_{\text{diff}} \approx \frac{k\vartheta}{q} \ln(\frac{N_{\text{D}}N_{\text{A}}}{n_{\text{i}}^2}).$$

(2.2)

For the exemplary chosen doping concentrations  $N_{\rm D} = N_{\rm A} = 1 \cdot 10^{15} \,\mathrm{cm}^{-3}$  the diffusion voltage at 300 K can be calculated for a Si and SiC junction to  $V_{\rm diff,Si} = 0.6 \,\mathrm{V}$  and  $V_{\rm diff,SiC} = 2.5 \,\mathrm{V}$ . Hence, the conduction losses can be expected to be much higher with SiC. Furthermore, bipolar structures like diodes made from silicon carbide suffer from severe aging mechanisms such as bar-shaped stacking faults [31]. Thus, SiC bipolar diodes - and SiC-MOSFET body diodes - are not a reasonable choice for free-wheeling operation yet.

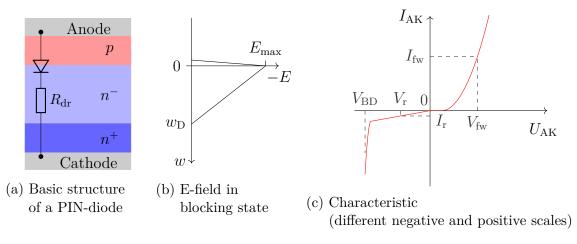

Compared to normal diodes, PIN-diodes have an intrinsic region between the P and N doped sides. Because a PIN-diode as a substructure of a MOSFET, its characteristics are explained in this chapter. The intrinsic  $n^-$  zone, cf. Fig. 2.2a, increases the blocking capability compared to a simple P-N junction. The characteristic is given in Figure 2.2c. At a defined forward current  $I_{\rm fw}$ , a forward voltage drop  $V_{\rm fw}$  from anode to cathode can be

measured. At reverse voltage operation the reverse blocking current  $I_{\rm r}$  flows from cathode to anode. For high reverse voltages the devices breaks down at a voltage of  $V_{\rm BD}$ .

Figure 2.2: PIN Diode

#### **Blocking state**

By applying a reverse voltage to the diode, an electric field is formed similar to Fig. 2.2b. Due to the lower carrier density the  $n^-$  zone the field strength decreases slower. Hence, in case the field does not enter the  $n^+$  zone, the width of the intrinsic zone  $w_{\rm B}$ , determines the blocking capability of the diode. According to [30], the width as a function of the applied voltage  $V_{\rm AK}$  can be calculated with

$$w_{\rm D} = \sqrt{\frac{2\varepsilon_{\rm s}}{qN_{\rm D}} \left(V_{\rm diff} - V_{\rm AK} - \frac{2k\vartheta}{q}\right)},\tag{2.3}$$

while  $N_{\rm D}$  is the donor concentration in the  $n^-$  region, q the unit charge and  $\varepsilon_{\rm s}$  is the semiconductor permittivity, see also Table 2.1. Additionally, the depletion layer capacitance per area can be written as

$$C_{\rm D} = \frac{\varepsilon_{\rm s}}{w_{\rm D}} = \sqrt{\frac{q\varepsilon_{\rm s}N_{\rm D}}{2\left(V_{\rm diff} - V_{\rm AK} - \frac{2k\vartheta}{q}\right)}}.$$

(2.4)

#### Conduction and reverse recovery

As explained by [4] p.39, the forward voltage at the PN junction at a current density of  $10 \text{ A/cm}^2$ , which is comparatively low, is similar to the diffusion voltage  $V_{\text{diff}}$ . Thus, considering the voltage drop over the drift region resistance, which is a function of the charge carrier concentrations  $\mu_{\rm n}$  and  $\mu_{\rm p}$ , cf. Fig. 2.2a  $R_{\rm dr}$ , the forward voltage  $V_{\rm fw}$  can be estimated with

$$V_{\rm fw} \approx V_{\rm diff} + R_{\rm dr}(\mu_{\rm n}, \mu_{\rm p}) I_{\rm fw}.$$

(2.5)

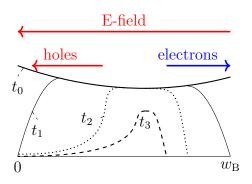

During forward bias operation, the intrinsic region is swamped with charge carriers, Fig. 2.3  $t_0$ . By applying a negative voltage on the flooded PN junction, these carriers are extracted during the interval  $t_0 < t < t_3$ . First, for  $t \leq t_1$ , the carrier concentration at the

Figure 2.3: Carrier distribution in the drift region after [32] for a strong reverse current

corners (0 and  $w_{\rm B}$ ) drops to the state of thermal equilibrium. Later, from  $t_1 < t \leq t_3$  the space-charge zone widens and the device voltage decrease to higher negative values. The extraction current can be measured as a reverse current as will be described in Section 3.4 and may cause significant losses.

As already mentioned, the PIN-structure is included in a MOSFET structure, cf. Fig. 2.2a with Fig. 2.5a. It is important to notice that at commercial free wheeling Si-PIN diodes it is common to modify the charge carrier life time to achieve an improved conduction behavior as well as a tail current during reverse recovery and thus a clean switching event with low voltage overshoot [33–35]. However, it is well known that the MOSFET intrinsic diode is not optimal. Thus, if the body diode is used as a free wheeling diode - as it is done in this work - the reverse recovery behavior might reduce the achievable device performance.

#### Forward recovery behavior

By applying a high current slope in conduction direction of a diode, the device might show a forward voltage  $V_{\rm fr}$  [36–38]. This effect, depicted in Fig. 2.9, has a very similar influence as a stray inductance and might limit the achievable switching speed. A worstcase estimation is given by [4], with the assumption of an infinite current slope and a device without swamped base, the maximum voltage can be calculated as

$$V_{\rm frm} = \frac{w_{\rm B} \cdot j}{q\mu_{\rm n}N_{\rm D}} \tag{2.6}$$

while  $\mu_n$  is the carrier mobility in the  $n^-$  region and j the current density. It should be mentioned that this effect has been evaluated for the used SiC-MOSFETs with the result of a negligible forward recovery voltage.

### 2.1.3 Introduction to MOSFETs

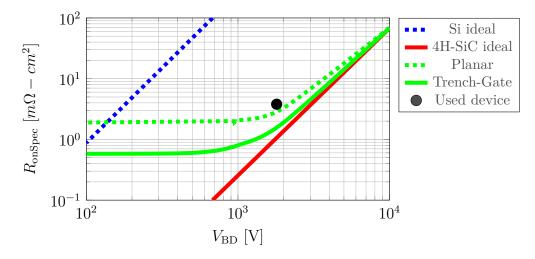

The MOSFET is the most important switching device in electronics. It is capable of operating at highest switching frequencies compared to other power semiconductors. However, silicon devices are only available for comparatively low voltages and current levels which is related to the dependence of the on-state resistance  $R_{\rm on}$  to the breakdown voltage, cf. Fig. 2.4. Considering that the drift region has a significant fraction, of the total on-state

Figure 2.4: Ideal specific on-state resistance over breakdown voltage after [39]

resistance, a rough estimation on the dependence of the implemented breakdown voltage can be found in [39] p. 15 with

$$R_{\rm on-ideal} = \frac{4V_{\rm BD}^2}{\varepsilon_{\rm s}\mu_{\rm n}E_{\rm crit}^3}.$$

(2.7)

Here, the semiconductor properties are considered by  $\varepsilon_{\rm S}$  as the semiconductor dielectric constant,  $\mu_{\rm n}$  as the electron mobility and  $E_{\rm crit}$  as the critical electric field. Due to the cubic dependence on the critical electric field, this equation indicates the strong benefits of wide-bandgap materials which is illustrated in Fig. 2.4.

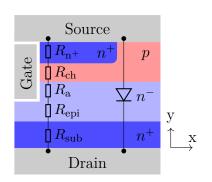

Since the availability of wide-bandgap materials the MOSFET is reasonable for applications at voltages above 1 kV. The first SiC-MOSFET with a rated break down voltage of 1 kV was commercially introduced by Cree [18] in 2011. For power electronics, higher blocking and current-carrying capability can be achieved with a vertical trench gate structure as depicted in Fig. 2.5a compared to a planar structure. It can be seen that the right-hand-side arrangement of the device equates to a PIN-diode structure. This body diode results in a reverse conductive capability which is considered with the negative quadrant of the characteristic in Fig. 2.5b. However, a body diode has some significant disadvantages compared to a dedicated anti-parallel diode in both dynamic and static behavior, cf. [40]. Additionally, for SiC-MOSFETs, as mentioned above, the bipolar structure suffers from significant aging mechanisms like bar-shaped stacking faults [31, 41, 42]. Therefore, it is not reasonable to use the body diode as a free wheeling diode as it is done with paralleled IGBT-diode combination.

Further, it has been found that the breakdown voltage of the structure shown in Fig. 2.5a is limited by the high electric field strength at the bottom side of the gate trench. According to [43] p. 496, this limitation can be overcome by implementing a shielding plate at the trench bottom. Further, the drift region has still a major contribution to the total specific on-resistance, cf. [44] p. 501. By applying a positive voltage  $V_{\rm GS}$  from Gate to Source, the conductivity of the p-region near the Gate can be modulated. A positive voltage increases the electron concentration and decreases the hole concentration in this region and for a voltage higher than a specific threshold voltage  $V_{\rm th}$  a conductive channel can be achieved.

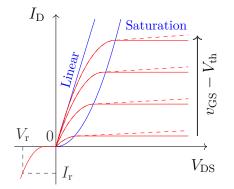

(a) Basic MOSFET structure

(b) Characteristic with solid: long channel, dashed: short channel

Figure 2.5: Vertical trench MOSFET

#### Channel modulation through Gate voltage

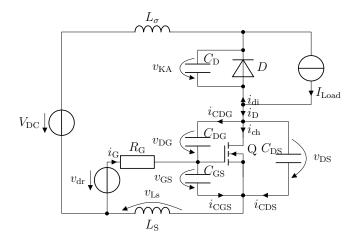

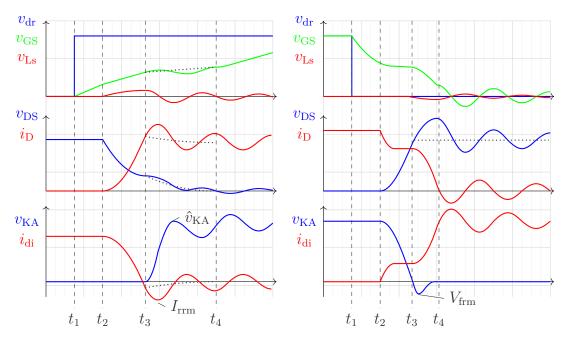

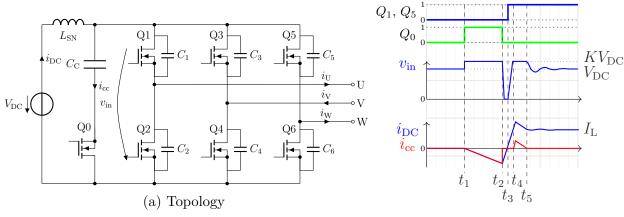

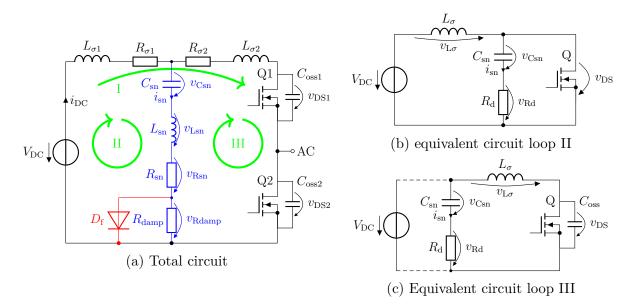

As described in [30] in detail, with the condition that the electric field strength in xdirection, cf. 2.5a, is much larger compared to the field in y-direction, and the assumption of a constant mobility the current-voltage-characteristic can be estimated as follows.