# Channel Coding for Highly Efficient Transmission in Wireless Local Area Network

Zur Erlangung des akademischen Grades

## Doktor der Ingenieurwissenschaften

von der Fakultät für Elektrotechnik und Informationstechnik der

Technischen Universität Dortmund genehmigte

#### **Dissertation**

von

## Deny Hamdani

aus Bandung, Indonesien

Tag der mündlichen Prüfung: 21.03.2012

Hauptreferent: Prof. Dr.-Ing. Rüdiger Kays Koreferent: Prof. Dr.-Ing. Jürgen Götze

#### **ACKNOWLEDGMENT**

First of all, I would like to express my sincerest gratitude to my *Doktorvater*, Prof. Dr.-Ing. Rüdiger Kays, for his inspiring guidance revealed during my doctoral education at the Technische Universitaet Dortmund. I am really grateful to him for all his fruitful help and for his inspiring insights that supported this work very much. I would like also to gratefully thank Prof. Dr.-Ing. Jürgen Götze for co-supervisory of this thesis and his recommendation for my DAAD scholarships. I thank also sincerely to examiners: Prof. Dr.-Ing. Christian Rehtanz and Prof. Dr.-Ing. Peter Krummrich, for their advisory opinion.

I wish to thank my roommate Dr.-Ing. Wolfgang Endemann for his charming friendship and many fruitful discussions as well as his support in finishing-touch of this dissertation. Many thanks also to my labmates for their help and friendship: Yasser Al-Nahlaoui, Christian Schilling, Beatriz Aznar, Dominik Lubeley, Thomas Jäger, Oliver Hundt, Dirk Seebeck, Harald Gebhard, Klaus Jotschulte, Heidrun Schettke, Helga Scheffler, Jürgen Marsch and also, *last but not least*, Stefan Nowak. They made Lehrstuhl fuer Kommunikationstechnik to become an incredible, pleasant environment for research and study.

I am grateful to all my friends in Ruhrgebiet, Aachen and Karlsruhe for making my stay in Germany a very pleasant one, especially, Supriyanto, Nurrakhman Yulianto, and Aulia Rahman, who have cordially helped me in finishing my study. I also wish to thank gratefully Mrs. Barbara Schwarz-Bergmann and DAAD for their cordial assistance and scholarships during my study in Germany. I am also grateful to Prof. Dr. Suwarno, Dr. Djoko Darwanto Gitokarsono and Prof. Dr. Ngapuli Irmea Sinisuka for their support, guidance and encouragement in my professional life. Special thanks also to Dr. Sony Suhandono and Dr. Endra Susila for valuable discussion and their grammatical review on technical English writing of this dissertation.

Finally, I would like to express special thanks to my family. I sincerely thank my parents, Mamah and Bapa, for their everlasting love, pray, encouragement, and support which led me to possibly earn such high educational degree. No words are sufficient to show my appreciation and respect for them. My wife, Dr.-med Ira Safitri, has always supported and encouraged me during my study. Her true love and cordial support have encouraged me to finish my study. I am especially grateful to her for taking such a loving care of our beloved sons Farhan, Fauzan and Fathur Denira. I also wish to thank Amah and Apah for their cordial support, and also my sister, all sisters- and brother-in-laws who helped us in many ways. I greatly appreciate their thoughtful support. My gratitude goes also to my late teacher Pak Muslim for teaching me about the blessed life.

#### ACKNOWLEDGMENT

#### **ABSTRACT**

Since their rediscovery, Low Density Parity Check (LDPC) codes sparked high interests due to their capacity-approaching performance achieved through their low decoding complexity. Therefore, they are considered as promising scheme for channel coding in future wireless application. However, they still constitute disadvantage in their high encoding complexity. The research on practical LDPC codes with good performance is quite challenging. In this direction their potential characteristics are explored with respect to the technical requirement of wireless local area network (WLAN).

This thesis is focused on three topics, which correspond to three major issues in the research of LDPC codes: code characterization with girth degree distribution, low encoding complexity with structured construction, and higher decoding convergence with two-stage decoding scheme.

In the first part of the thesis, a novel concept of girth degree is introduced. This concept combines the idea of the classical concept of girth with node degree. The proposed concept is used to characterize the codes and measure their performance. A simple tree-based search algorithm is applied to detect and count the girth degree. The proposed concept is more effective than the classical concept of girth in measuring the performance. It shows that the girth degree plays more significant role than the girth it self, in determining the code performance. Furthermore, the existence of short-four-cycles to some extent is not harmful to degrade the code performances.

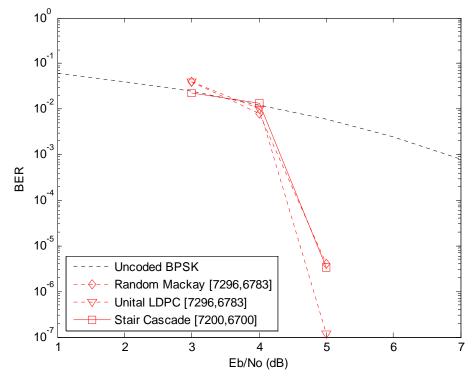

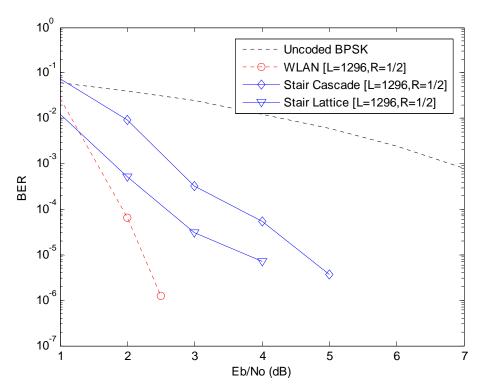

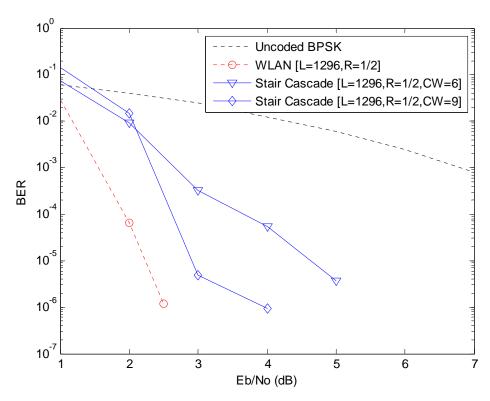

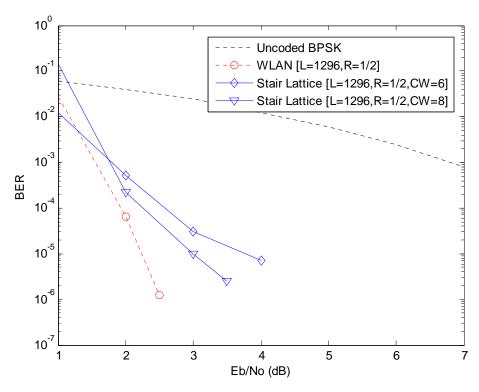

The second part deals with a simple method for constructing a class of LDPC codes, which pose relative low encoding complexity but show good performance. The combination of the stair structure and the permutation matrices, which are constructed based on the proposed method, yields very simple implementation in encoding process within encoder. The resulting encoder can be implemented using relatively simple shift-register circuits. Their performance is comparable with that of irregular MacKay codes. In short code length, they outperform some well-established structured codes. The performance of the proposed codes is comparable with the optional LDPC codes for WLAN at higher code rates. However, the proposed codes are relatively suboptimal at lower code rate. Such performance is achieved by the proposed codes in lower encoding complexity

In the third part, a method for enhancing the decoding convergence for high coded modulation system is introduced. The two-stage decoding scheme is proposed to improve bit reliabilities in decoding process leading to reduced decoding iteration without performance losses. This is achieved by making use of the output from the first decoding stage as the additional input for the second decoding stage. The optimal combination of the maximal iteration of both decoding stages is capable of reducing the average iteration. This method shows its efficiency at the waterfall region of signal-to-noise-ratio.

#### KURZFASSUNG

Seit ihrer Wiederentdeckung haben die Low Density Parity Check (LDPC) Codes ein hohes Interesse erfahren, da sie mit niedrigem Aufwand für die Dekodierung fast die Kanalkapazität erreichen. Daher sind sie ein vielversprechendes Kanalcodierungsschema für zukünftige drahtlose Anwendungen. Sie weisen allerdings noch den Nachteil eines hohen Enkodierungsaufwandes auf. Die Einwicklung eines mit geringem Aufwand implementierbaren LDPC Codes mit guten Leistungen stellt noch eine große Herausforderung dar. Die Nutzbarkeit der potenziellen Eigenschaften von LDPC-Codes im Bezug auf die technischen Randbedingungen gerade bei drahtlosen lokalen Netzwerken (Wireess Local Area Network - WLAN) wirft dabei besonders interessante Fragestellungen auf.

Die vorliegende Dissertation konzentriert sich auf drei große Themen bezüglich der Erforschung von LDPC Codes, nämlich die Charakterisierung des Codes mittels Umfangsmaßverteilung (Girth Degree Distribution), den niedrigen Enkodierungsaufwand mittels strukturierter Codekonstruktion sowie die verbesserte Decodierungskonvergenz mittels eines Zwei-Phasen Dekodierungsverfahrens.

Im ersten Teil der Dissertation wird ein neues Konzept zur Beurteilung von Codes eingeführt. Es basiert auf der Umfangsmaßverteilung. Dieses Konzept kombiniert die Ideen des klassischen Konzeptes - basierend auf dem Umfang (Girth) - mit denen des Knotenmaßes (Node Degree) und wird zur Charakterisierung und zur Abschätzung der Leistungsfähigkeit des Codes eingesetzt. Zur Erkennung und Berechnung des Umfangs wird ein einfacher, baumbasierter Suchalgorithmus eingeführt. Dieses Konzept ermöglicht eine effizientere Leistungsabschätzung als das der alleinigen Verwendung des Umfangs. Es wird gezeigt, dass das Umfangsmaß bei der Ermittlung der Leistung des Codes eine wesentlich größere Rolle spielt als der Umfang. Im Rahmen dieser Untersuchungen fällt als weiteres Ergebnis an, dass die Existenz von kurzen Schleifen der Länge 4 die Leistungsfähigkeit des Codes nicht beeinträchtigt.

Der zweite Teil der Dissertation beschäftigt sich mit einem einfachen Verfahren für die Konstruktion einer Gruppe von LDPC Codes, die bei einem relativ niedrigen Enkodierungsaufwand dennoch eine gute Leistung aufweist. Die Kombination einer Treppestruktur in Verbindung mit Permutationsmatrizen führt zu einer sehr einfachen Implementierung, ohne dass ein erheblicher Leistungsverlust auftritt. Der resultierende Enkodierer kann ausschließlich mit einer sehr einfachen Schaltung aus Schieberegistern implementiert werden. Die Leistungsfähigkeit des entstehenden Codes ist mit der des unregelmäßigen MacKay-Codes vergleichbar. In kurzer Kodelänge übertreffen sie sogar einige bekannte strukturierte Codes. Allerdings sind die vorgeschlagenen Codes suboptimal im Vergleich mit den optionalen LDPC Codes für WLAN, sofern niedrige Coderaten betrachtet werden. Sie erweisen sich aber als ebenbürtig bei höheren Coderaten. Diese Leistungsfähigkeit wird von den hier vorgeschlagenen Codes mit relativ niedrigem Enkodierungsaufwand erreicht.

Letztendlich wird im dritten Teil der Dissertation ist ein Verfahren zur Steigerung der Decodierungskonvergenz beim Einsatz von LDPC Codes in Kombination mit Modulationsverfahren hoher Wertigkeit vorgestellt. Das Zwei-Phasen Dekodierverfahren wird zur Verbesserung der Bit-Zuverlässigkeit im Dekodierungsprozess eingeführt. Dieses bewirkt eine Reduktion der benötigten Dekodierungsschritte ohne Leistungsverlust. Erreicht wird dies durch die Verwendung der Ergebnisse einer ersten Dekodierungsphase als erneute Eingabe für eine zweite Dekodierungsphase. Die optimale Kombination der durchzuführenden Iterationen beider Dekodierungsphasen kann die Anzahl der insgesamt benötigten Iteration im Durchschnitt reduzieren. Dieses Verfahren zeigt seine Wirksamkeit im Wasserfallbereich des Signal-Rausch-Verhältnisses.

## **CONTENTS**

| ACKNOWLEDGMENT                     | j       |

|------------------------------------|---------|

| ABSTRACT                           |         |

| KURZFASSUNG                        | V       |

| CONTENTS                           | vii     |

| LIST OF FIGURES                    |         |

| LIST OF TABLES                     |         |

| LIST OF PUBLICATIONS               | XV      |

|                                    |         |

| CHAPTER 1                          |         |

| INTRODUCTION                       |         |

| 1.1 Motivation                     |         |

| 1.2 Historical Review              |         |

| 1.2.1 Channel Coding               |         |

| 1.2.2 LDPC Coding                  |         |

| 1.3. Thesis Organization           | 5       |

|                                    |         |

| CHAPTER 2                          |         |

| BASIC THEORY                       |         |

| 2.1 Communication System           |         |

| 2.2 Channel Coding                 |         |

| 2.3 LDPC Codes                     |         |

| 2.3.1 Description                  |         |

| 2.3.2 Code Construction            |         |

| 2.3.3 Encoding                     | 14      |

| 2.3.4 Decoding                     | 16      |

| 2.4 Wireless LAN                   | 20      |

|                                    |         |

| CHAPTER 3                          |         |

| GIRTH DEGREE FOR CODE EVALUATION   | 25      |

| 3.1 Background                     | 25      |

| 3.2 Concept of Girth Degree        |         |

| 3.3 Simulation Results             | 32      |

| 3.4 Conclusion                     | 54      |

| CHAPTER 4                          |         |

| CODE CONSTRUCTION WITH STAIR STRUC | TURE 57 |

| 4.1 Background                     |         |

| 4.2 Code Structure                 | 58      |

#### CONTENTS

| 4.3 Construction Methods                   | 62    |

|--------------------------------------------|-------|

| 4.3.1 Slopes Method                        | 62    |

| 4.3.2 Girth Degree Detection Method        |       |

| 4.4 Encoder/Decoder Design                 | 65    |

| 4.4.1 Encoder Design                       | 65    |

| 4.4.2 Decoder Design                       | 71    |

| 4.5 Simulation Results                     |       |

| 4.6 Conclusion                             | 108   |

| CHAPTER 5                                  |       |

| TWO-STAGE DECODING FOR ITERATION REDUCTION | N 111 |

| 5.1 Background                             | 111   |

| 5.2 Concept and Methods                    | 111   |

| 5.3 Simulation Results                     | 115   |

| 5.3.1 Two feedback parameters              | 117   |

| 5.3.2 Generality of Two-stage decoding     | 120   |

| 5.4 Conclusion                             | 129   |

| CHAPTER 6                                  |       |

| CONCLUSION                                 | 131   |

| 6.1 Thesis contribution                    | 133   |

| 6.2 Future Work                            | 133   |

| ABBREVIATIONS                              |       |

| REFERENCESAPPENDIX                         |       |

| <u> </u>                                   |       |

# Chapter 2

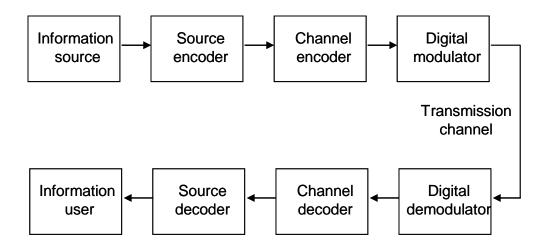

| Figure 2.1 General block diagram of coded systems for digital communications          | 7       |

|---------------------------------------------------------------------------------------|---------|

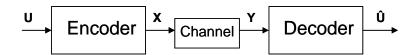

| Figure 2.2 A simplified model of channel coding system                                |         |

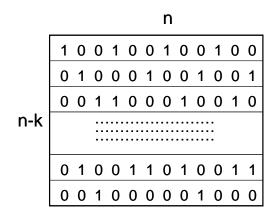

| Figure 2.3 Parity check matrix H of an LDPC code                                      |         |

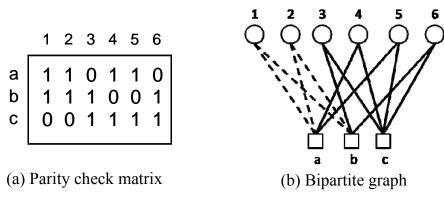

| Figure 2.4 Representation of LDPC codes                                               |         |

| Figure 2.5 Triangular parity-check matrix of MacKay (a) and Richardson (b)            |         |

| Figure 2.6 Message passing decoder of LDPC codes                                      |         |

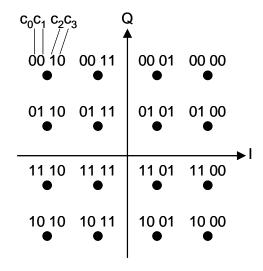

| Figure 2.7 Signal constellation for 16-QAM with Gray labelling                        |         |

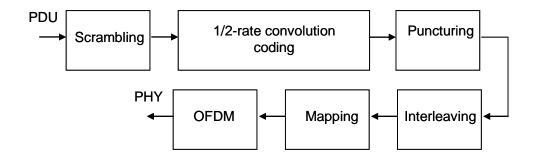

| Figure 2.8 IEEE 802.11a transmitter PHY layer                                         |         |

| Chapter 3                                                                             |         |

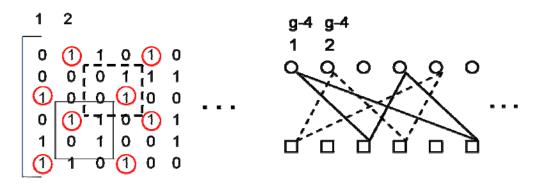

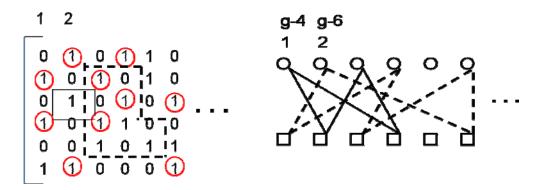

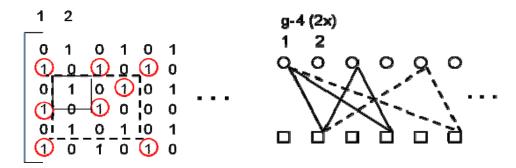

| Figure 3.1 Example for homogeneous local girth                                        | 26      |

| Figure 3.2 Example for heterogeneous local girth                                      |         |

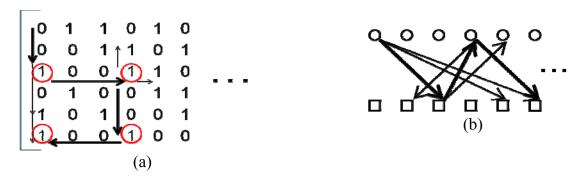

| Figure 3.3 Two of six cycles of girth of four passing through the variable node 1     |         |

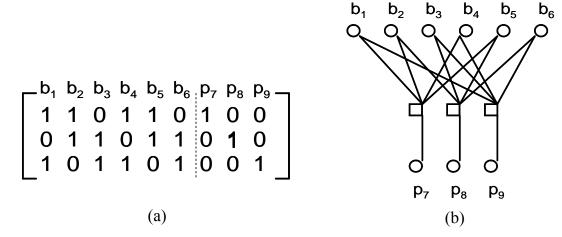

| Figure 3.4 An example of girth detection process in a parity check matrix (a) and a   |         |

| bipartite graph (b)                                                                   | 30      |

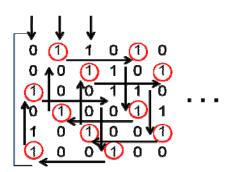

| Figure 3.5 An example of girth degree counting process for girth of four              | 31      |

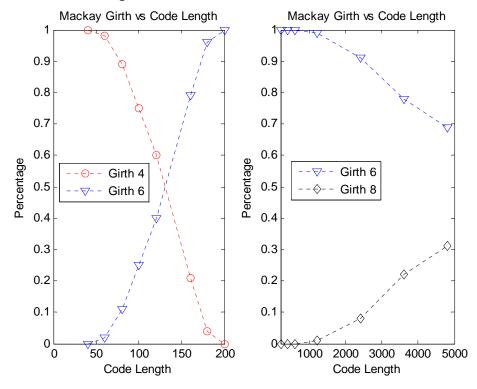

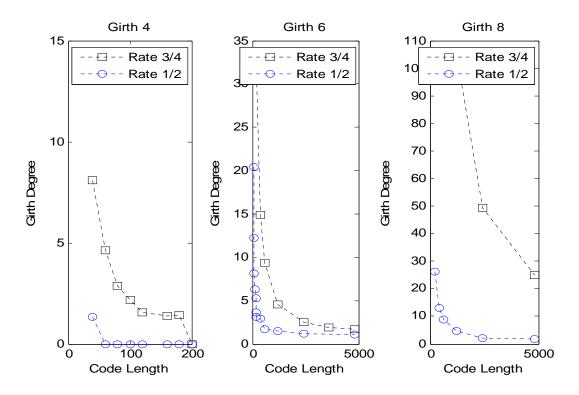

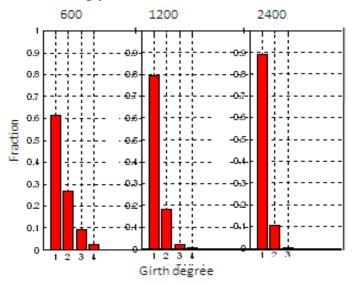

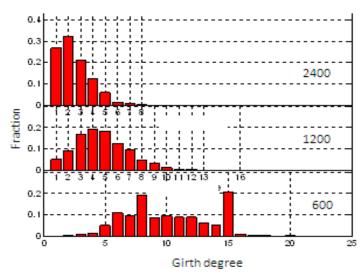

| Figure 3.6 Girth distribution of MacKay code at code rate 3/4 as function of code len | ngth 32 |

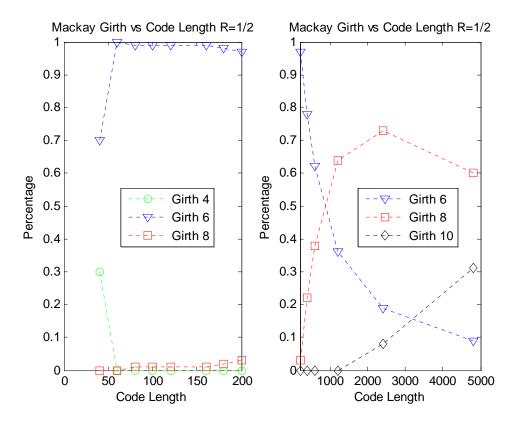

| Figure 3.7 Girth distribution of MacKay code at code rate 1/2 as function of code len | ngth 33 |

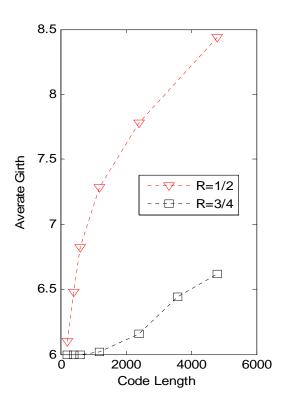

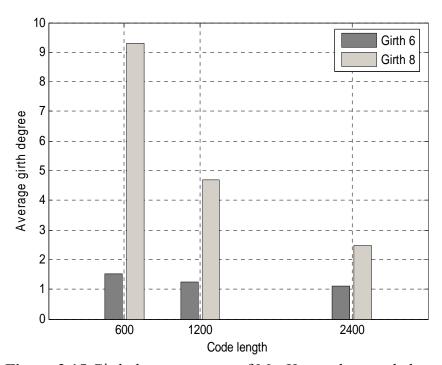

| Figure 3.8 Impact of code length on the average girth at different code rate          | 34      |

| Figure 3.9 Impact of code rate on average girth degree in different code rate         | 35      |

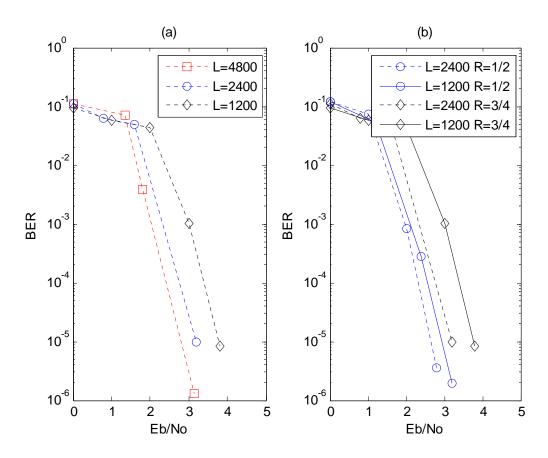

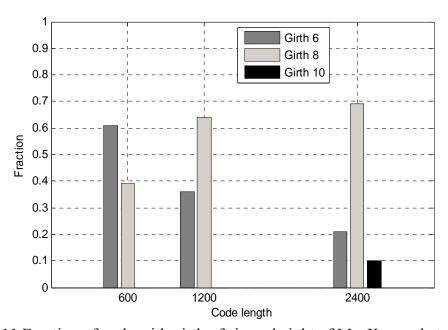

| Figure 3.10 Performance of MacKay code in different code length (a) and code rate     | (b)36   |

| Figure 3.11 Fraction of node with girth of six and eight of MacKay code to code len   | gth37   |

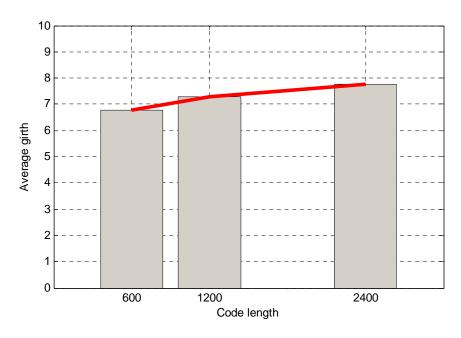

| Figure 3.12 Average girth of MacKay code to code length                               | 38      |

| Figure 3.13 Girth degree distribution of girth 6 of MacKay code                       | 39      |

| Figure 3.14 Girth degree distribution of girth-8 of MacKay code                       | 39      |

| Figure 3.15 Girth degree average of MacKay code to code length                        | 40      |

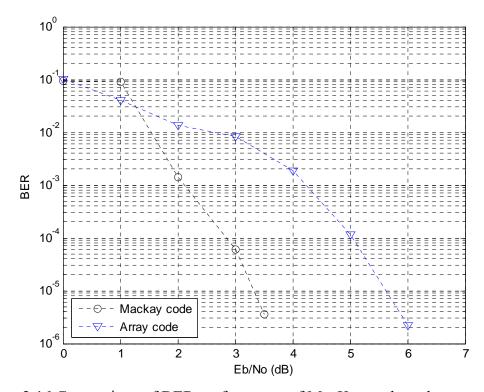

| Figure 3.16 Comparison of BER performance of MacKay code and array code with          |         |

| column weight 3 at code length 1,200 bits and code rate 1/2                           | 42      |

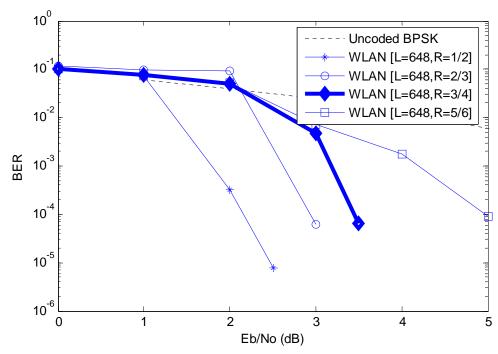

| Figure 3.17 Code performance of the 648-length WLAN codes at different code rate      | s43     |

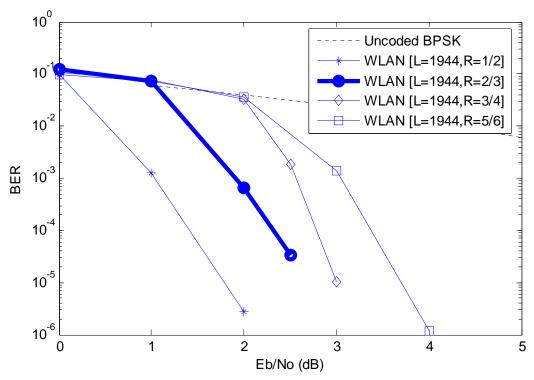

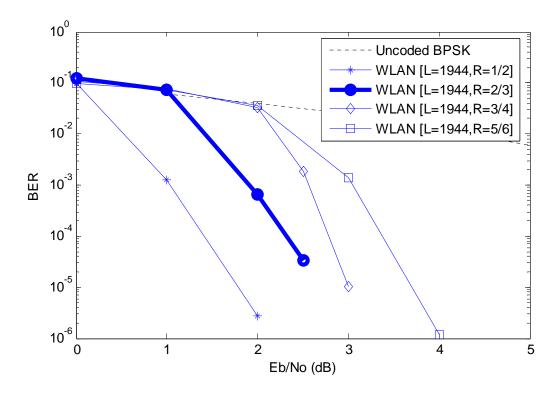

| Figure 3.18 Code performance of the 1296-length WLAN codes at different code rat      | tes46   |

| Figure 3.19 Code performance of the 1944-length WLAN codes at different code rat      | tes48   |

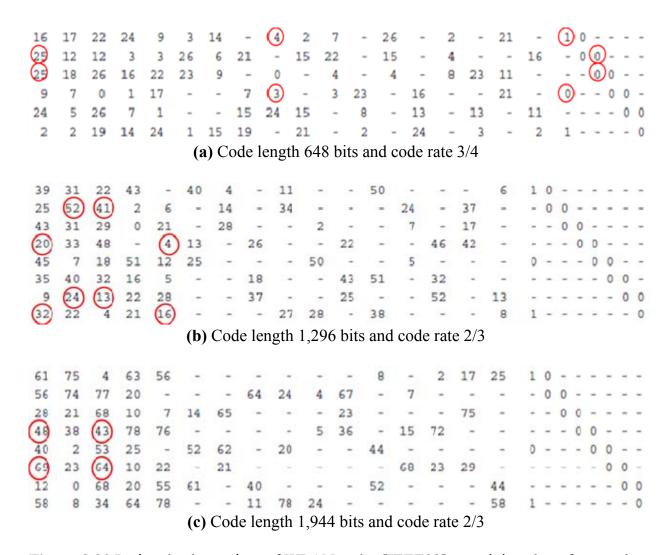

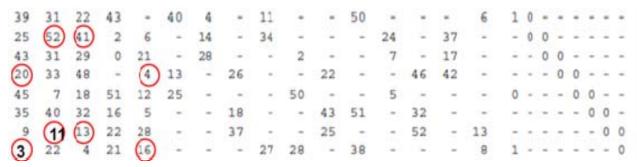

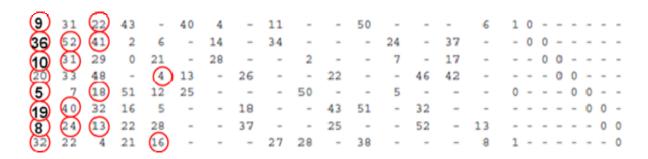

| Figure 3.20 Parity check matrices of WLAN codes [IEEE09] containing short-four-of-    | cycles  |

|                                                                                       | 51      |

| Figure 3.21 Modified parity check matrix of IEEE802.11n codes without short-four-     | cycles  |

|                                                                                       | 52      |

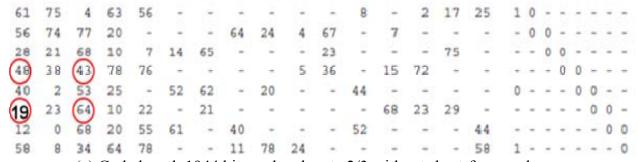

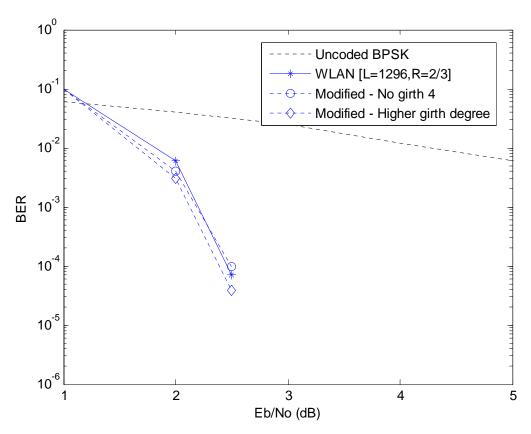

| Figure 3.22 Comparison of the WLAN codes with and without the short-four-cycles. Figure 3.23 Modified parity check matrix of WLAN codes (code length 1296 bits an rate 2/3) with higher short-four-cycles | d code        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Figure 3.24 Impact of girth degree on BER performance of the length-1944, rate-2/3                                                                                                                        |               |

| inguite 5.24 impact of girli degree on BER performance of the length 1544, rate 2/5                                                                                                                       |               |

|                                                                                                                                                                                                           |               |

| Chapter 4                                                                                                                                                                                                 |               |

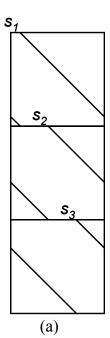

| Figure 4.1 LDPC staircase codes: parity-check matrix (a) and its corresponding graph                                                                                                                      |               |

| Figure 4.2 An identity matrix (a) and a singular cyclic shift submatrix (b)                                                                                                                               |               |

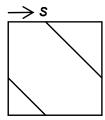

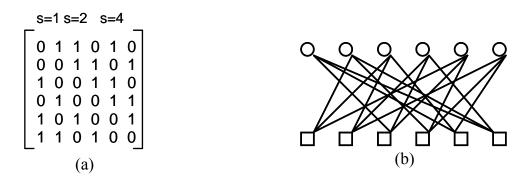

| Figure 4.3 Submatrix with cyclic right-shifted slope <i>s</i>                                                                                                                                             | 59            |

| Figure 4.4 Submatrix (a) with its corresponding graph (b)                                                                                                                                                 | 59            |

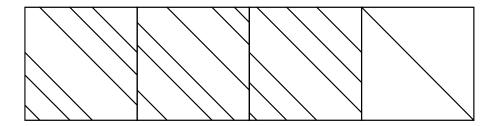

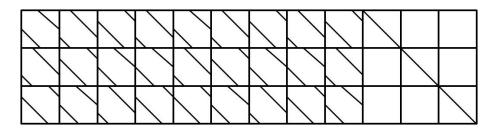

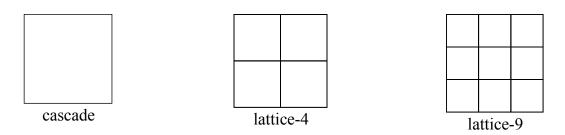

| Figure 4.5 Cascade structure: parity check matrix                                                                                                                                                         |               |

| Figure 4.6 Lattice structure: parity check matrix                                                                                                                                                         |               |

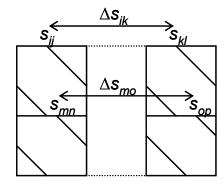

| Figure 4.7 Cascade and lattice submatrices                                                                                                                                                                | 62            |

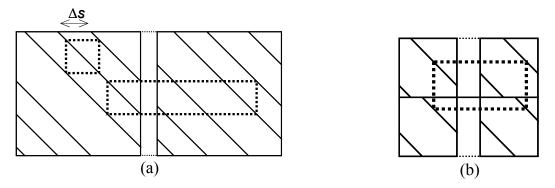

| Figure 4.8 Presence of four-cycles in the cascade (a) and lattice structure (b)                                                                                                                           | 62            |

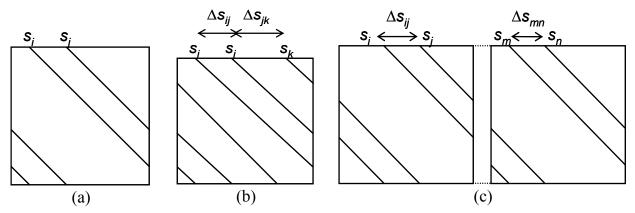

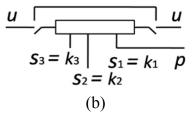

| Figure 4.9 Parameters in the slope method.                                                                                                                                                                | 63            |

| Figure 4.10 A pair of slope distance                                                                                                                                                                      |               |

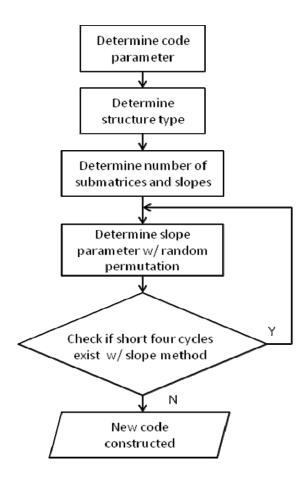

| Figure 4.11 Algorithm of code construction with slope method                                                                                                                                              |               |

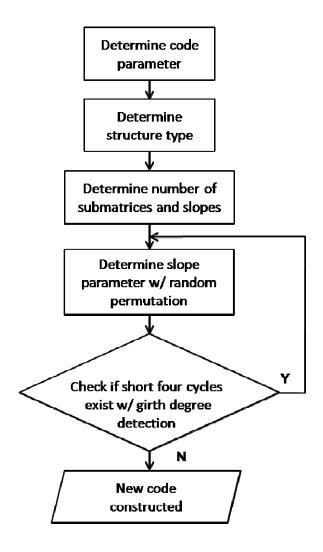

| Figure 4.12 Algorithm of code construction with girth degree detection method                                                                                                                             |               |

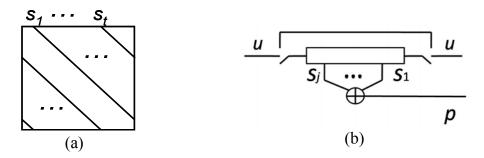

| Figure 4.13 Submatrix                                                                                                                                                                                     |               |

| Figure 4.14 Cascade structure: submatrix (a) and its cyclic-shift register (b)                                                                                                                            |               |

| Figure 4.15 Implementation of the encoder of cascade structure                                                                                                                                            |               |

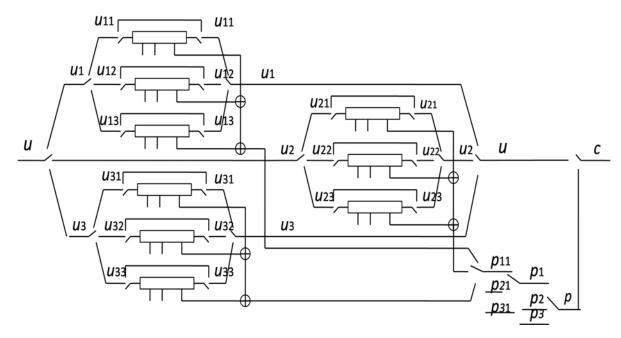

| Figure 4.16 Lattice structure: submatrices (a)                                                                                                                                                            |               |

| Figure 4.17 Implementation of the encoder of lattice structure                                                                                                                                            |               |

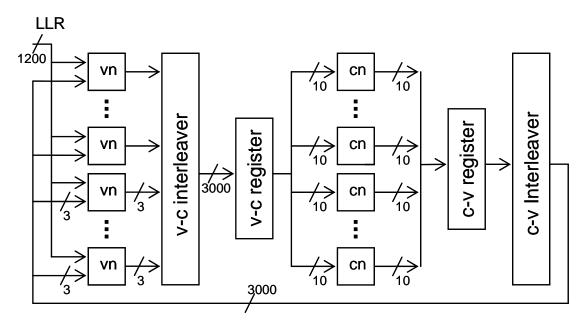

| Figure 4.18 Block diagram of the decoder                                                                                                                                                                  |               |

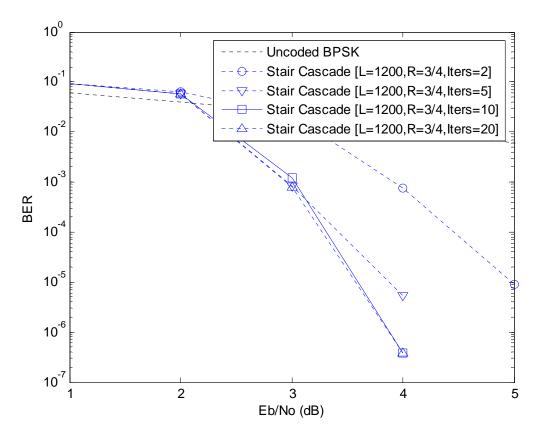

| Figure 4.19 Impact of decoding iteration on the performance of the length-1200, rate                                                                                                                      |               |

| Stair Cascade code                                                                                                                                                                                        |               |

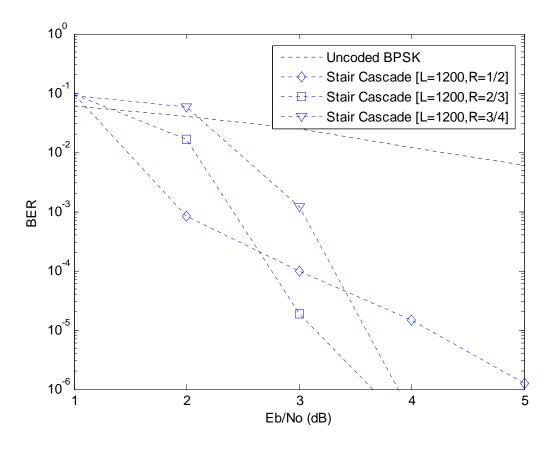

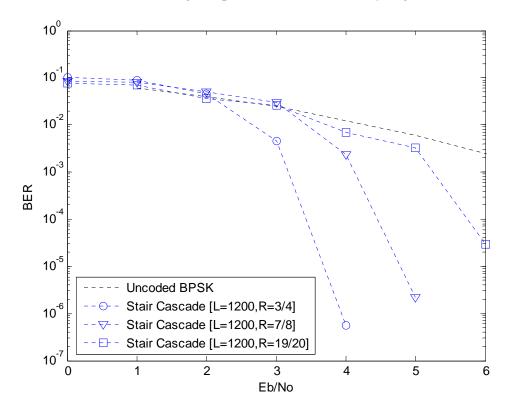

| Figure 4.20 Performance of Stair Cascade codes with code length 1,200 bits at differ                                                                                                                      |               |

| code rates                                                                                                                                                                                                |               |

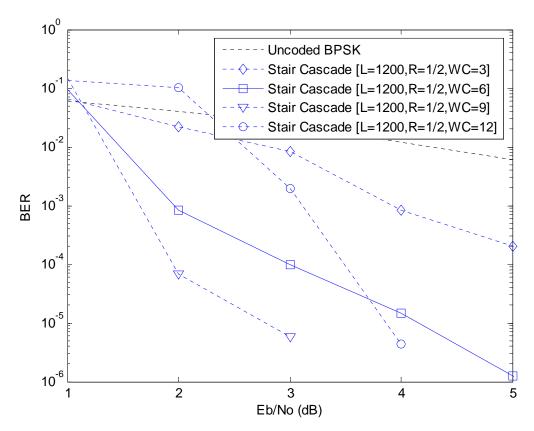

| length 1,200 bits at code rate 1/2                                                                                                                                                                        |               |

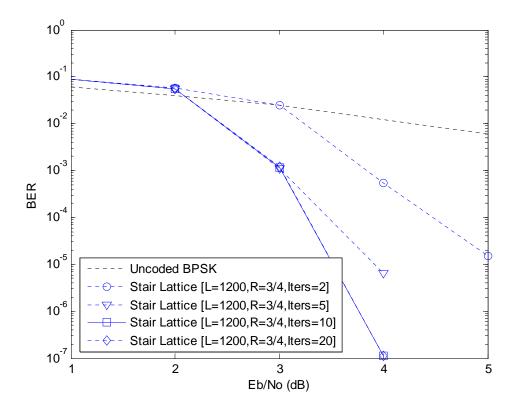

| Figure 4.22 Impact of column weight on the performance of Stair Cascade codes with                                                                                                                        | /0<br>h.code  |

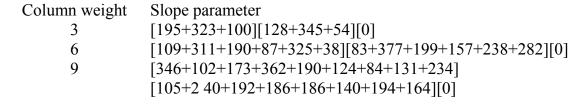

| length 1,200 bits at code rate 2/3                                                                                                                                                                        | 11 code<br>77 |

| Figure 4.23 Impact of column weight on the performance of Stair Cascade codes with                                                                                                                        |               |

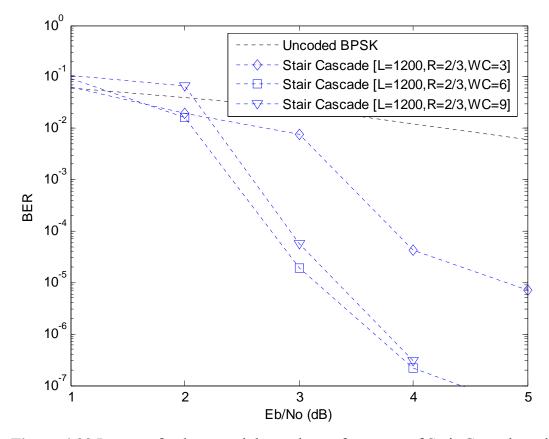

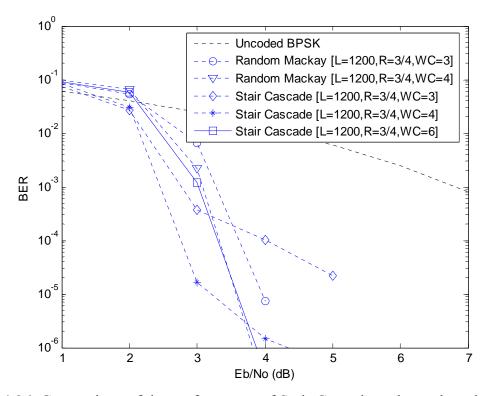

| length 1,200 bits at code rate 3/4                                                                                                                                                                        |               |

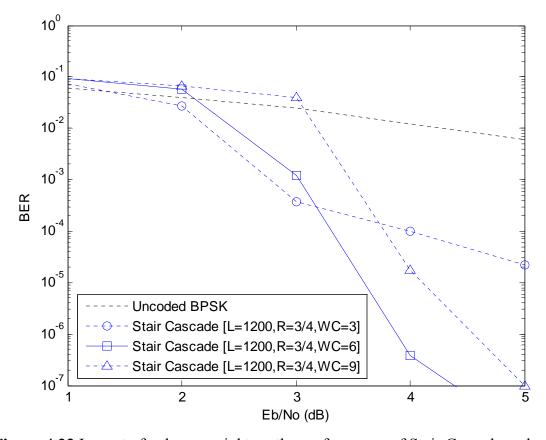

| Figure 4.24 Impact of decoding iteration on the performance of the length-1200, rate                                                                                                                      | -3/4          |

| Stair Lattice code                                                                                                                                                                                        |               |

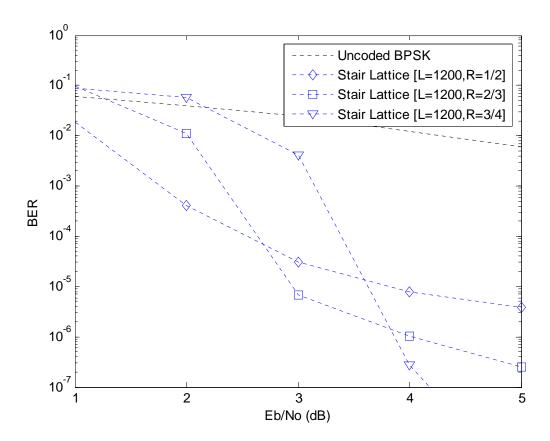

| Figure 4.25 Performance of Stair Lattice codes with code length 1,200 bits at different                                                                                                                   |               |

| code rates                                                                                                                                                                                                |               |

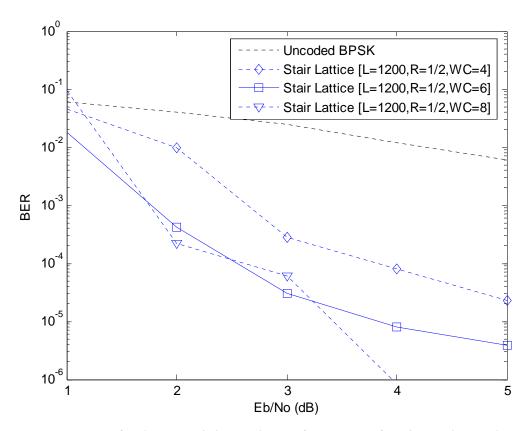

| Figure 4.26 Impact of column weight on the performance of Stair Lattice codes with                                                                                                                        |               |

| length 1,200 bits at code rate 1/2                                                                                                                                                                        |               |

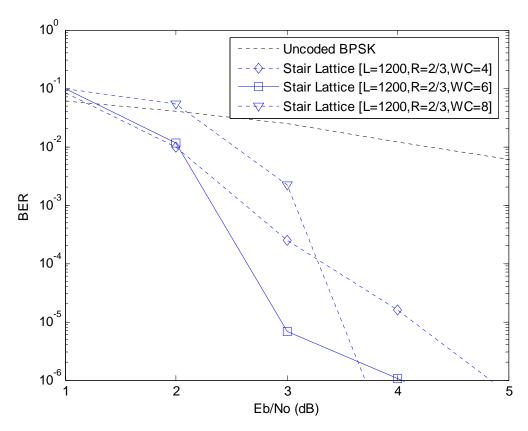

| Figure 4.27 Impact of column weight on the performance of Stair Lattice codes with code                                    |     |

|----------------------------------------------------------------------------------------------------------------------------|-----|

| length 1,200 bits at code rate 3/4                                                                                         | 33  |

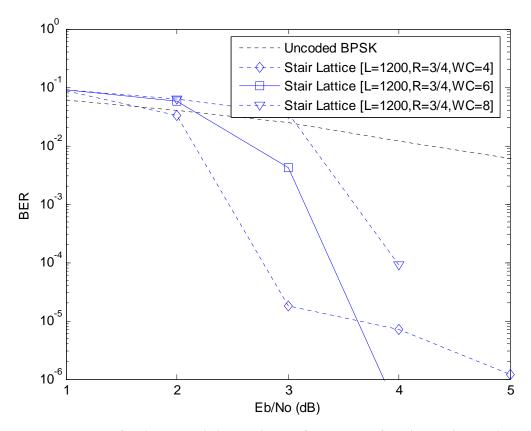

| Figure 4.28 Impact of column weight on the performance of Stair Lattice codes with code length 1,200 bits at code rate 3/4 |     |

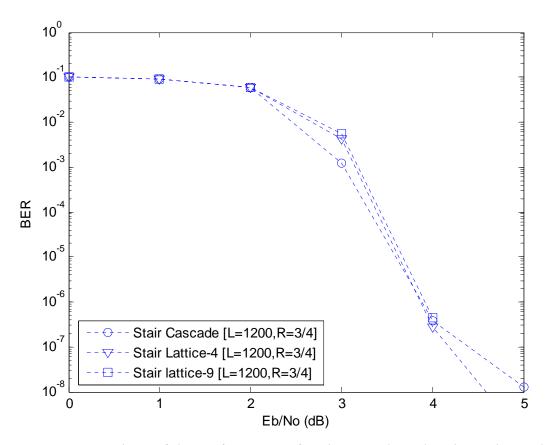

| Figure 4.29 Comparison of the performance of Stair Cascade and Stair Lattice codes with                                    |     |

| code length 1,200 bits and code rate 3/4                                                                                   |     |

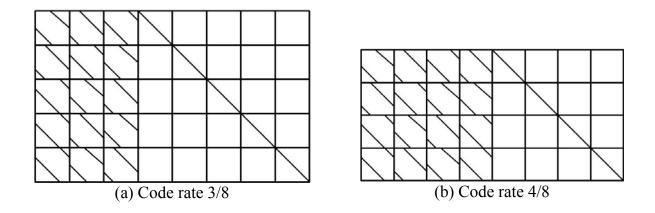

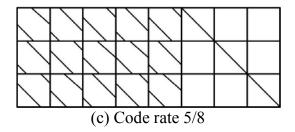

| Figure 4.30 Structure of parity check matrices of Stair Lattice codes with different code                                  | 30  |

| rates                                                                                                                      | 27  |

| Figure 4.31 Performance of the length-1,200 Stair Latice codes at specific code rates                                      |     |

| Figure 4.32 Performance of Stair Cascade codes at high code rate                                                           |     |

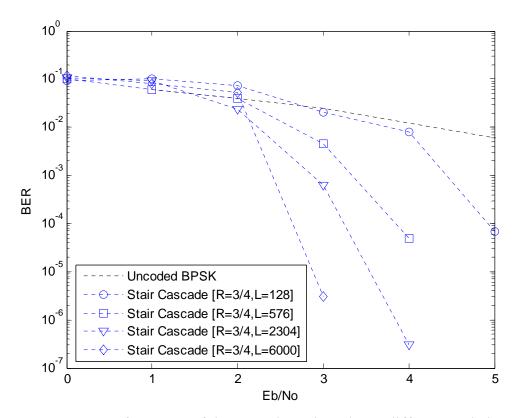

| Figure 4.33 Performance of the rate-3/4 Stair codes at different code length                                               |     |

| · ·                                                                                                                        |     |

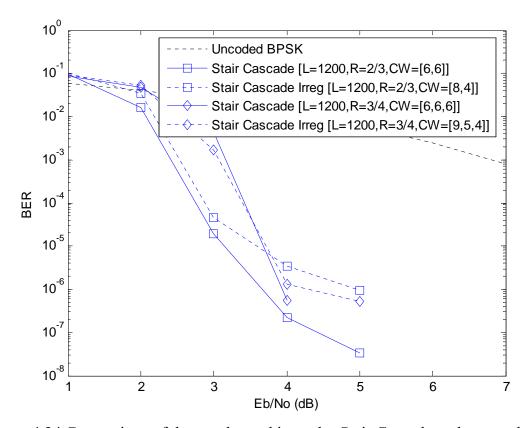

| Figure 4.34 Comparison of the regular and irregular Stair Cascade codes at code length                                     |     |

| 1,200 bits and code rate 2/3 and 3/4                                                                                       |     |

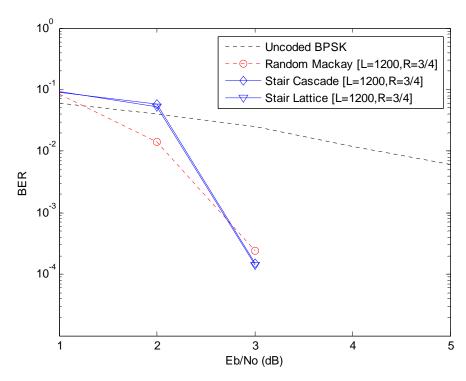

| Figure 4.35 Comparison of the BER performance of Stair Codes with MacKay Codes                                             |     |

| Figure 4.36 Comparison of the performance of Stair Cascade codes and random MacKay                                         |     |

| code at code length 1,200 bits, code rate 3/4.                                                                             |     |

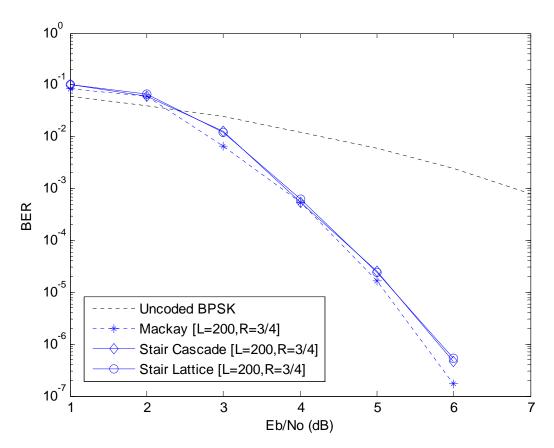

| Figure 4.37 Comparison of Stair codes with MacKay code at code rate 200 and code rate                                      |     |

| 3/4                                                                                                                        |     |

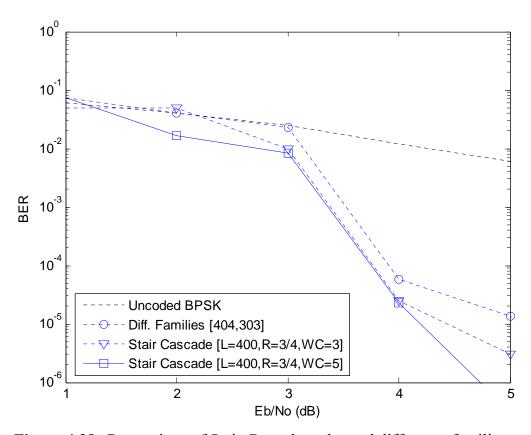

| Figure 4.38 Comparison of Stair Cascade codes and difference families code                                                 |     |

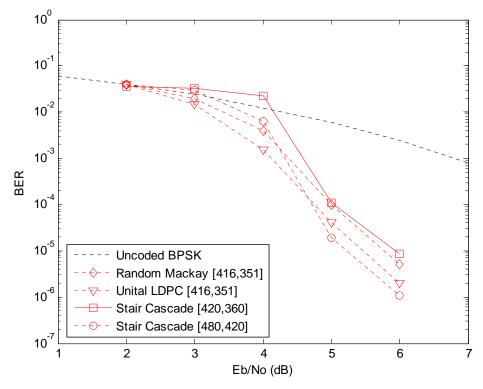

| Figure 4.39 BER performance of high-rate short-length LDPC codes on AWGN channel                                           |     |

| with a maximum iteration 10                                                                                                | 96  |

| Figure 4.40 BER performance of high-rate long-length LDPC codes on AWGN channel                                            | 07  |

| with a maximum iteration 10                                                                                                | 97  |

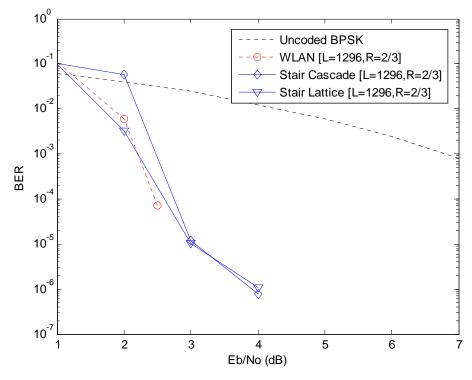

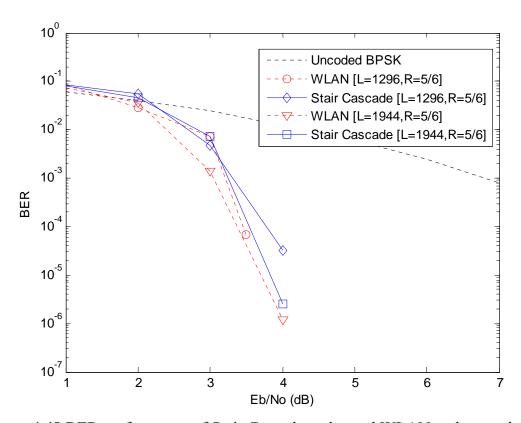

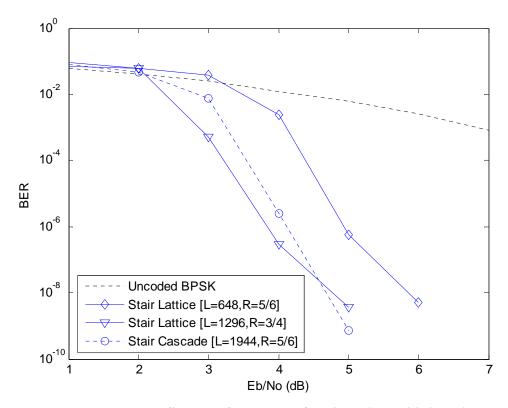

| Figure 4.41 BER performance of Stair codes and WLAN code at code length 1,296 bits                                         | ^^  |

|                                                                                                                            | 98  |

| Figure 4.42 BER performance of the improved Stair Cascade codes and WLAN code at                                           | ~ ~ |

|                                                                                                                            | 99  |

| Figure 4.43 BER performance of the improved Stair Lattice codes and WLAN code at                                           |     |

| code length 1,296 bits and code rate 1/2                                                                                   | )() |

| Figure 4.44 BER performance of Stair codes and WLAN code at code length 1,296 bits                                         |     |

| and code rate 2/3                                                                                                          | 00  |

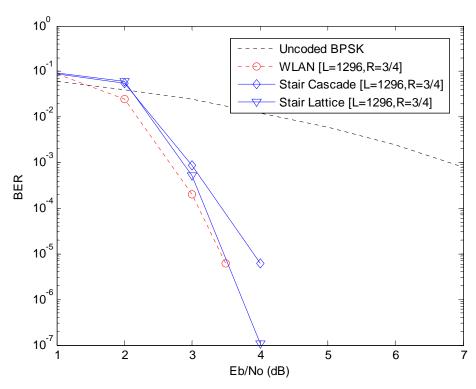

| Figure 4.45 BER performance of Stair codes and WLAN code at code length 1,296 bits                                         |     |

| and code rate 3/410                                                                                                        | 01  |

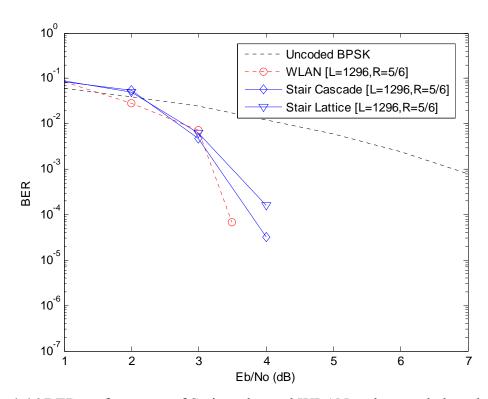

| Figure 4.46 BER performance of Stair codes and WLAN code at code length 1,296 bits                                         |     |

| and code rate 5/610                                                                                                        | 02  |

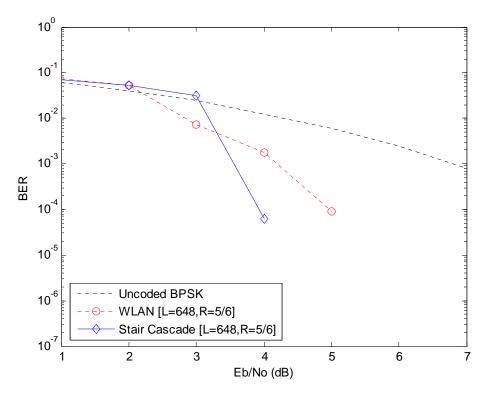

| Figure 4.47 BER performance of Stair codes and WLAN code at code length 648 bits and                                       |     |

| code rate 5/6                                                                                                              | 03  |

| Figure 4.48 BER performance of Stair Cascade codes and WLAN code at code length                                            |     |

| 1,296 bits and 1,944 bits and code rate 5/6                                                                                |     |

| Figure 4.49 Error-floor performance of Stair codes at high code rate                                                       |     |

| Figure 4.50 Impact of girth degree of four cycles on BER performance of the length-1,29                                    |     |

| rate-1/2 Stair Cascade codes                                                                                               |     |

| Figure 4.51 Impact of girth degree of four cycles on BER performance of the length-1,29                                    | 6,  |

|                                                                                                                            | 07  |

# Chapter 5

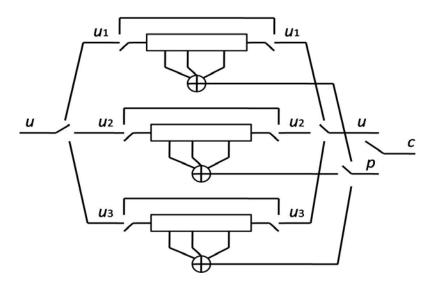

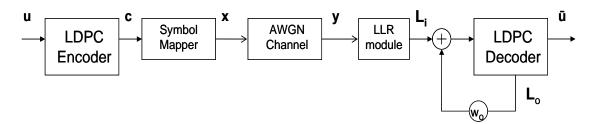

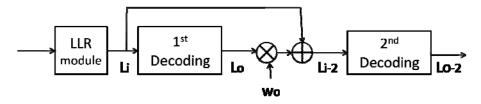

| Figure 5.1 Scheme of the two-stage decoding                                        | 112      |

|------------------------------------------------------------------------------------|----------|

| Figure 5.2 Two-stage decoding in LDPC decoder                                      | 113      |

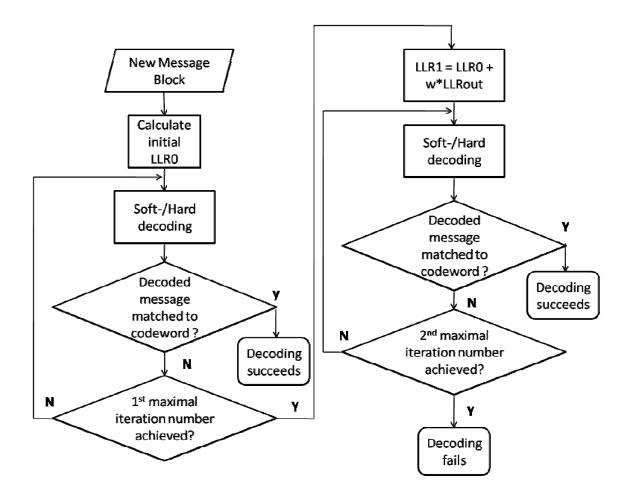

| Figure 5.3 Flow diagram of two-stage decoding algorithm                            | 113      |

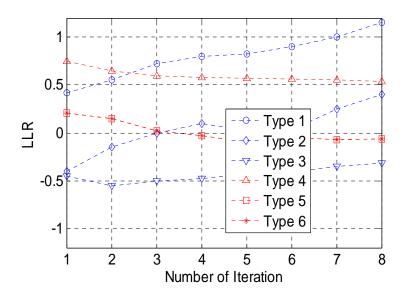

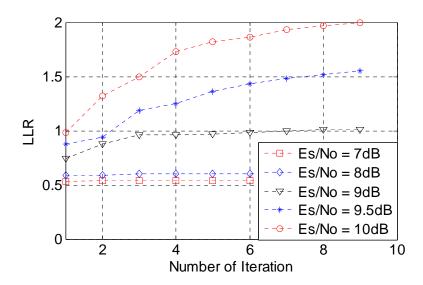

| Figure 5.4 Typical development of LLRs at the waterfall region                     | 114      |

| Figure 5.5 Development of LLRs depending on SNR                                    | 115      |

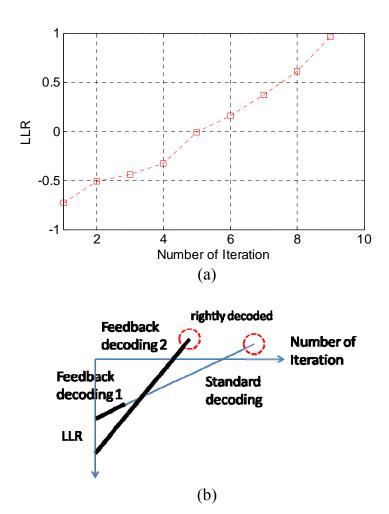

| Figure 5.6 Development of LLR of bit subject to fail decoded in generic decoding   | (a) and  |

| its model denoting decoding improvement using feedback decoding                    | 116      |

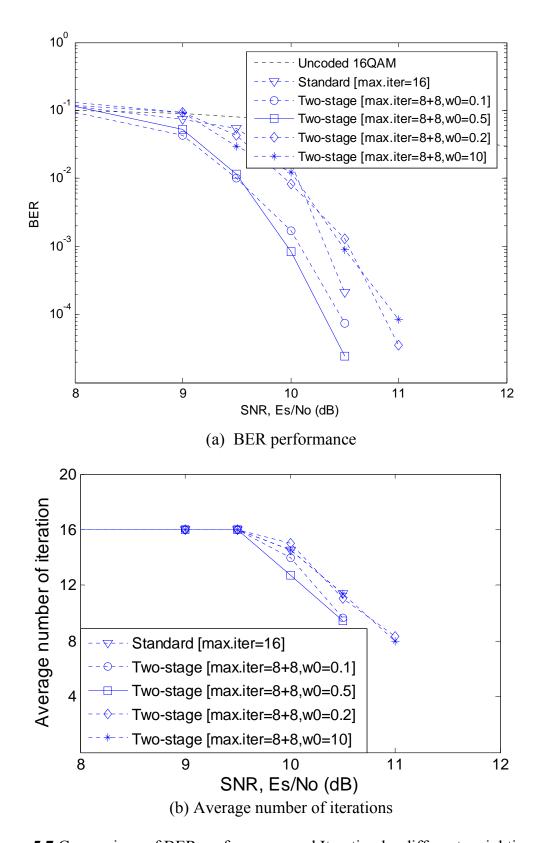

| Figure 5.7 Comparison of BER performance and Iteration by different weighting fa   | actor.   |

|                                                                                    | 118      |

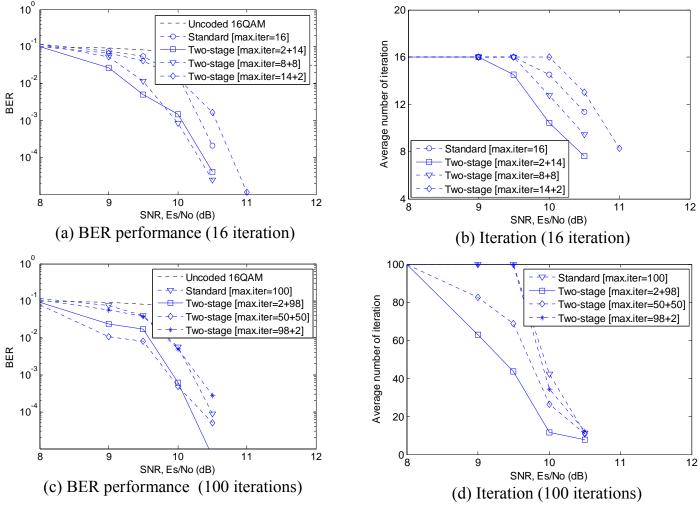

| Figure 5.8 Comparison of BER performance and iteration number by different         |          |

| combination of iteration numbers                                                   | 119      |

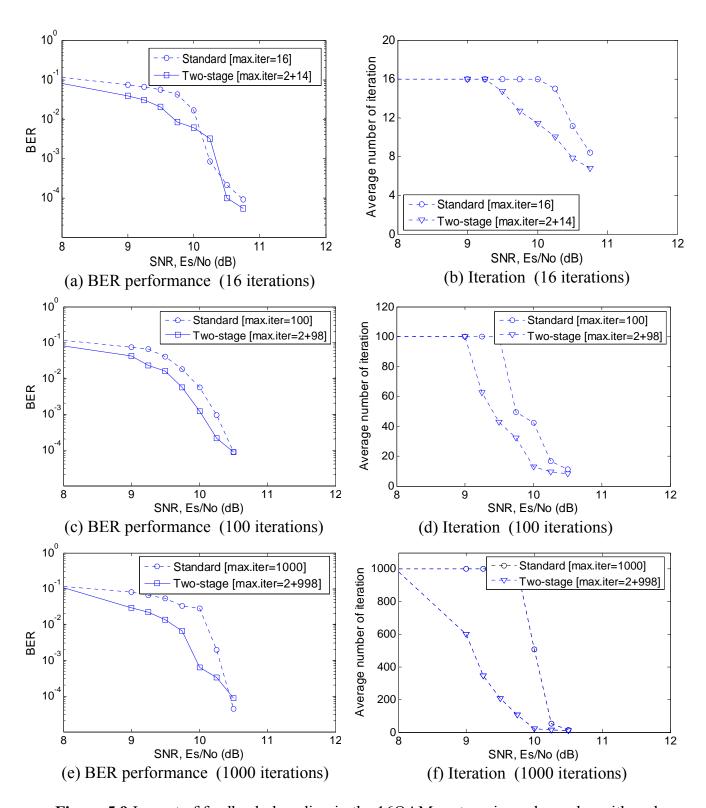

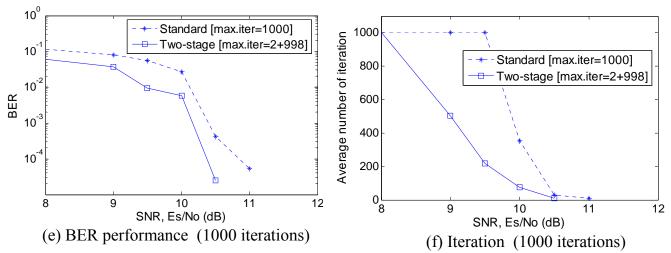

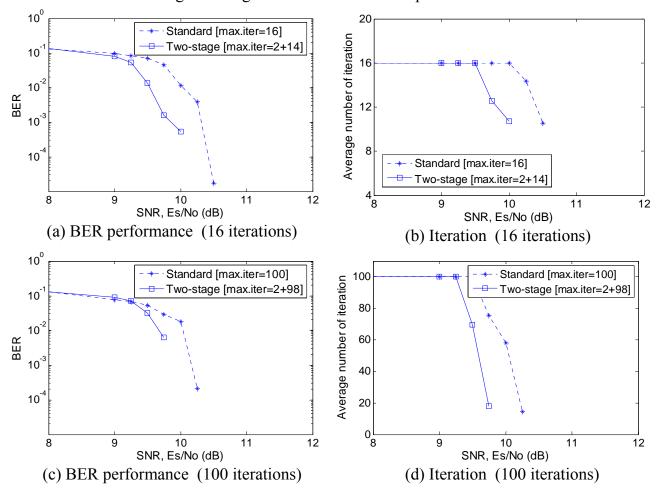

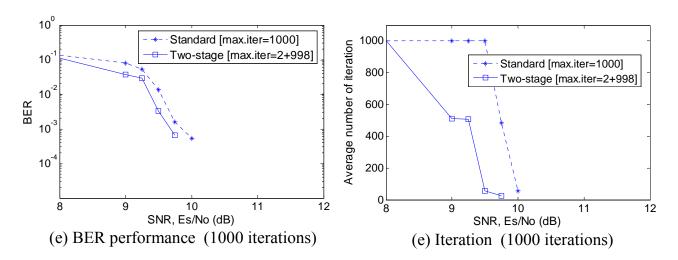

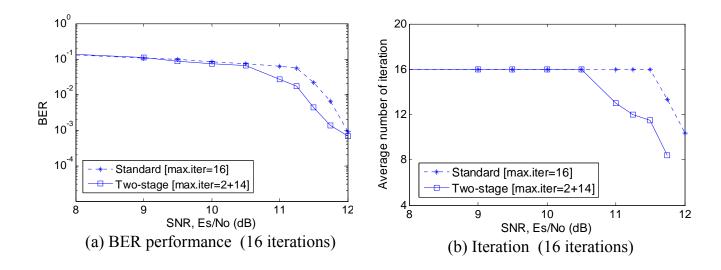

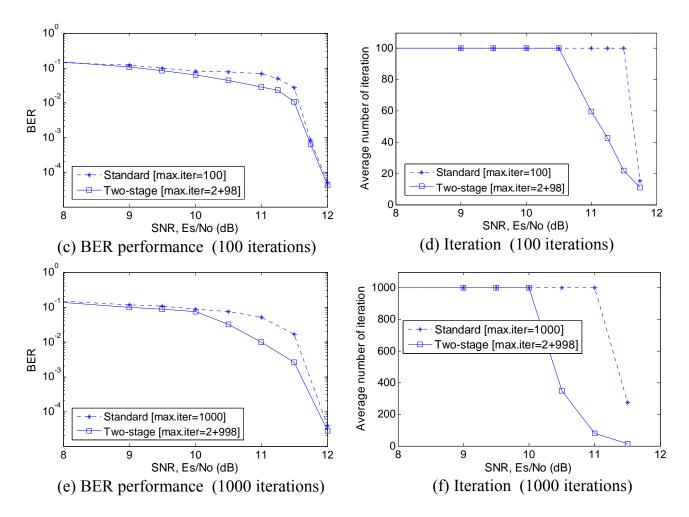

| Figure 5.9 Impact of feedback decoding in the 16QAM system, irregular codes wit    | h code   |

| length 1,200 bits on BER performance and average number of iterations              | 121      |

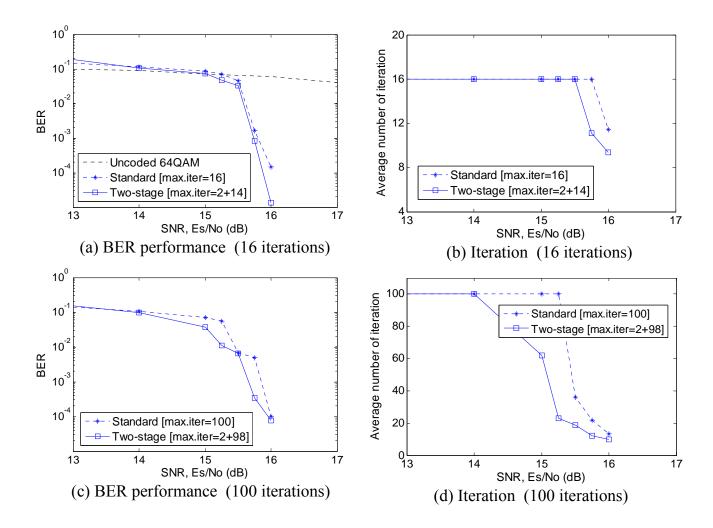

| Figure 5.10 Impact of feedback decoding in the 64QAM system, irregular codes with  | ith code |

| length 1,200 bits on BER performance and average number of iterations              | 123      |

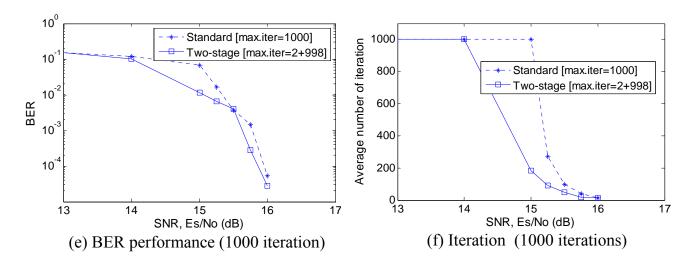

| Figure 5.11 Impact of feedback decoding in the 16QAM system, irregular codes with  | ith code |

| length 600 bits on BER performance and average number of iterations                | 124      |

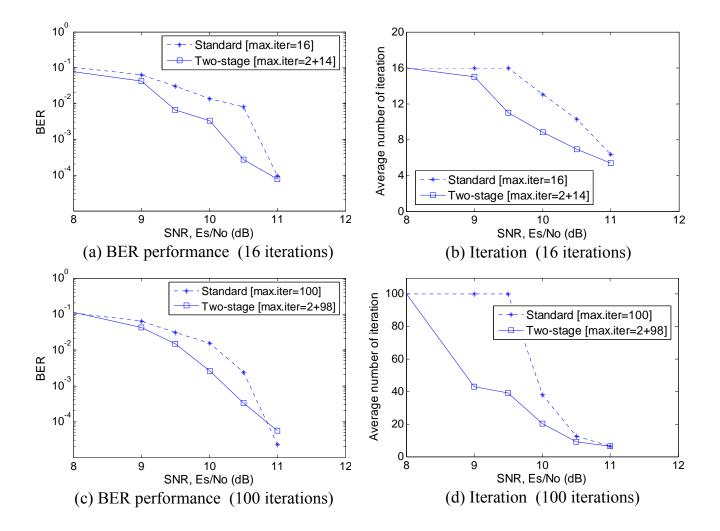

| Figure 5.12 impact of feedback decoding in the 16QAM system, irregular codes with  | ith code |

| length 2,400 bits on BER performance and average number of iterations              | 125      |

| Figure 5.13 Impact of feedback decoding in the 16QAM system, array codes with a    | code     |

| length 1,200 bits on BER performance and average number of iterations              | 126      |

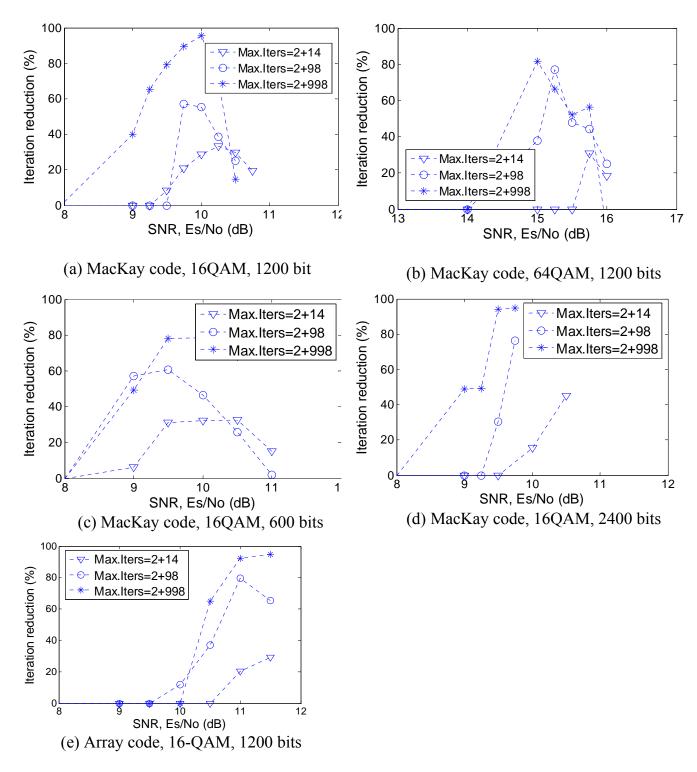

| Figure 5.14 Impact of the two-stage decoding on the reduction of iteration numbers | s for    |

| different condition                                                                | 127      |

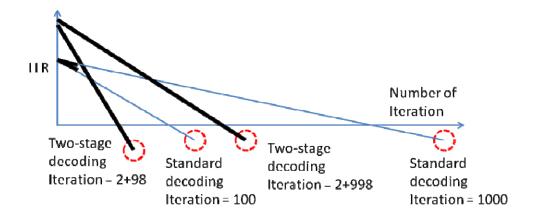

| Figure 5.15 Model of LLR development during iterations for low and high number     | s of     |

| decoding iterations                                                                | 128      |

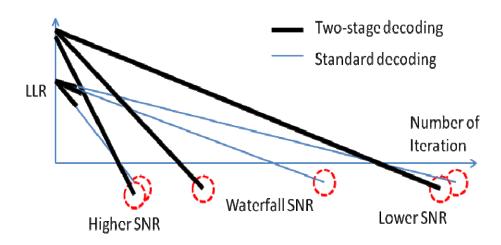

| Figure 5.16 Model of the LLR development during iterations under influence of SN   | √R129    |

|                                                                                    |          |

# LIST OF TABLES

# Chapter 2

| Table 2.1 Mode-dependent parameters                                                            | 21 |

|------------------------------------------------------------------------------------------------|----|

| Table 2.2 OFDM parameters                                                                      |    |

| Table 2.3 Channel models                                                                       | 22 |

| Table 2.4 Rate-dependent parameter of LDPC codes in the IEEE 802.11n Standard                  | 23 |

| Table 2.5 MCS parameters in the IEEE 802.11n Standard                                          |    |

| Chapter 3                                                                                      |    |

| Table 3.1 Code length and girth distribution of MacKay code                                    | 38 |

| Table 3.2 Girth degree distribution of MacKay code                                             |    |

| Table 3.3 Average girth degree of the smallest girth of of MacKay code                         | 40 |

| Table 3.4 Code length and girth distribution of Array code                                     |    |

| Table 3.5 Girth degree distribution of array codes of the smallest girth of array codes        |    |

| Table 3.6 Average girth degree of the smallest girth of array codes                            |    |

| Table 3.7 Girth distribution of WLAN codes (code length = 648 bits)                            |    |

| Table 3.8 Girth degree distribution of WLAN codes (code length = 648 bits)                     |    |

| Table 3.9 Average girth degree of WLAN codes (code length = 648 bits)                          |    |

| Table 3.10 Average girth degree distribution of WLAN codes (code length = $648$ bits).         |    |

| Table 3.11 Girth distribution of WLAN codes (code length = 1,296 bits)                         |    |

| Table 3.12 Girth degree distribution of WLAN codes (code length = 1,296 bits)                  |    |

| Table 3.13 Average girth degree of WLAN codes (code length = 1,296 bits)                       |    |

| Table 3.14 Average girth degree distribution of WLAN codes (code length = 1,296 bits           | _  |

| Table 3.15 Girth distribution of WLAN codes (code length = 1,944 bits)                         |    |

| Table 3.16 Girth degree distribution of WLAN codes (code length = 1,944 bits)                  |    |

| Table 3.17 Average girth degree of WLAN codes (code length = 1,944 bits)                       |    |

| Table 3.18 Average girth degree distribution of WLAN codes (code length = 1,944 bits           |    |

| Table 3.19 Average girth distribution of WLAN codes having girth 4                             |    |

| Table 3.20 Girth condition of WLAN codes in comparison                                         | 50 |

| Chapter 4                                                                                      |    |

| Tabel 4.1 Number of equation $(N_{eq})$ depending on number of slopes per submatrix $(N_{sl})$ | 70 |

| Tabel 4.2 Number of equation $(N_{eq})$ for number of submatrix $(N_{sm})$                     |    |

| Tabel 4.3 Comparison of both structures in number of equation per code rate                    | 71 |

| Tabel 4.4 Comparison of both structures in number of submatrix per code rate                   |    |

## LIST OF PUBLICATIONS

- 1. Deny Hamdani, Wolfgang Endemann, Ruediger Kays. *A Class of LDPC Codes with Very Efficient Encoder*. International Conference on Electrical Engineering and Informatics (ICEEI2007), 17-19 June 2007, Bandung, Indonesia.

- 2. Deny Hamdani, Wolfgang Endemann, Ruediger Kays. *Measuring Performance of LDPC Codes with Girth Degree*. International Conference on Electrical Engineering and Informatics (ICEEI2007), 17-19 June 2007, Bandung, Indonesia.

- 3. Deny Hamdani, Wolfgang Endemann, Ruediger Kays. *Enhancing Performance of High-Order Modulation with LDPC Codes using Feedback Mechanism*. International Conference on Electrical Engineering and Informatics (ICEEI2007), 17-19 June 2007, Bandung, Indonesia.

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Motivation

Mobile computing has been of great interest within information and communication communities due to its tremendous growing resulting in a continuous influx of mobile devices supporting modern human life-style in the last decades. The indispensable growth in mobile computing is boosted by rapid development in device technology, affordable prices and increasing mobility requirement. Wireless local area networks (WLAN) in form of ad-hoc networks became the key technology in wireless networking of mobile computing. The high-speed WLAN standardized in IEEE 802.11 was introduced to cope with the development in area of mobile networking.

At the beginning of their development, the IEEE 802.11 wireless standards incorporated a well-known convolutional code and the Viterbi algorithm as error correcting channel code. At the time of the development of the standards this was the most practical solution considering cost, complexity, power consumption, and decoding latency. Unfortunately, convolutional codes and the Viterbi algorithm show inferior performance with respect to the theoretical capacity limits.

To cope with these problems, it would have been possible to introduce Turbo codes to the WLAN scheme. Although being capable of coming reasonably close to theoretical capacity, Turbo were not applied to WLAN due to their performance degradation for short blocks as well as their high decoding complexity. This fact led to the introduction of another family of forward-error-correcting codes known as Low Density Parity Check (LDPC) codes. By utilizing their advantageous very sparse matrix characteristics, a significant improvement over the current coding system can be reasonably realized. LDPC codes have been proven to outperform Turbo codes [RU03] and make reliable communication in vicinity of the Shannon limit possible [Chun01]. Although a scheme of LDPC codes has been officially incorporated in the recent WLAN Standard IEEE 802.11n [IEEE09], it is always of challenging interest to elaborate and explore this rediscovered coding technique for improving the performance of WLAN system.

This thesis deals with the investigation of LDPC codes as an efficient and reliable channel coding technique, which best fit to the wireless channel within WLAN systems. Some constraints concerning the environment and the application in WLAN shall be taken into account, such as limited processing capability, limited battery power, small physical form, demanded Quality of Service (QoS), and harmonious coexistence with other systems working in the neighbored bands. A significant drawback of LDPC codes in their encoding complexity has been the focus of this research to cope with aforementioned requirement.

#### 1.2 Historical Review

#### 1.2.1 Channel Coding

The history of channel coding could be dated back to 1948 as Claude Shannon published his seminal paper, *A Mathematical Theory of Communication* [Shan48]. He proved that reliable communication can be established over a noisy channel using channel codes provided that the information rate is not exceeding the so-called capacity of the channel. He derived the limit of the information rate over a noisy channel and presented channel codes with very long block length and optimal decoding that can achieve reliable communication. However, his approach is practically prohibitive due to expensive realization of both encoding and decoding.

The introduction of Shannon's noisy coding theorem has been sparking the research in field of coding theory. Practical capacity-achieving schemes found large interest within the coding community. Over four decades after Shannon's publication, none of a large number of proposed coding systems could approach Shannon's theoretical limit. The breakthrough just came in the early of 90's with the discovery of turbo codes [BGT93]. Thanks to their pseudorandom interleaver and iterative decoding algorithm, turbo codes could operate near Shannon's capacity limit with reasonable decoding complexity. The discovery of turbo codes sparked the research interest in the field of codes on graphs and iterative decoding. This fact led to the next breakthrough in 1995, that is, the rediscovery of LDPC codes [KN95], which was firstly invented in 1962 by Gallager [Gall62] and unfortunately, ignored thereafter. The main reason was that the state-of-the-art hardware technology considered the realization of LDPC codes as impractical at that time.

In principal, the construction techniques of channel codes are based on algebraic approach and convolutional approach. Further category of channel codes is derived from the combination of both approaches. Therefore, based on their construction technique, the channel codes can be classified into three categories [Li02]. The first category of channel codes is block codes based on algebraic approach. This codes includes Hamming codes introduced by Hamming in 1950 [Hamm50], BCH codes by Hocquenhem in 1959 [Hocq59] and independently by Bose and Ray-Chaudhuri in 1960 [BC60] and RS codes by Reed and Solomon in 1960 [RS60]. Those codes are practical in hardware implementation. However, there was no comfortable soft decoding algorithm. Furthermore, those codes are not flexible in code lengths.

The second category of channel codes is convolutional codes which were firstly introduced by Elias in 1955 [Elia55]. These codes are decoded by trellis decoding. They operate on serial data and are usually described by their code rate and constraint length. More powerful codes can be produced by longer constraint length, however, at cost of exponentially increased maximum likelihood decoding complexity. Unlike block codes, it is convenient to change code lengths of convolutional codes. The technique of puncturing keeps the flexibility of convolutional codes in code rate without extra complexity. They have efficient soft decoding algorithms, such as soft-output Viterbi algorithm [HH89] and a posteriori probability algorithm [BCJR74], which are of great advantages on fading

channels. As an alternative, convolutional codes can be decoded by trellis decoding introduced by Ungerboeck [Unge82].

The third category of channel codes is the compound codes which combine block and convolutional codes. They use iterative decoding. The discovery of this code is dated back to 1966 as Forney [Forn66] concatenated an inner code and an outer code. This construction makes the codes to have error probability that decreases exponentially at rate less than capacity, while decoding complexity increases only algebraically. The development of these codes was accelerated by the discovery of turbo codes by Berrou, Glavieux, and Thitimajshima in 1993 [BGT93] and the rediscovery of LDPC codes by MacKay and Neal in 1995 [KN95]. Their impressive near-capacity performance lead to the introduction of other concatenated codes providing similar coding gains, such as parallel concatenated convolutional codes [BM96], serial concatenated convolutional codes [BMDP96] and hybrid concatenated convolutional codes [DP97]. Further codes includes turbo product codes [Elia54, CT94], regular/irregular repeat-accumulate codes [DJE98], and product accumulate codes [LNG01a]. These codes have common features including the application of a (random) interleaver and decoding techniques.

The milestones of history of coding theory can be summarized as follows

- 1948 Shannon's channel coding theorem [Shan48]

- 1950 Hamming codes [Hamm50]

- 1955 Convolutional codes [Elia55]

- 1959/60 BCH codes [Hocq59, BC60], RS codes [RS60]

- LDPC codes [Gall62], rediscovered in 1995 [KN95]

- 1982 Trellis-coded modulation [Unge82]

- 1993 Turbo codes [BGT93]

## 1.2.2 LDPC Coding

The history of LDPC coding began in the early 1960s when Gallager [Gall62, Gall63] introduced a channel coding scheme providing the structural basis for codes with near-shannon-limit performance. Gallager's codes applied iterative decoding based on message-passing decoding algorithms. However, such decoding demanded very intensive computation, which could not be supported by the existing hardware technology at that time. Hence, Gallager's codes were considered as impractical to be implemented as channel codes. It was about four decades later when LDPC codes were rediscovered in the mid 1990s as MacKay [KN95] realized the immense potential of the codes due to their near-Shannon limit performance.

Before the rediscovery of LDPC codes took place, a small number of researchers worked with Gallager's codes during the few decades after the first publication of Gallager's codes, including Zyablov and Pinsker [ZP75] and Margulis [Marg82]. In the early 1980s, Tanner [Tann81] provided a graphical representation of LDPC codes and other coding schemes. Tanner suggested the employment of a recursive approach for the construction of LDPC codes and presented a graph representation of the parity check

matrix of LDPC codes. In the same work, Tanner also introduced the min-sum decoding algorithm.

In the early 1990s, channel coding research was sparked by the introduction of Turbo codes which have shown the impressive near-shannon limit performance with relative lower complexity. The application of iterative decoding in Turbo codes's scheme has accelerated the research of iterative decoding techniques leading to revisiting the work of Gallager. However, in their initial development, Turbo codes were not considered in connection with graphical representations. The iterative decoding techniques used for decoding turbo codes have been linked by McEliece *et al.* [EKC98] to the principles of belief propagation described by Pearl [Pear88], which was the basis of the decoding techniques proposed by Gallager.

The work of Tanner and its developments by Wiberg et al. [Wibe94, WKL95, Wibe96] provided the basis for the factor graph representation of codes in common use recently. These graphs have been further highlighted by Kschischang et al [KFL98]. The further usage of the graphs led Sipser and Spielman [SS96] to introduce LDPC codes whose parity check matrix is based on expander graphs. The common interest in the algorithms used for iterative decoding in the artificial intelligence community has led MacKay and Neal [KN95] in the mid 1990s to the rediscovery of LDPC codes.

Since then, the research of LDPC codes has been focusing on the improvements of the code performance. The general approach has been to modify the graph describing the code. The performance of LDPC codes in the case of very long block sizes (around 10<sup>5</sup> to 10<sup>7</sup> bits) has outperformed Turbo codes and approached the Shannon bound to within hundredths of decibel. Such techniques and their performance gains have been demonstrated by Sipser and Spielman [SS96], Richardson *et al.* [RSU00, RSU01] and Luby *et al.* [LMSSS97, LMSS98, LSMS01]. Chung *et al.* [CFRU01] showed that the threshold for a code rate 1/2 on the AWGN channel is within 0.0045 dB of the Shannon limit. Their simulation resulted within 0.04 dB of the Shannon limit at a bit error rate of 10<sup>-6</sup> using a block length of 10<sup>7</sup> bits.

In coding research community, LDPC codes have been studied extensively in many aspects. Richardson *et al.* [RU01a] proposed the density evolution algorithm to calculate the asymptotic performance of a given LDPC code over AWGN channel. Chung *et al.* [Chun00, CRU01] simplified the complex density evolution algorithm using Gaussian Approximation. The bounds of code rate and performance of LDPC codes were studied by Burshtein *et al.* in [BKLM02, Burs02, MiB01]. MacKay *et al.* [KN97, KN99] simulated LDPC codes at high block length and illustrated that LDPC codes are capable of outperforming the turbo codes when communicating over AWGN channel.

LDPC codes using higher decoding Galois field were also proposed by Davey *et al.* [DK98, DK99, Dave99], Song *et al.* [SC03] and Nakamura *et al.* [NKS01]. Lentmaier [Lent97] proposed the generalized LDPC codes by replacing the rows in the parity check matrix of LDPC codes with a Hamming code and this also attracted the interest from Zhang *et al.* [ZP01a, ZP01b], Hirst *et al.* [HH02a, HH02b] and Boutros *et al.* [BPZ99]. LDPC codes using higher decoding Galois field were also proposed by Davey *et al.* [DK98, DK99, Dave99], Song *et al.* [SC03] and Nakamura *et al.* [NKS01]. Lentmaier [Lent97] proposed the generalized LDPC codes by replacing the rows in the parity check

matrix of LDPC codes with a Hamming code and this also attracted the interest from Zhang et al. [ZP01a, ZP01b], Hirst et al. [HH02a, HH02b] and Boutros et al. [BPZ99].

Motivated by their outstanding performance, LDPC codes have been studied in many other channels and employed with various modulation scheme. The performance of LDPC codes over Rayleigh fading channel [HSM01, LWN02], Rician channel [LZW04], Nakagami channel [MMØ02], Gilbert-Elliot channel [EKP03], Lorentzian channel [STC00], partial-response channel [LNG01b] and binary erasure channel [NF04] are evaluated. LDPC codes are elaborated for some communication scheme, such as OFDM scheme [FO01, SNG03], MIMO scheme [BKA04], CDMA scheme [SKP00]. The elaboration of LDPC codes within bandwidth efficient coded modulation schemes are studied in [EO01, HSMP03]. In addition to exploring the performance issues, some researchers are trying to reduce the complexity of encoding and decoding of LDPC codes such as Richardson *et al.* [RU01a, RU01b], Kou *et al.* [KLF00, KLF01], Spielman [Spiel96] and Pothier *et al.* [PBB99].

The research of LDPC codes leads to the design of their derivatives as Tornado [BLMR98], LT [Luby02], and Raptor [Shok03], which were protected by patents.

The milestones of LDPC coding research can be summarized as follows

- 1948 Shannon Limit [Shan48]

- 1962 Invention of LDPC codes [Gall62]

- 1975 Quantification of LDPC codes complexity [ZP75]

- 1981 Graph representation on LDPC codes parity check matrix [Tann81]

- 1995 Rediscovery of near Shannon-limit performance of LDPC codes [KN95]

- 1998 Irregular LDPC codes [LMSS98]

- 2001 World record-breaking LDPC codes performance [CFRU01]

## 1.3. Thesis Organization

The thesis is structured as follows.

In Chapter 1 the introduction to this work, including motivation of the research, historical review of LDPC codes, and the organization of the thesis, is given.

In Chapter 2 some basic concepts for theoretical basis of the research, including transmission system, channel coding, LDPC codes, coded modulation and wireless LAN, are discussed.

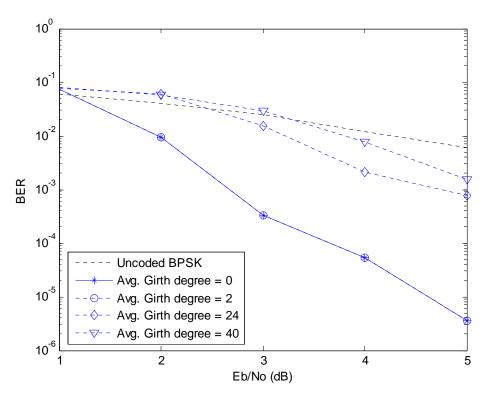

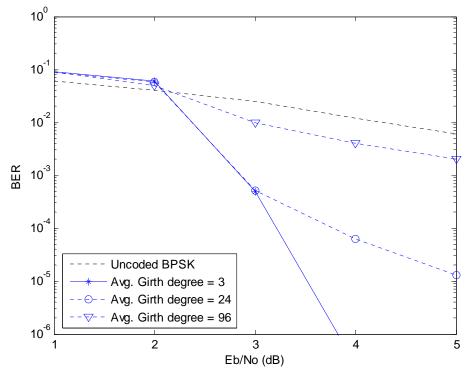

In Chapter 3 the thesis introduces the concept of girth degree that can be considered an extension of the concept of girth in the theory of LDPC codes. The concept is used to characterize LDPC codes and also to explore the role of girth in determining the performance of LDPC codes. Girth detection and girth degree counting algorithms are introduced. Some LDPC codes are characterized and evaluated using this concept. It is of great interest that the existence of short-four-cycles is realized within some optional LDPC codes in Standard IEEE 802.11n, which in fact suffer from no performance degradation.

In Chapter 4 the thesis discusses a simple method for code construction using the stair structure to reduce encoding complexity, which is one of the drawbacks of LDPC codes.

The proposed codes are based on permutation submatrices in cascade and lattice forms concatenated with the identity submatrix to provide lower encoding complexity. The permutation submatrices are determined by shift parameters, which are randomly generated by a permutation process. The shift parameters are examined by two proposed methods, i.e. slope method and girth degree method. These methods will realize the possible existence of short-four-cycles that may degrade the code performance. Their performance is investigated under different parameter of LDPC codes, such as weight column, code rate, code length, etc. For benchmarking, their BER performance is put into comparison with some well-established, such as MacKay codes and optional LDPC codes in the IEEE 802.11n Standard. In the hardware implementation, their encoder/decoder derived from parity-check equation can be implemented in simple shift-registers circuits. One of the most interesting results is that the girth degree plays more significant role in code performance than the girth does.

In Chapter 5 the thesis is focused on the simple method for improving decoding process. A two-stage decoding using feedback mechanism is proposed. The method is investigated within a high-order coded modulation system with different parameters including types of LDPC codes, QAM bit-constellation level, and code length under different maximal number of decoding iteration.

In Chapter 6 the result of this work is summarized. The contribution of this work is cited. Some interesting topics are mentioned for advancing this work in the future.

#### **CHAPTER 2**

#### **BASIC THEORY**

#### 2.1 Communication System

In principal, a typical communication system consists of three major components that are transmitter, receiver, and channel. The transmitter translates the information bits into the signals that can be effectively transmitted over the channel. The channel, which is mainly the physical medium over which the communication process takes place, passes the signals to the receiver. The signals are then translated by the receiver to retrieve the information.

Conceptually, the basic elements of a communication system are illustrated with the general block diagram shown in Figure 2.1 [LC04]. As the input of the communication system, the source information in the transmitter may be either analogue (time-continuous) or discrete (symbol sequences). Symbol sequences can be produced from analogue signals via sampling and the analogue-to-digital conversion process. Prior to transmission, the source encoder removes redundancy from the source information. The symbol sequences are assumed as a stream of statistically independent, equally likely discrete symbols (binary digits) with a constant rate of  $R_s$  bits per second.

Figure 2.1 General block diagram of coded systems for digital communications

Furthermore, the symbol sequences are encoded by the channel encoder for error correcting purpose before modulation. The encoder adds redundancy to information bits

and produces data at a higher rate  $R_c$ . In case of encoding of a block code, the encoder accepts information in successive k-bit blocks and for each k bits generates a block of n bits, called a codeword, where  $n \ge k$ . Thus the encoder outputs bits at a rate  $R_c = R_s \cdot (n/k)$ .

The modulator matches the encoder output to the transmission channel. The modulator modulates binary or M-ary encoded symbols in form of waveforms appropriate physically to the transmission channel. The modulator simply converts a binary digit or the M possible encoded symbols to two or M possible waveform of equal duration.

The transmission channel passes the modulated waveform to the point just prior to demodulation. During the transmission process noise is added to the transmitted waveform. In received signals noise constitutes the most significant factor constraining the performance of a communication system. Noise limits the ability of the demodulator to reliably distinguish one modulated waveform from another, thereby producing errors in the demodulator output. Thermal noise is always present in electrical circuitry. This noise is broadband and steady in its power level, and has Gaussian amplitude statistics. The resulting errors tend to occur independently from one signaling interval to the next. Other impairments are impulsive noise and multipath interference.

At the receiver, the demodulator receives the noisy waveform. It computes and delivers estimates of the transmitted data in each separate transmission symbol interval and produces a number or a set of numbers that represent an estimate of a transmitted symbol. Since the received waveforms are noisy, the symbol decisions are subject to be erroneous.

The channel decoder receives the demodulated outputs and converts them into symbol decisions that reproduce, as accurately as possible, the data that was encoded by the channel encoder. For block coding, the decoder accepts consecutive blocks of n demodulator outputs and produces k decoded symbols for each block. The decoder attempts to make definite symbol decisions that operate on hard-decision or soft-decision. Error probability at the output of the decoder provides an important measure of the overall performance of the communication system. The symbol-error-rate, which is the average rate of occurrence of symbol errors, taken as a fraction of the total number of symbols received over a long period of time become the measure of the quality of a communication system.

Finally, the source decoder accepts the sequence of symbols from the channel decoder. In accordance with the encoding method used in the transmitter it reconstructs the information originally generated by the analogue source.

## 2.2 Channel Coding

The basic idea of forward error correcting in channel coding theory is to add redundancy to the transmitted information in order to cope with channel errors. For a binary block code the channel encoder divides the information sequence into message blocks of k information bits each [LC04]. A message block is represented by the binary k-tuple  $\mathbf{u} = (u_0, u_1, \dots, u_{k-1})$ . A total of  $2^k$  different possible messages are available. Each message  $\mathbf{u}$  is transformed independently into n-tuple  $\mathbf{x} = (x_0, x_1, \dots, x_{n-1})$  of codeword. The

set of  $2^k$  codewords of length n is called an (n, k) block code and the ratio R = k/n is called code rate. The encoder is memoryless because each message is encoded independently, which means the n-bit codeword depends only on the corresponding k-bit message. Hence, the encoder is implemented with a combinational logic circuit.

For a convolutional code, the n-k redundant bits are also added to each message to form a codeword. The channel encoder also transforms k-bit blocks of the information sequence  $\mathbf{u}$  into a code sequence  $\mathbf{v}$  of n-symbol blocks. This transformation proceeds with code rate R = k/n. In contrast to block code, the encoder of convolutional code is not memoryless because each encoded block depends not only on the corresponding k-bit message block at the same time unit but also on m previous message blocks. Hence, the encoder is said to have a memory order of m. The encoder is implemented with a sequential logic circuit.

In order to describe the mechanism of channel coding, a simplified model of a channel coding system is depicted in Figure 2.2. The encoder transforms the information sequences  $\mathbf{U}$  into a discrete encoded sequence  $\mathbf{X}$  called as codeword [LC04] and transmits it over the noisy channel. The decoder receives the noisy sequence  $\mathbf{Y}$ . The sequence  $\mathbf{Y}$  is a non-deterministic function of the channel input  $\mathbf{X}$ , and the decoder tries to reconstruct the input string  $\bar{\mathbf{U}}$  based on the knowledge of  $\mathbf{Y}$ .

Figure 2.2 A simplified model of channel coding system

A model for the channel is necessary to analyze such a system. In this model, it is assumed that the output sequence  $\mathbf{Y}$  of the channel has the same length as the input sequence  $\mathbf{X}$ , and depends on  $\mathbf{X}$  via a conditional probability density function (pdf)  $p_{\mathbf{Y}|\mathbf{X}}(\mathbf{y}|\mathbf{x})$ . For special cases, further consideration must be made.

In case of a memoryless channel, the channel output at any time instant depends only on the input at that time instant, i.e., if  $\mathbf{y} = y_1 y_2 \dots y_n$  and  $\mathbf{x} = x_1 x_2 \dots x_n$ , then  $p_{\mathbf{Y}|\mathbf{X}}(\mathbf{y}|\mathbf{x}) = \prod_{i=1}^n p_{Y|X}(y_i \mid x_i)$ . In this case, the channel is completely described by its input and output bits, and the conditional pdf  $p_{\mathbf{Y}|\mathbf{X}}(\mathbf{y}|\mathbf{x})$  for one time instant.

In this kind of channel, the output of the channel will be independent and identically distributed copies of some random variable Y as the input to the channel is generated by independent and identically distributed copies of a random variable X. Hence, the information between random variable X and Y, I(X;Y), is a function of the pdf of X.

For analyzing the system, the additive white Gaussian noise (AWGN) channel is commonly applied as the channel model, which is parameterized by a non-negative real number  $\sigma$ . The channel output **Y** is given by  $\mathbf{X} + \mathbf{N}$ , where **X** is the channel input and **N** is a Gaussian random variable with mean 0 and variance  $\sigma^2$ . The conditional pdf  $p_{Y|X}(y|x)$  is therefore a Gaussian pdf with mean  $\mu$  and variance  $\sigma^2$ .

In case of a binary symmetric input channel, the channel is parameterized with a parameter p (i.e. the crossover probability of the channel) and output binary alphabet  $\{0,1\}$ .

By supposing that the input distribution of a binary-input channel conditioned on the knowledge of the received value y, that is, a-posteriori probabilities Pr(X = 0|Y = y) and Pr(X = 1|Y = y), their ratio can be computed using Bayes' rule

$$\frac{\Pr(X=0 \mid Y=y)}{\Pr(X=1 \mid Y=y)} = \frac{p_{Y\mid X}(y \mid 0)}{p_{Y\mid X}(y \mid 1)} \frac{\Pr(X=0)}{\Pr(X=1)}$$

(2.1)

Hence, the ratio  $\frac{p_{Y|X}(y|0)}{p_{Y|X}(y|1)}$  is sufficient for the estimation of the input to the channel.

This quantity corresponding to the output y of a binary-input channel is called likelihood ratio. Its logarithm  $\log \frac{p_{Y|X}(y\mid 0)}{p_{Y|X}(y\mid 1)}$  is called the log-likelihood ratio (LLR).

#### 2.3 LDPC Codes

#### 2.3.1 Description

The ensembles of LDPC codes are defined by the set of parity-check matrices in a non-systematic form with a small number of ones in each column and in each row (see Figure 2.3). Since each row of the parity check matrix  $\mathbf{H}$  is a single parity check, an LDPC code can be viewed as the concatenation of (n-k) single parity check codes in parallel, where n is the codeword length and k is the information bit length [Li02].

Figure 2.3 Parity check matrix H of an LDPC code

Alternatively, LDPC codes can be represented by a Tanner graph [Tann81]. This bipartite graph utilizes variable (or bit) nodes (illustrated as circle) and check nodes (box) to represent the columns and rows of the parity check matrix **H** and uses inter-connecting edges to represent the relations between variable and check nodes (see Figure 2.4). The variable nodes represent elements of the codeword as variables, while the check nodes represent constraints among these variables. For binary linear codes, the variable nodes represent binary variables, and a check node assures that the binary sum of all its neighbors is zero.

Figure 2.4 Representation of LDPC codes

Based on the fraction of non-zero elements in the columns of their parity-check matrix, LDPC codes are categorized as regular and irregular. The regularity of LDPC codes corresponds to the uniformity of their column weights and row weight as well. The parameter of the regularity includes the column weight (corresponds to the variable node degree in the bipartite graph)  $\gamma$  and the row weight (the check node degree)  $\rho$ . An LDPC code is considered to be  $(\gamma, \rho)$ -regular if all column have weight  $\gamma$  and all rows have weight  $\rho$ . Meanwhile, irregular LDPC codes are not constrained to uniform row or column weights. Their node degree profiles,  $\gamma(i)$  and  $\rho(i)$ , are usually used to describe the distributions of row weights and column weights, respectively. Another important parameter of LDPC codes is the girth. It is defined as the length of the shortest cycle in the bipartite graph. A cycle of length of four as the girth is highlighted by a dashed line in Figure 2.4.b.

The regular LDPC codes have a minimum distance (averaged over the ensembles of the code) which increases linearly with the block size, provided the column weight is at least 3 [Gall63]. This implies that the codes have excellent asymptotic performance in the code length. With carefully designed row and column degree profiles, irregular LDPC codes can outperform regular LDPC codes [LMSS98, RSU01, CRU01].

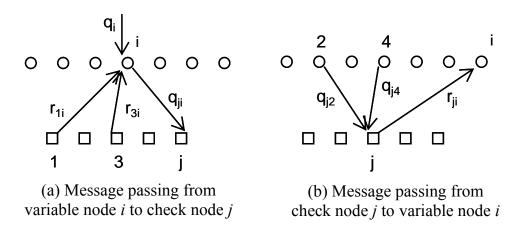

The decoding of an LDPC code takes place using an iterative message-passing algorithm. The algorithm is working based on belief propagation operating on the graph representation of the code. The message-passing algorithm is also known as the sumproduct algorithm, where (soft) messages are passed from bit nodes to check nodes and check nodes to bit nodes, vice-versa, in an iterative way until the message is correctly

decoded before the maximal number of iterations is exceeded or failed otherwise. The girth plays an important role in determining the performance of LDPC codes because the performance of the message-passing algorithm is adversely affected by the existence of short cycles. The convergence of a message-passing decoder is optimal in the ideal case where the bipartite graph is tree-like or cycle-free. However, in practice, the existence of short cycles within LDPC codes is difficult to be avoided in constructing the codes. Nevertheless, the suboptimal decoder performs quite satisfactorily.

#### 2.3.2 Code Construction

Based on their construction, LDPC codes can be divided into two categories: random codes and structured codes. Random LDPC codes are constructed by computer search based on certain design rules or graph structures, such as girth and node degree distribution, while structured LDPC codes are constructed based on algebraic and combinatorial methods.

In general, random LDPC codes with long code length perform closer to the Shannon limit than their equivalent structured LDPC codes. However, the random LDPC codes do not have sufficient structure to provide simple encoding and hence, is highly complex to implement in hardware. The wiring structure of the encoder is very difficult. On the other hand, structured codes are advantageous in encoding over random codes. LDPC codes in cyclic or quasi-cyclic structure can be encoded with simple shift registers. Their encoding complexity is linearly proportional to the number of parity-check bits for serial coding and to the code length for parallel encoding. For practical lengths, in fact, LDPC codes with well-designed structure are capable of equally performing well, even outperforming LDPC codes with equivalent random structure.

The construction of random codes is mostly based upon random edge connections. A common construction technique is to build the parity-check matrix using random permutation matrices as described in [KWD99]. The random construction prohibits the creation of cycles of length four by maintaining column weight and row weight to be uniform. Gallager [Gall62] showed that the ensemble of such codes poses excellent distance properties provided column weight of at least three and row weight is greater than column weight. MacKay *et al.* [KN95] provided algorithms to generate semi-randomly codes with sparse parity check matrices.

Richardson *et al.* [RSU01, RU01] and Luby *et al.* [LMSSS97, LMSS98, LSMS01] define ensembles of irregular LDPC codes, in which column-weight and row-weight are not uniform. These codes are parameterized by the polynomial of node degree distribution, which can be optimized via density evolution algorithm. By relaxing the regularity code constraint and allowing irregular degree sequences the performance of Gallager's original LDPC construction could be improved. Several years before, MacKay *et al.* [KWD99] have explored some examples of irregular construction. For finding good irregular distributions for LDPC codes Feldman and Karger [FK02] applied linear programming techniques to develop heuristics. Chung *et al.* [CFRU01] developed algorithms to compute the capacity of randomly constructed LDPC codes and used these algorithms to provide optimized irregular codes, which can achieve asymptotically 0.0045 dB of the Shannon

limit and simulated performance within 0.04dB of the Shannon bound for a block length of  $10^7$  at a bit error rate of  $10^{-6}$ .

On the other hand, there have been some works to create some classes of LDPC codes in structured form based on the algebraic approach. Margulis [Marg82] applied explicit graph constructions to Gallager codes. Rosenthal *et al.* [RV00] extended this technique using Ramanujan graphs to build LDPC codes. Bond *et al.* [BHS00] proposed circulant matrices to build LDPC codes. Some types of LDPC codes employing the circulant matrices are the following: array codes [Fan00], repeat accumulate codes [DJE98] and their extension, irregular repeat accumulate codes [JKM00] and extended irregular repeat accumulate codes [YLR02], then combinatorial codes [KD00, VM04, JW01], finite geometry codes [KLF01], RS-based LDPC codes [DXGL03], convolutional LDPC codes [FZ99, BPZ99], product accumulate codes [LRG04]. Ping *et al.* [PLP99] have shown how the parity-check matrix can be built from separate deterministic and random components with only a small loss in code performance. Tang *et al.* [TXKLG04] proposed hybrid method to construct LDPC codes by combining several base constructions, i.e. Gallager codes, finite geometries codes, and circulant codes.

In constructing LDPC codes there have been some issues that present the requirement as follows

- Computation: the amount of computation in check nodes and variable nodes also increases, if column weight and row weight increase, respectively. The critical intensive computation is in the check nodes.

- Efficiency: the memory size is determined by the size of parity check matrix. The small parity check matrix can save the required chip area necessary for storing the memory.

- Flexibility: the rate adjustment is required to support many different code rates, and also support H-ARQ mechanism. A single parity check matrix capable of performing rate scalability can save memory size

In practice, the recent code design is targeting LDPC codes having excellent performance and providing flexibility and low encoding/decoding complexity. Both parameters are always trade-off in design. Their features can be summarized as follows

- Structured block: the matrix is composed of the same style of permutation subblocks, which allows structured decoding leading to the reduction of decoder implementation

- Low-complexity encoding: the encoding is performed in a structured, recursive manner, without degrading the performance with multiple weight-1 columns

- Designed to match the OFDMA scheme: the matrices are provided in different base matrices for exact code rate for different block sizes.

- Compact representation: The shift values for each block size are derived from the largest block size of the code rate.

- Simplified decoder architecture: each base matrix has 24 columns, which perform better, and provide a larger parallelization. The same number of columns between code rates minimizes the number of different expansion factors that must be supported.

Some companies have proposed their practical schemes of LDPC codes for broadband wireless access, such as Intel, Motorola, Nortel, etc. Intel [XJ04] proposed efficient encoding technique using the triangular matrix structure and adapted the parity-check matrix of extended irregular repeat accumulate. With this structure, the parity bits in codewords are generated by a differential encoder. Motorola [BCB04] proposed the modification of Intel's LDPC codes by introducing the modified triangle matrix so that the recursive encoding is enabled. Samsung [Kim04] applied Richardson's efficient encoding technique and adapted the permutation matrix for its parity-check matrix. Its idea is to make use of the lower-triangular submatrix and make dimension of a submatrix as small as possible. Nortel [PSJ04] adopted the encoding technique of  $\pi$ -rotation LDPC codes [EC01]. The parity-check matrix is composed of several sub-matrices, which slopes are rotated at certain degree.

An informal LDPC group has been working on the goal of achieving consensus on an optional advanced LDPC code for the OFDMA PHY [IEEE05]. A downselection process was conducted to get best codes among eight candidates: Intel, LG, Motorola, Nokia, Nortel, Runcom, Samsung, and TI. The candidates shared many desirable features. After redesigning process, Motorola with its enhanced proposal came out as the winner [IEEE05].

#### 2.3.3 Encoding

It is well-known that the significant drawback of LDPC codes is their high encoding complexity, which scales as a quadratic of the code block length. This fact has inspired research into the area of structuring the codes in order to reduce encoding complexity, which is practically of importance.

Basically, the encoding of LDPC codes proceeds using two methods, i.e. the encoding with generator matrix derived from its corresponding parity check matrix and the encoding with reduced encoding complexity. The latter method is proposed to reduce the complexity of the first method, which is originally applicable for encoding linear block code.

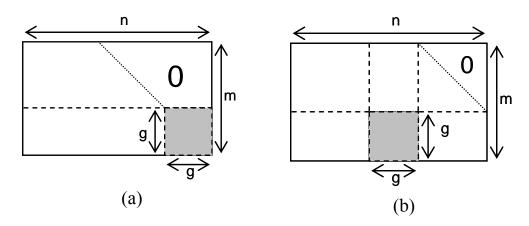

In encoding with a generator matrix, the process of encoding an LDPC codes requires the generator matrix  $\mathbf{G}$ , which corresponds to the parity check matrix  $\mathbf{H}$  by the expression  $\mathbf{G}\mathbf{H}^T=0$ . The parity check matrix  $\mathbf{H}$  is transformed via Gauss-Jordan elimination and columns reordering into a systematic form  $\mathbf{H}_S=[\mathbf{P}^T\ \mathbf{I}]$  where  $\mathbf{P}^T$  is a transposed parity-check submatrix and  $\mathbf{I}$  is an identity matrix. From this, a generator matrix  $\mathbf{G}=[\mathbf{I}\ \mathbf{P}]$  is produced. The encoding is performed by multiplying  $\mathbf{G}$  and information vector  $\mathbf{u}$  via the relation  $\mathbf{x}=\mathbf{G}^T\mathbf{u}$ . The number of operations required to calculate each element of the transmitted  $\mathbf{x}$  is k multiplications and k-1 additions. Hence, the total number of operations required by this process is  $n \times k$  multiplications and  $n \times (k$ -1) additions. This method reveals the drawback of LDPC codes, in which the encoding complexity scales as a quadratic of the block length. The other drawback is the parity-check submatrix  $\mathbf{P}$  is generally not sparse. These lead to long latency and high storage requirement.