# A data processing firmware for an upgrade of the Outer Tracker detector at the LHCb experiment

Dissertation zur Erlangung des Grades Dr. rer. nat.

vorgelegt von Dipl.-Phys. Stefan Swientek

Fakultät Physik Technische Universität Dortmund

> Dortmund Januar 2015

Erstgutachter: Prof. Dr. Bernhard Spaan

Zweitgutachter: Priv.-Doz. Dr. Reiner Klingenberg

#### **Abstract**

This thesis describes the data processing software for an Outer Tracker upgrade at the LHCb experiment. The 2018/19 intended upgrade for the LHCb detector will introduce new readout electronics on the front end of the detector as well as on the back end. The read out electronics on the back end of the detector will use a common board equipped with a Field Programmable Gate Array (FPGA). To ensure a correct data processing for each subdetector, the firmware used on the FPGA will contain subdetector specific data processing parts. The data processing part for the Outer Tracker includes receiving the data, sorting incoming data streams, merging hit pattern and drift times of three consecutive bunch crossings, clustering and formatting the data for an accurate output. In addition, a mezzanine card, called the SantaLuz board, is presented which can be used to extend existing FPGA boards with up to eight optical transceivers.

#### Zusammenfassung

Diese Arbeit beschreibt die Datenverarbeitungssoftware für ein Outer Tracker Upgrade am LHCb Experiment. Das für 2018/19 vorgesehene Upgrade des LHCb Detektors wird sowohl am Detektor als auch abseits dessen neue Ausleseelektronik einführen. Die Elektronik abseits des Detektors wird aus einer mit einem FPGA bestückten Platine bestehen. Um eine korrekte Datenverarbeitung zu gewährleisten, wird es für jeden Subdetektor eine eigene Datenverarbeitungssoftware auf der Firmware des FPGA geben. Die Datenverarbeitung für den Outer Tracker empfängt die Daten, sortiert die eingehenden Datenleitungen, fasst die Trefferliste und die Driftzeiten aus drei aufeinanderfolgenden Bunch Crossings zusammen, sucht nach Gruppierungen von Treffern und formatiert die Daten zur korrekten Ausgabe. Zusätzlich wird das SantaLuz board vorgestellt, eine Erweiterungskarte für bereits vorhandene FPGA Karten, die bis zu acht optische Transceiver bereit stellen kann.

## Contents

| 1 | Introduction                                                                                          | 1                                      |

|---|-------------------------------------------------------------------------------------------------------|----------------------------------------|

| 2 | The Large Hadron Collider 2.1 ATLAS and CMS                                                           | <b>3</b>                               |

| 3 | The LHCb experiment  3.1 Physical motivation for the LHCb experiment                                  | 7<br>7<br>10<br>16                     |

| 4 | The Outer Tracker and its upgrade 4.1 The Outer Tracker detector                                      | 19<br>19<br>21<br>22<br>26<br>26<br>27 |

| 5 | The LHCb back end electronics upgrade  5.1 The back end electronics upgrade structure  5.2 The ATCA40 | 29<br>29<br>30<br>31                   |

| 6 | Field Programmable Gate Arrays6.1 FPGA technologies6.2 FPGA structures6.3 Working with FPGAs          | 33<br>35<br>35<br>37                   |

| 7 | The AMC40 firmware for the OT upgrade 7.1 The AMC40 common part                                       | 43<br>44<br>45<br>46<br>47<br>51<br>52 |

### Contents

|    |        | 7.2.6    | Clustering              | 61 |

|----|--------|----------|-------------------------|----|

|    |        | 7.2.7    | Output formatting       | 63 |

|    |        | 7.2.8    | Complete design         | 64 |

|    |        | 7.2.9    | Simulation              | 67 |

|    |        | 7.2.10   | Bandwidth consideration | 69 |

| 8  | Test   | systen   | 15                      | 73 |

|    | 8.1    | The M    | iniDAQ                  | 73 |

|    | 8.2    | The Sa   | antaLuz board           | 74 |

| 9  | Con    | clusions | 5                       | 77 |

| Ac | ronyı  | ns       |                         | 79 |

| Αŗ | pend   | lix      |                         | 83 |

| Bi | bliogi | aphy     |                         | 87 |

| Da | anksa  | gung     |                         | 93 |

# List of Figures

| 2.1  | The LHC at CERN                                                 |

|------|-----------------------------------------------------------------|

| 2.2  | The ATLAS and CMS detectors                                     |

| 2.3  | The ALICE detector                                              |

| 3.1  | Standard Model of particle physics                              |

| 3.2  | The unitarity triangle                                          |

| 3.3  | $b\bar{b}$ distribution in pp-collisions                        |

| 3.4  | The LHCb detector                                               |

| 3.5  | The Vertex Locator                                              |

| 3.6  | The RICH detectors                                              |

| 3.7  | The tracking stations T1 - T3                                   |

| 3.8  | The Inner Tracker                                               |

| 3.9  | The LHCb calorimeter system                                     |

| 3.10 | The LHCb Muon System                                            |

| 3.11 | Data acquisition at LHCb                                        |

| 4.1  | Scheme of the Outer Tracker in T1 to T3                         |

| 4.2  | Close up of an Outer Tracker module                             |

| 4.3  | Straw tube functionality                                        |

| 4.4  | Possible track trajectories in a single Outer Tracker module 21 |

| 4.5  | The OT FE Box                                                   |

| 4.6  | The Outer Tracker straw occupancy                               |

| 4.7  | Straw tube hit efficiency                                       |

| 4.8  | The Outer Trackerr hit resolution                               |

| 4.9  | Distance to drift time relation                                 |

| 4.10 | The Outer Tracker drift time spectrum                           |

| 4.11 | MicroSemi based upgrade plans                                   |

| 4.12 |                                                                 |

| 5.1  | ATCA carrier board and setup                                    |

| 5.2  | Schematic view of an ATCA40 board                               |

| 5.3  | The AMC40 architecture                                          |

| 5.4  | An example for a jitter                                         |

|      |                                                                 |

| 6.1  | SRAM memory structure                                           |

| 6.2  | EEPROM memory structure                                         |

## List of Figures

| 6.3  | Logic elements inside an FPGA                                  |

|------|----------------------------------------------------------------|

| 6.4  | Simple generic FPGA architecture                               |

| 6.5  | Visualised VHDL block                                          |

| 6.6  | HDL Designer generated flowchart                               |

| 6.7  | QuartusII generated RTL view                                   |

| 6.8  | VHDL block example for simulation 41                           |

| 6.9  | Simulation of the example code                                 |

| 6.10 | Stratix IV Development Kit                                     |

| 7.1  | AMC40 MiniDAQ firmware overview                                |

| 7.2  | Overview of the main data processing working steps 45          |

| 7.3  | Content of an incoming 224 bit wide data bus                   |

| 7.4  | Hit pattern sorting scheme                                     |

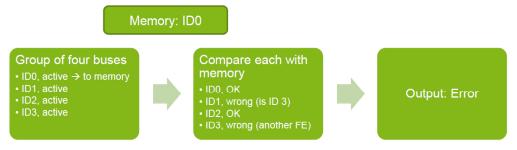

| 7.5  | Decision making procedure of the algorithm warning the user 50 |

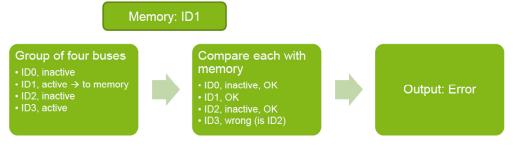

| 7.6  | Possibilities of different drift time receiving                |

| 7.7  | Illustration of the hit pattern merging algorithm              |

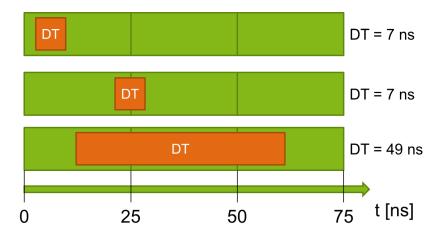

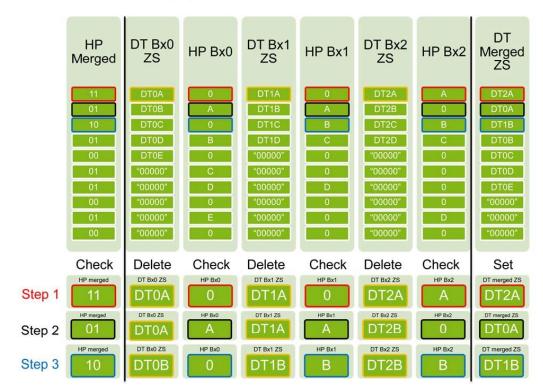

| 7.8  | Illustration of step-by-step arranging                         |

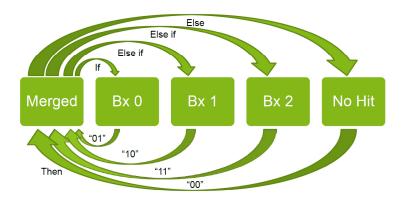

| 7.9  | Zero unsuppressing mechanism                                   |

| 7.10 | Merging mechanism for zero unsuppressed drift times 59         |

| 7.11 | Examples for the first zero suppressing step 60                |

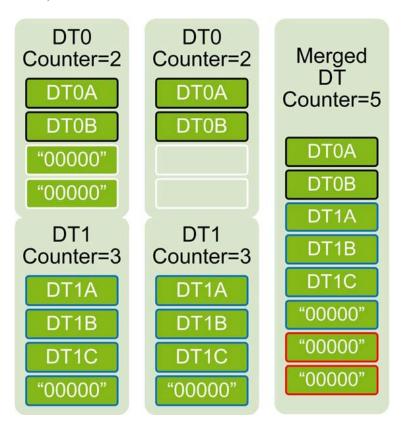

|      | Example for merging zero suppressed drift time vectors 60      |

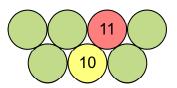

| 7.13 | Possibilities for clusters                                     |

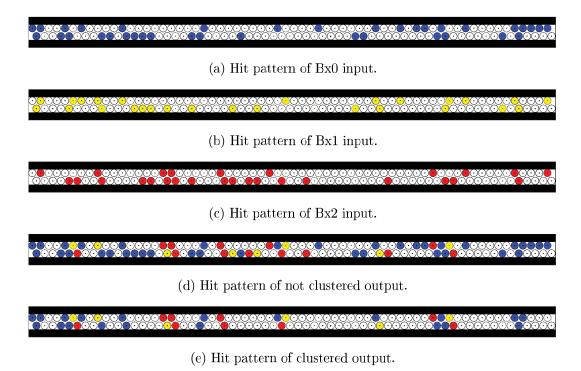

| 7.14 | A hit pattern before and after clustering 62                   |

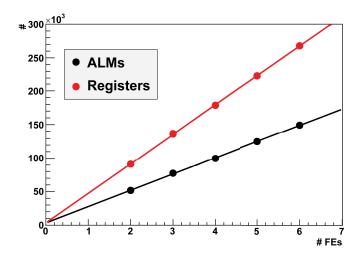

| 7.15 | Linear fit for logic usage                                     |

| 7.16 | Data processing simulation with random generated data 68       |

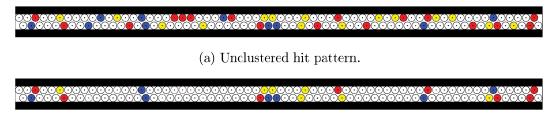

| 7.17 | Visualised hit patterns                                        |

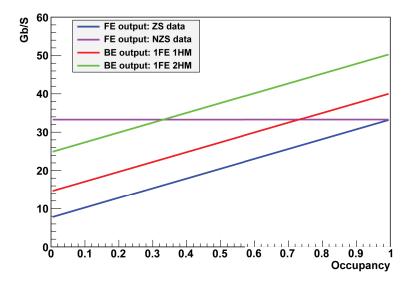

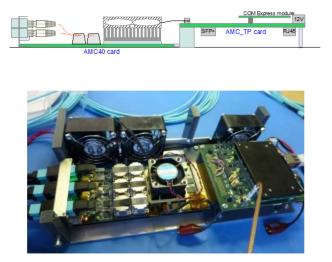

|      | Occupancy vs. bandwidth usage                                  |

| 7.19 | Bandwidth usage of different amount of FEs                     |

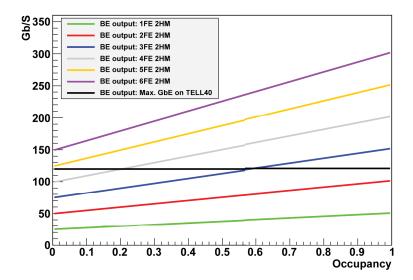

| 7.20 | Bandwidth usage with LLT reduction                             |

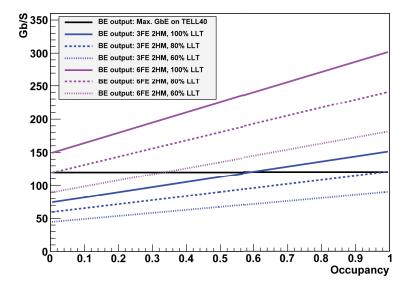

| 8.1  | Picture of the MiniDAQ                                         |

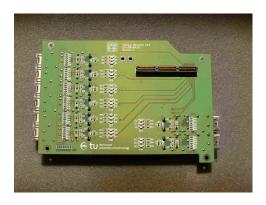

| 8.2  | The SantaLuz board                                             |

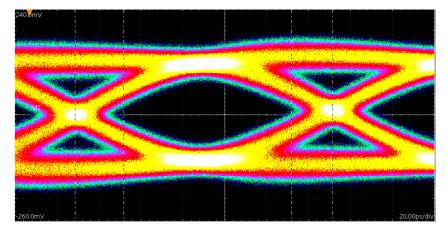

| 8.3  | Eye diagram of the SantaLuz board                              |

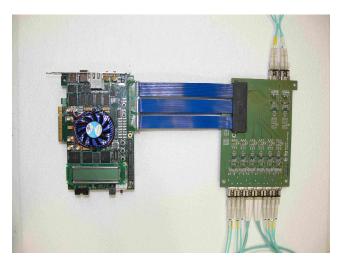

| 8.4  | Picture of a SantaLuz test setup                               |

## 1 Introduction

Physicists never stop asking questions. Why does the earth turn around the sun? Why does the apple fall to the ground? What is an atom built of? In modern particle physics these questions are far more detailed. Where does the mass of elementary particles come from? What happened during and directly after the Big Bang?

To answer these and other questions particle physicists are trying to reproduce similar conditions as in the beginning of our universe. Therefore, protons and other particles are collided with high energy in large particle colliders. The currently largest particle collider is the Large Hadron Collider (LHC) at CERN. Particles were colliding from 2010 to 2012 at a centre-of-mass energy of up to 8 TeV and the LHC will continue with colliding particles in 2015. To reconstruct the events of colliding particles large experiments are built with different purposes. One of the four big experiments at the LHC is the LHCb experiment, which is specialised to observe particles with a small production angle to the beam axis. This experiment was successfully observing B-meson decays for the whole first run period of the LHC, taking and processing a large amount of data.

An upgrade of the LHCb detector is intended for the years 2018/19 to increase the rate with which LHCb is capable of taking data. The hardware trigger shall be removed and the whole detector upgraded. With this change of the trigger method, LHCb will be able to specialise their triggering and therefore be able to measure decays more precisely, or adapt the triggers to new physics. This would also increase the data sent from the detector to the back end electronics, where it has to be processed before sending it to the Data Acquisition (DAQ). To process that amount of data, special electronics called the AMC40 is developed and working with an FPGA. A firmware for this FPGA has to be programmed to perform all necessary tasks needed for a fully functioning data taking.

The goal of this thesis is to develop a firmware for the data processing part of the AMC40 firmware for an upgrade of the Outer Tracker, a gaseous straw tube detector, of the LHCb experiment. This firmware has to perform without failure during high data flow and various running conditions.

First a short introductory overview of the LHC and the three large experiments AT-LAS, CMS and ALICE is given in Chapter 2. Afterwards a motivation for LHCb, the fourth large experiment at the LHC, is given, including an overview of the detector in Chapter 3. A requirement for the development of a data processing firmware for

#### 1 Introduction

a specific detector type is to understand its working procedure, which is explained for the Outer Tracker in Chapter 4, including the plans for the upgrade. Since the data processing firmware will be used on specific electronics, the design of the upgraded back end electronics is summarised in Chapter 5. Chapter 6 covers the basics of FPGAs, e.g. their structure and working procedures. The developed data processing firmware is explained in detail in Chapter 7, containing every step in data processing and explaining each function and algorithm. A comparison in logic usage on the FPGA is also given for different possibilities of workload on the back end electronics. In Chapter 8 two test setups are introduced, which are able to test a finished firmware on hardware. Finally, conclusions are given in Chapter 9.

## 2 The Large Hadron Collider

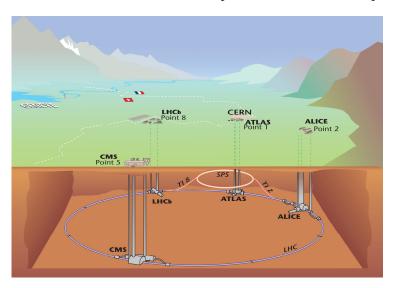

The LHC at CERN<sup>I</sup> near Geneva is the largest proton-proton-collider in the world. It is a circular proton-proton-collider with a circumference of 26.7 km, also capable of accelerating and colliding heavy ions. Built in a depth of about 100 m, the LHC is designed to collide protons with a centre of mass energy of  $\sqrt{s}$ =14 TeV [1], whereat during LHC data taking from 2010 to 2012 (called LHC Run I) the energy was set to a maximum of 8 TeV [2]. The protons are collided at four collision points, where the four large experiments of the LHC are located, called ATLAS, CMS, ALICE and LHCb (see Figure 2.1). A short overview of each detector will be given in the following, while the LHCb detector will be explained in detail in Chapter 3.

Figure 2.1: The LHC at CERN, with the four large experiments ATLAS, CMS, ALICE and LHCb [3].

<sup>&</sup>lt;sup>I</sup>European Organization for Nuclear Research.

## 2.1 ATLAS and CMS

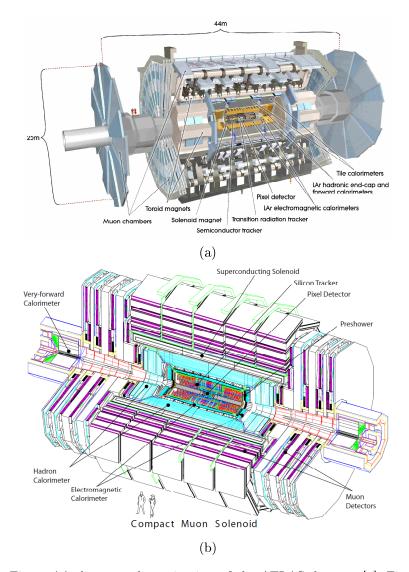

ATLAS (A Toroidal LHC ApparatuS) and CMS (Compact Muon Solenoid) are the two largest experiments at CERN. Their main goal is to search for new physics. For example, ATLAS and CMS try to discover particles which can be assigned to supersymmetric theories [4]. Both detectors cover the whole area around the interaction point. Figures 2.2a and 2.2b show both detectors in a schematic view.

Figure 2.2: Figure (a) shows a schematic view of the ATLAS detector [5], Figure (b) the CMS detector [6].

Such detectors are built with a tracking detector near the collision point, followed by a detector for energy measurements, like calorimeters. Finally, a muon spectrometer is placed at the outermost part of the whole detector.

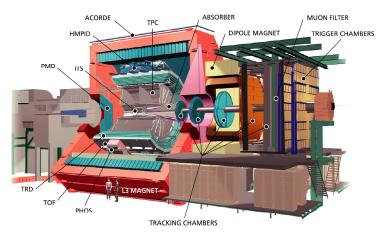

### 2.2 ALICE

ALICE (A Large Ion Collider Experiment) is another detector at LHC covering the whole area around the interaction point, but specialised in analysing heavy ion collisions. Figure 2.3 shows a schematic of the ALICE detector, which is equipped with various tracking detectors. Such large amount of tracking detectors is needed to observe a high multiplicity of tracks, which occur at heavy ion collisions. The

Figure 2.3: The ALICE detector [7]. A large amount of tracking detectors is used to capture the enormous number of tracks (labelled: ITS, TPC, TRD).

purpose of ALICE is to study the quark-gluon-plasma in this heavy ion collisions [7]. The quark-gluon-plasma is a state in which all matter should have existed a few milliseconds after the big bang. Thus, the results of this experiment could contribute to the understanding of Quantum Chromodynamics (QCD) [8].

## 3 The LHCb experiment

The LHCb (Large Hadron Collider beauty) experiment is dedicated to search for indirect evidences of new physics in Charge-Parity (CP) violating processes and rare decays of bottom<sup>I</sup> and charm hadrons. Thus, its complete setup in hardware as well as software is specialized for b and c physics.

## 3.1 Physical motivation for the LHCb experiment

To introduce into the physical motivation of the LHCb experiment, a short introduction to the Standard Model of particle physics (SM) and LHCb specific searches is given before explaining the design of the LHCb detector.

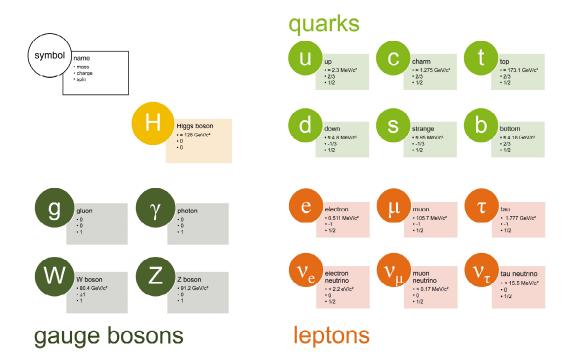

#### The Standard Model of particle physics

The Standard Model of particle physics is a theory that describes the interactions of elementary particles. It covers the fundamental forces, which are represented through their spin 1 gauge bosons in Figure 3.1. These are the photon  $(\gamma)$ , representing the gauge boson of the electromagnetic force, the W<sup>+</sup>-, the W<sup>-</sup>- and the Z<sup>0</sup>- boson, mediating the weak interaction, and the gluons for the strong interaction. The photon is a massless electrically neutral boson and its own antiparticle [9]. In contrast to the other gauge bosons the gauge bosons of the weak interaction are massive<sup>II</sup> and the W<sup>±</sup> are the only gauge bosons carrying an electric charge. The W<sup>±</sup>, Z<sup>0</sup> and  $\gamma$  are unified within the electroweak interaction [9]. The gluons are eight massless gauge bosons mediating the strong interaction and carry a charge called "colour". Three charges of colour (red, green, blue) combine up to eight gluons with different colour-anticolour combination [8].

The SM also identifies the quarks and leptons (both fermions with a spin of  $\frac{1}{2}\hbar$  as fundamental fermions, shown in Figure 3.1. Additionally, there is an antiparticle for each fermion: same particles with all charge-like quantum numbers reversed. The quarks are the building blocks for all known particles. They are categorised into three families, each consisting of an up-type quark (up or u, charm or c, top or t)

<sup>&</sup>lt;sup>I</sup>The bottom quark is also often referred to as the beauty quark.

$<sup>^{\</sup>rm II}{\rm W}^{\pm}$ : 80.4 GeV/c<sup>2</sup>, Z: 91.2 GeV/c<sup>2</sup>.

#### 3 The LHCb experiment

and a down-type quark (down or d, strange or s, bottom or b). Hereby, each up-type quark carries an electric charge of  $\frac{2}{3}$ e and each down-type quark an electric charge of  $-\frac{1}{3}$ e. The quarks and antiquarks can be combined to hadrons, represented by mesons as a quark-antiquark combination and baryons as a combination of three quarks or three antiquarks. Well known baryons are the proton, consisting of two up and one down quark (uud) or the neutron built of one up and two down quarks (udd).

The leptons are also categorized into three families, each consisting of an electrically charged particle (electron or e, muon or  $\mu$ , tau or  $\tau$ ) and an electrically neutral neutrino ( $\nu_e$ ,  $\nu_{\mu}$ ,  $\nu_{\tau}$ ). The properties of the charged leptons are well measured, whereas especially the masses of the neutrinos are not known [10]. Since neutrinos are weakly interacting particles, which are nearly undetectable in a standard particle detector, their characteristics are only determined with low statistics in large experiments or through indirect measurements<sup>III</sup>.

Another part of the SM is the Higgs boson (H). This spinless boson with a mass of about  $126 \,\mathrm{GeV/c^2}$  is the boson of the Higgs field. This field explains the mass of the other particles in the SM by using the so-called Higgs-mechanism postulated in 1964 [11, 12]. In 2012 a particle was found at CERN [13, 14], which could be the Higgs boson and therefore strengthen this theory.

However, the SM is incomplete. Gravitation is not included and besides other open questions neutrinos are assumed to be massless in the SM, although measurements of neutrino oscillations have already shown the opposite.

IIIAn indirect measurement of neutrinos can be done e.g., by constraining the missing energy in a fully reconstructed event.

Figure 3.1: An illustration of the elementary particles included in the Standard Model of particle physics, with its quarks (green), leptons (red), gauge bosons (dark green) and the Higgs boson (yellow).

### Basics of LHCb specific searches

As already mentioned, LHCb searches for indirect evidences of new physics in CP violating processes. These processes could help explaining the excess in the production rate of matter over antimatter. CP violation is described through the complex phase of the Cabibbo-Kobayashi-Maskawa matrix [15, 16], which indicates the strength of flavour-changing weak decays:

$$V_{CKM} \equiv V_L^u V_L^{d\dagger} = \begin{bmatrix} V_{ud} & V_{us} & V_{ub} \\ V_{cd} & V_{cs} & V_{cb} \\ V_{td} & V_{ts} & V_{tb} \end{bmatrix}.$$

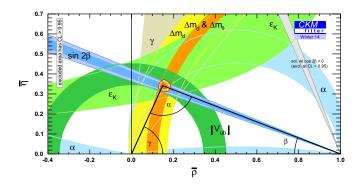

The unitarity of this matrix is required in the theory of electroweak interactions, but it still has to be proven in experiment. Six unitarity conditions of the CKM matrix can be illustrated in six different unitarity triangles. The unitarity triangle corresponding to the unitarity relation  $V_{qd}V_{qb}^{\star}$  is shown in Figure 3.2. The decay  $B^0 \to J/\psi K_S^0$  is one particle decay used to study this relation at LHCb [17].

With the information gathered from these studies, indirect measurements of the

angles and distributions of the unitarity triangles can be obtained (e.g.  $\sin 2\beta$  in Figure 3.2). The combination of all results can lead to a perfectly closed triangle and thus prove the CKM-matrix, or if the triangle does not fit (loose ends or missing endpoints of sides) disagree with the CKM-matrix and lead to new pyhsics.

Figure 3.2: The unitarity triangle corresponding to the unitarity relation  $V_{qd}V_{qb}^{\star}$  [18]. The colours indicate results of different measurements.

### 3.2 The LHCb detector

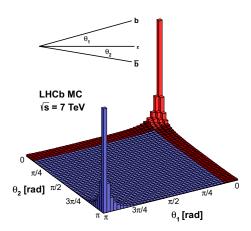

The production angle of  $b\bar{b}$  pairs in pp-collisions is a distinct distribution as shown in Figure 3.3 for LHCb. To ensure a precise measurement of decaying e.g. B mesons

Figure 3.3: The  $b\bar{b}$  distribution in pp-collisions [19].  $b\bar{b}$  pairs are produced in a small angle corresponding to the beam axis. The figure shows the distribution in LHCb at  $\sqrt{s}$ =7 TeV with clear peaks at low angles.

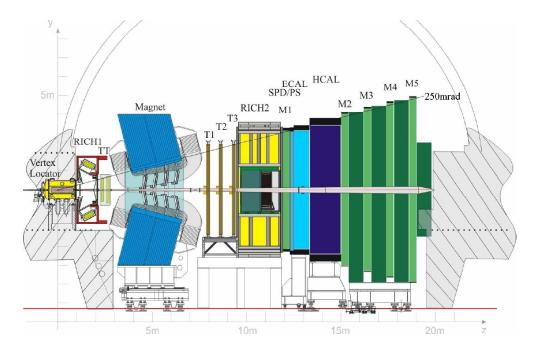

the LHCb detector is built as a one-armed forward spectrometer specialised to detect particles decaying in low angles to the beam axis. The subdetectors, as shown in Figure 3.4, will be explained in the following, starting with the tracking detectors in front of the magnet, the Vertex Locator (VELO) and the Tracker Turicensis (TT). Afterwards, both Ring Imaging Cherenkov (RICH) detectors are explained, before introducing the tracking stations T1-T3 behind the magnet. Then the calorimeters are described, finishing with the muon system.

Figure 3.4: The LHCb detector with its subdetectors [1]. Built as a one-armed forward spectrometer the collision point for the two proton beams is located inside the VELO on the left side of the figure.

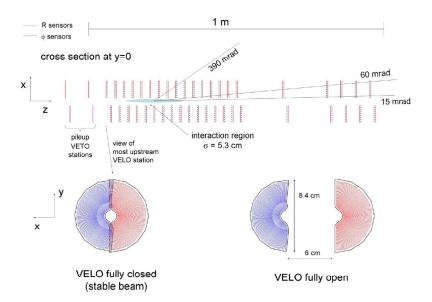

#### The Vertex Locator

The Vertex Locator is the first component of LHCb's tracking system. The detector has a special layout to reach the area as close to the interaction point as possible. With this feature it is capable of measuring secondary vertices, which are striking for b and c hadron decays. As shown in Figure 3.5, the VELO is split in two halves, which can be moved to widen or narrow the gap between them. Each half consists of 21 VELO-tracking-modules, with two layers of silicon strips: One layer to determine the distance to the beam axis (|R| sensors; red in Figure 3.5) and another to determine the polar angle of the particle track ( $\phi$  sensors; blue in Figure 3.5). The combination of both sensors leads to an explicit point in the LHCb coordinates.

With this information, the particle tracks can be observed and reconstructed close to the interaction point [1].

Figure 3.5: The Vertex Locator at LHCb [1]. On the top a cross section through the LHCb plane is shown. The 21 VELO stations can be seen as they are arranged around the interaction point of LHCb. On the bottom a closed and a fully opened VELO station is shown with an example of an |R| sensor in red and a  $\phi$  sensor in blue.

#### The Tracker Turicensis

The Tracker Turicensis is the second part of the tracking system and the last detector in front of the magnet. The TT is a silicon strip detector and covers an area of  $1300\,\mathrm{mm} \times 1500\,\mathrm{mm}$ . The tracker consists of 4 planes of silicon strips, with the inner two tilted by  $\pm 5^\circ$  in the LHCb x-y-plane<sup>IV</sup>. This so-called X-U-V-X structure will be explained in detail in Chapter 4. For more information on semiconductor detectors see [20] and [21]. With the information gathered from the TT and the VELO the first part of track recognition can be performed before the particles pass the magnet [1].

#### RICH1 and RICH2

The RICH detectors are two detectors used for particle identification. As the name implies the detectors use the Cherenkov effect [22] to provide particle identification

<sup>&</sup>lt;sup>IV</sup>The LHCb coordinate system can be seen in Figure 3.4.

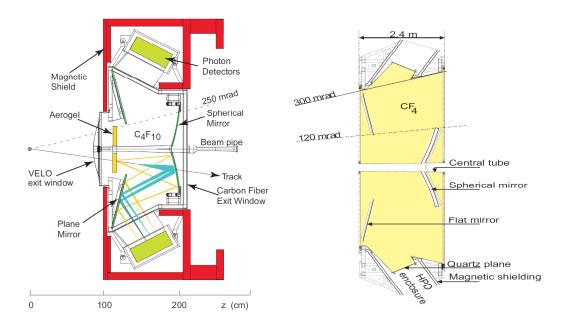

of charged particles, by measuring the diameter of the emitted cone of light. Hereby, RICH1 is positioned right after the VELO whereas RICH2 is located behind the tracking station T3. As Figure 3.6 displays, both detectors use a similar setup with a gas filled body and photon detectors at their sides. They differ just in details, such as the used gases. While RICH2 is completely filled with CF4 (Tetrafluoromethane) RICH1 uses two different media, a small block of Aerogel and C4F10 (Perfluorobutane) for the rest of the body [23]. With a complex alignment of mirrors the Cherenkov emitted photons are guided to the frame of the RICHes, where the photon detectors are positioned. With the measured intensity and position of the triggered photon detectors the speed of the particles passing through the RICHes can be determined and used for particle identification [1].

Figure 3.6: RICH1 (left) and RICH2 (right) [1]. These two detectors use the Cherenkov effect to determine the speed of passing particles by measuring the diameter of the emitted cone of light. The emitted light is then guided to photon detectors (HPD) by mirrors. The differences between these detectors are the position (see Figure 3.4) and the used medium.

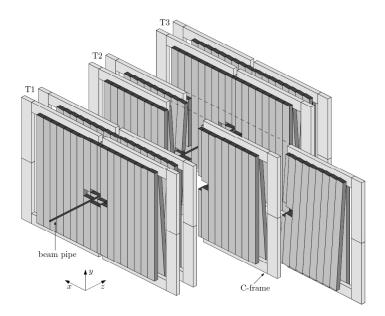

#### The Tracking Stations T1 - T3

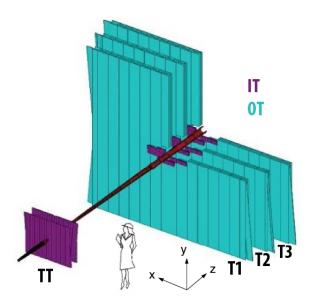

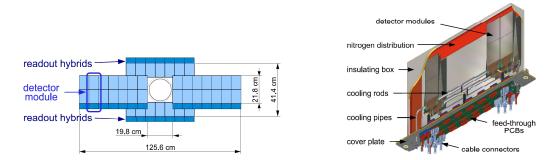

The three tracking stations T1 - T3 are located behind the magnet. As Figure 3.7 shows, each T-Station is built of an Outer Tracker (OT) and an Inner Tracker (IT). The IT uses the same technology as the TT. Its silicon strip modules cover an area of 1256 mm width and 414 mm height set in four boxes arranged as a cross (see Figure 3.8). With this positioning the innermost region of the T-Stations is covered

Figure 3.7: The figure shows the tracking stations T1-T3 and the TT [1]. The silicon detectors (TT and IT) are coloured purple and the OT (a gaseous detector) is shown surrounding the IT. Each station consists of four layers of each detector technology, with the the inner two layers tilted by  $\pm 5^{\circ}$  in the LHXb x-y-plane.

with 200 µm wide silicon strips and a resulting track resolution of about 50 µm [1]. The modules inside the boxes are arranged in four planes in the already mentioned X-U-V-X structure to gain resolution in the LHCb y-axis. The Outer Tracker is a gaseous straw tube detector, which covers an area of  $5 \times 6 \,\mathrm{m}^2$  outside the IT, and will be covered in detail in Chapter 4 [1].

Figure 3.8: Schematics of the IT box set up within the tracking stations are shown on the left. The right figure illustrates the inside of an IT box with the four layers of silicon strip modules as well as the tilted modules [1].

#### The Calorimeter System

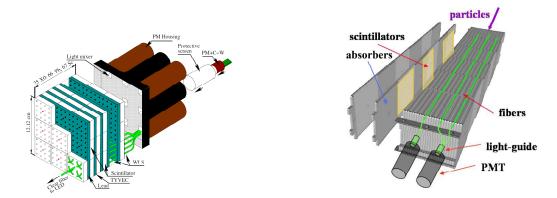

The LHCb calorimeter system consists of three different parts. The Silicon Pad Detector/PreShower (SPD/PS), the Electromagnetic Calorimeter (ECAL) and the Hadronic Calorimeter (HCAL) are lined up in this order behind RICH2 and the first muon chamber (M1). With the help of this system the energy of particles can be measured. This information is crucial for a successful particle identification. The SPD/PS consists of a lead converter, that is sandwiched by scintillating pads. Its main purpose is to separate electrons from pions. Both particles would shower in the ECAL and separating them beforehand gives a great benefit in particle identification.

The ECAL is used to measure electromagnetically interacting particles, like electrons and photons, and is built in a so-called shashlik calorimeter technology of alternating layers of lead and scintillators. The lead reduces the energy of passing particles, while the scintillators indicate how far the particle has intruded into the detector and how much light it produced. The scintillators are then read out and the penetration depth of the particle in combination with the amount of light can then be used to determine the deposited particle energy.

Finally, the HCAL determines the energy of strong interacting particles, hadrons as the name indicates. It consists of alternating layers of iron and scintillators and operates according to the same principle as the ECAL, as shown in Figure 3.9. The LHCb HCAL is oriented parallel to the LHC beam axis, thereby the length of the steel parts correspond to one interaction length in steel. The length of the HCAL is set to prevent most particles from leaving it, except for muons which are able to pass through the calorimeter system.

Figure 3.9: The LHCb calorimeter system. On the left a construction view of the ECAL is shown [24]. The shashlik building technique can be seen with alternating layers of lead and scintillators. On the right a schematic view of the HCAL is shown. In contrast to the ECAL the shashlik building technique is arranged along the particle beam direction [1].

#### The Muon System

The muon system is a crucial part of particle identification, since many final states in B decays include muons. It consists of five stations M1 to M5 positioned at the end of the detector behind the HCAL, except for M1 which is positioned between RICH2 and the calorimeters. The muon stations M2 to M5 are interleaved with iron absorbers to select muons and exclude other particles (see Figure 3.10). M1 is used to improve the p<sub>T</sub> measurement for the trigger. Each muon station is split

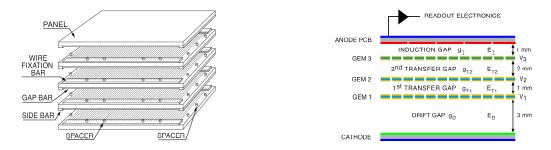

Figure 3.10: The muon system of LHCb is built of two different technologies. On the left a schematic view of the mostly used multi-wire proportional chambers is shown. On the right a schematic cross section of a triple-GEM detector is shown, which is used in the central region of M1 [1].

into four regions and equipped with Multi-Wire Proportional Chambers, which are gas detector, except for the innermost region of M1, which is built of Gas Electron Multipliers (GEMs) due to the high radiation environment. Both detectors work with the principle of ionising gases and measuring the drift time of the produced electrons. The principle of a gaseous detector is explained in detail in Chapter 4.

## 3.3 The LHCb upgrade

The whole LHCb experiment will experience an upgrade to improve its performance and be able to handle new circumstances. The instantaneous luminosity in LHCb will be raised from up to  $5 \times 10^{32}$  cm<sup>-2</sup> s<sup>-1</sup> [2] to  $10^{33}$  cm<sup>-2</sup> s<sup>-1</sup> [25]. Furthermore, the spacing between two consecutive proton bunches will be shortened to 25 ns [25] instead of the 50 ns mainly used during the first data taking period [2].

This will increase the experiments sensitivity in the b- and c-hadron decay studies, which will lead to higher precision measurements. These could surpass the precision in a lot of already published measurements, such as  $B_s^0 \to \mu^+\mu^-$  [26] and  $B^0 \to K^{*0}\mu^+\mu^-$  [27] in the flavour physics programme or the measurement of the weak phase in  $B_s^0$  [28] oscillation in studies of CP violation. With the increased sensitivity even further measurements can be obtained, including rare decays, CP violating

observables and fundamental parameters of the CKM unitarity triangles.

But not only precision can be improved, the upgraded detector can serve as a multipurpose detector in the forward direction. With a flexible trigger and the high resolution in the forward region, LHCb can easily be adapted to new interesting physics fields. The search for exotic particles or measurements of the electroweak sector are possible, too.

To perform this task all subdetectors will be upgraded, for specific details see [25]. The electronics upgrade, which will apply each subdetector, is essential to improve the data acquisition rate. A detailed view on the front end electronics upgrade for the OT will be given in Chapter 4 and for the back end electronics in Chapter 5. Besides the electronics upgrade the event trigger will be modified. Since not every event contains interesting particle decays, the detector response is scanned for specific behaviour and selected by various trigger levels.

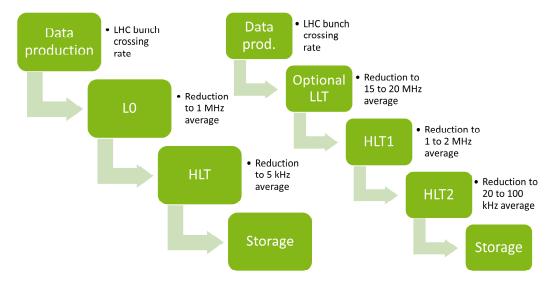

The current data reduction through trigger decisions is performed in several consecutive bandwidth reducing levels as illustrated in Figure 3.11. The data taken by

Figure 3.11: The DAQ at LHCb. On the left the current acquisition is shown with all rate reducing trigger levels. On the right a plan of the upgraded trigger steps is given. Here the data is reduced with more information than in the current triggering, where the hardware based L0 trigger uses just simple detector information.

the subdetectors with the LHC bunch crossing rate<sup>V</sup> is then buffered in the front end electronics. At this point the so-called Level-0 (L0) trigger reduces the output rate of the front end electronics to 1.1 MHz, by using direct hit information from the muon and calorimeter systems [29]. Afterwards, the data is processed in the back

<sup>&</sup>lt;sup>V</sup>The LHC bunch crossing rate was designed to be 40 MHz. However the bunch crossing rate during LHC Run I was set to 10 MHz–15 MHz [2].

#### 3 The LHCb experiment

end electronics and further reduced by the High-Level-Trigger (HLT) to an average rate of 5 kHz, through detailed cuts on particle masses and pulses. With this average rate, the data is then stored in the data storage.

For the upgrade, LHCb targets a triggerless readout of the subdetectors. So each front end electronic has to be upgraded to be able to read out the particular subdetector in an 25 ns bunch crossing spacing. With a 25 ns bunch crossing spacing the full detector has to be read out with a rate of 40 MHz, to avoid a buffer overflow on the front end side. The data is then sent to the back end electronics, in which a first processing of the data occurs and an optional Low-Level-Trigger (LLT) can reduce the output rate down to 15 MHz–30 MHz. Afterwards another trigger level, the first part of the HLT, reduces the rate to 1 MHz–2 MHz. In contrast to the actual trigger the first reduction after the upgrade is done with a software trigger, which uses a full track reconstruction instead of just muon and calorimeter information (as the current L0) [30, 31]. At the end of the data acquisition process the second part of the HLT reduces the rate to 20 kHz–100 kHz. With this rate the data is then written into the storage. A schematic view of the upgraded DAQ is shown on the right of Figure 3.11.

## 4 The Outer Tracker and its upgrade

#### 4.1 The Outer Tracker detector

As already mentioned in Chapter 3 the Outer Tracker (OT) is part of the tracking stations T1 to T3. It is a gaseous straw tube detector covering an area of  $5 \times 6 \,\mathrm{m}^2$ . Each station is equipped with four layers of 22 modules. The layers are arranged back to back with a so called X-U-V-X geometry. That means that, the modules in the X-layers are oriented along the LHCb y-axis (see Figure 4.1), whereas the modules in the U- and V-layers are rotated by  $+5^{\circ}$  and  $-5^{\circ}$  respectively in the LHCb x-y-plane to gain a hit resolution in the LHCb y-direction. Each layer consists of 14 long and

Figure 4.1: Scheme of the OT in the tracking stations T1 to T3 [32]. The X-U-V-X structure within each station can be observed just as the C-frames and the hole for the IT surrounding the beam pipe.

8 short modules, in which 7 long and 4 short modules per layer are attached to one C-frame<sup>I</sup>. The long modules contain two times 128 2.5 m long channels, arranged in a double layer structure of straw tubes, which are read out at the top and the bottom

<sup>&</sup>lt;sup>1</sup>A C-frame is a mechanical support structure, which can be pulled away from the beam pipe.

of each module. The short modules are equipped with 128 shorter straw tubes due to the adjacent IT. With this setting a total of 53,760<sup>II</sup> single straw tube channels are read out [32].

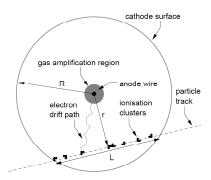

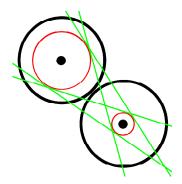

Figure 4.3: Functionality of a straw tube detector like it is used in the Outer Tracker [32]. A charged particle ionises the gas within the tube and the electrons drift towards the anode wire due to the applied high voltage. The distance to drift time relation can be seen in Figure 4.9 in Section 4.3

The double layer architecture of an OT module is shown in Figure 4.2. 128 channels are arranged in two lines, with 64 straw tubes each. An OT straw tube is up to 2.5 m long with an inner diameter of 4.9 mm and continuously flushed with a gas mixture of 70% Ar, 28.5% CO<sub>2</sub> and 1.5% O<sub>2</sub>. The anode wire is made of gold-plated tungsten of  $25 \,\mu\mathrm{m}$  diameter and operated at a high voltage of  $+1550 \,\mathrm{V}$ , whereas the cathode is a sandwich of two Kapton-XC<sup>III</sup> foils with a layer of aluminium in between. When a charged particle passes through the straw tube it ionises the gas mixture and electrons are set free in this ionisation clusters (see Figure 4.3). These electrons are then attracted to the positive high voltage of the anode and the time of arrival is measured in relation to the LHC clock. With the measured drift time a distance drift time relation can be used to get the minimal distance the particle passed the anode. Thus, an accuracy of about 210 µm [32] could be obtained during LHC Run I. If two adjacent straws are hit and the distance of the track to the anode is known, this arrangement reduces the number of possible tracks through a module to four. Figure 4.4 shows the possible track reconstruction. To reduce the number of possible tracks even further, more consecutive modules are needed, and used in the OT. To determine the distance of the track to the anode a drift time is measured.

<sup>&</sup>lt;sup>II</sup>Two short modules (one above and one below the beam pipe) in each layer are equipped with 64 channels only and read out with one front end box for two module layers.

<sup>&</sup>lt;sup>III</sup>Kapton® is a polyimide film developed by DuPont.

Figure 4.4: Possible track trajectories in a single OT module. Since only the hit distance (red) to the anode is known, four trajectories (green) are possible within a single module. By adding more consecutive modules these can be reduced.

### 4.2 The Outer Tracker electronics

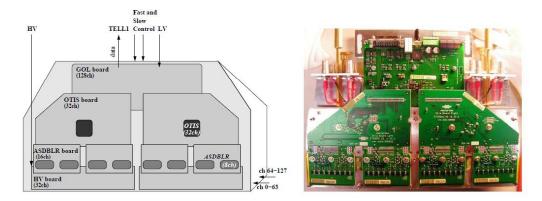

Data acquisition from the straw tubes, especially the drift time, and keeping them functioning are the tasks of the Outer Tracker Front End (FE) electronics. Therefore, special electronics have been built and combined in the so called Front End Box. As Figure 4.5 illustrates, the FE Box consists of separate boards, being the HV board, the ASDBLR board, the OTIS board and the GOL board. Each will be explained in the following.

Figure 4.5: Schematics of the OT FE Box with its different electronic boards (left) and a picture of an actual Front End Box [32].

The High Voltage (HV) board is a simple supply unit, which delivers the used high voltage of +1550 V to each straw tube channel. One HV board handles 32 channels, thus four of them are needed in one FE Box.

The Amplifier, Shaper, Discriminator and BaseLine Restorer (ASDBLR) board works as the link between the straw tubes and the Outer Tracker Time Information Sys-

tem (OTIS) board. Each ASDBLR board hosts two ASDBLR chips, with eight channels each. These chips contain the whole analogue signal processing chain. The power of the signal coming from the straw tubes is increased with the amplifier. Afterwards, the signal is shaped to a format the Time to Digital Converter (TDC) can interpret, with the help of the shaper and discriminator. Finally, a baseline restorer stabilises the signal. Two ASDBLR boards are then connected to one OTIS board of which four are arranged in one FE Box.

An OTIS<sup>IV</sup> board holds one radiation-hard OTIS TDC chip. This TDC chip is capable of digitising the incoming signals of the ASDBLR chips in steps of 0.4 ns and thereby creates a digital drift time value for each channel. The determined data is stored in a pipeline memory capable of storing the data for 4.1 µs. On a positive Level-0 trigger drift times from three consecutive bunch crossings are merged and transferred to a derandomising buffer.

Data from the buffers of four OTIS boards are then sent to the back end electronics, called the Trigger Electronics Level 1 (TELL1), via the Gigabit Optical Link (GOL) auxiliary board. Besides providing the data connection to the off detector electronics, the GOL board handles the power connection and the interfaces to the fast and to the slow control<sup>V</sup>.

## 4.3 The Outer Tracker performance

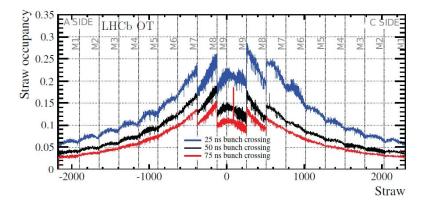

The Outer Tracker showed an excellent performance during LHC run I. The modules had an average occupancy of 3% to 15% as seen in the black curve in Figure 4.6, representing a 50 ns bunch crossing theme in the LHC. This occupancy is shown for typical run conditions in 2011 and 2012. After the upgrade, the occupancy for the 25 ns bunch spacing could be exceeded due to a higher multiplicity in LHCb events. But the shown occupancy can give an assumption to the estimated detector occupancy [32] after the upgrade.

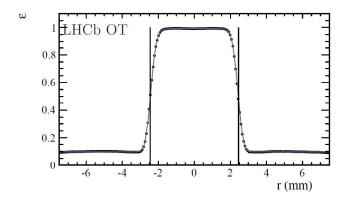

Another crucial aspect in detector performance is the hit efficiency. The vast majority of the OT modules have a hit efficiency between 98.5% and 99.7%, for hits within a radius smaller than 1.25 mm around the anode. The hit efficiency within a straw tube can be seen in Figure 4.7 and is located above 50% inside the whole straw tube.

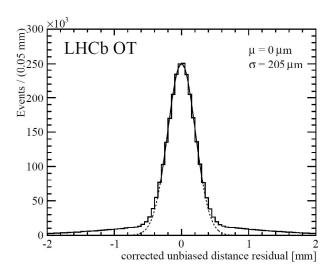

Since the OT is a tracking detector and used for the reconstruction of particle tracks, the hit resolution has to be well known. The design specification for the hit resolution of the OT was  $200\,\mu m$ . As the residual plot in Figure 4.8 shows, a hit resolution of

<sup>&</sup>lt;sup>IV</sup>The OTIS works on a Low Voltage Differential Signaling (LVDS) basis. LVDS is a voltage standard as described in ANSI/TIA/EIA-644-A.

<sup>&</sup>lt;sup>V</sup>The fast control provides the electronics with continuous signals, like the LHC clock, whereas the slow control writes and reads registers to control the electronics.

Figure 4.6: Straw occupancy versus straws for 75 ns (red), 50 ns (black) and 25 ns (blue) bunch crossing spacing in LHCb [32]. The lower occupancy in modules M8 and M9 is explained by shorter modules due to the IT.

Figure 4.7: Hit efficiency ( $\varepsilon$ ) versus radius (r) [32]. The bars indicate the border of the straw tubes.

205 µm was achieved in the 2011/2012 data taking period. This resolution is due to internal construction accuracy and subsequent offline alignment procedure. Hereby, errors occur from the straw accuracy in the modules ( $\pm 50 \,\mu\text{m}$ ), the accuracy with which the modules are hung inside the C-frame ( $\pm 50 \,\mu\text{m}$ ), the frame positioning ( $\pm 1 \,\text{mm}$ ) and the error on the optical survey ( $\pm 0.2 \,\text{mm}$ ) [32].

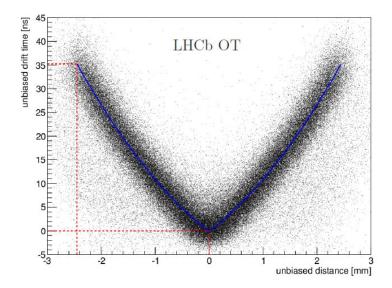

To get a proper distance out of the measured drift times a distance to drift time relation is needed. Figure 4.9 shows the distance to drift time relation with the shape of a second order polynomial distribution. The drift time calibration is done four times a year and the current calibration is found to be:

$$t_{\rm drift}(r) = 20.5\,\mathrm{ns} \times \frac{|r|}{R} + 15.85\,\mathrm{ns} \times \frac{r^2}{R^2},$$

with r as the distance of the hit from the anode and  $R=2.5\,\mathrm{mm}$  as the tube radius.

#### 4 The Outer Tracker and its upgrade

Figure 4.8: Events versus corrected unbiased distance residual [32]. The distance error and thereby the resolution of the detector is about  $205\,\mu m$ .

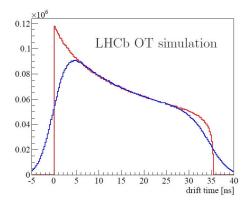

The red lines in Figure 4.9 indicate the maximum possible drift time with 35 ns. This equals the maximum of the simulated OT drift time spectrum shown in Figure 4.10a. However, the highest measured drift time was about 50 ns (see Figure 4.10b). This difference is due to the timing of the front end clock, which is not calibrated for each module separately, and the time of flight of the particle, starting at the interaction point, which again is assumed the same for each module.

Except for the occupancy, all<sup>VI</sup> of the mentioned aspects should not be affected by the LHCb upgrade with a higher luminosity and a higher multiplicity. Therefore the only part of the OT which has to be upgraded due to the new trigger design will be the electronics.

VIThe distance to drift time calibration will still be done a few times per year, and therefore the values will change.

Figure 4.9: Unbiased drift time versus unbiased distance [32]. The distance to drift time relation is calculated with this information.

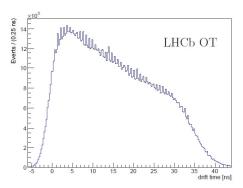

(b) A measured OT drift time spectrum.

Figure 4.10: The Outer Tracker drift time spectrum [32].

## 4.4 The Outer Tracker front end electronics upgrade

The tracker upgrade foreseen for the Outer Tracker would contain reusing the current straw tubes. Therefore, the main interest in development is the upgrade of the OT electronics, which consists of the front end electronics, handled in this section and the back end electronics, for which the firmware was developed in this thesis, explained in detail in Chapter 5. There are two options for the Outer Tracker Front End electronics upgrade, both using the current HV- and ASDBLR-boards and replacing the other parts. Anyway both options would zero suppress the data taken before sending it to the back end to reduce the bandwidth usage. This means, that only the data of hit channels is send to the back end, compressed at the beginning of the stream, while the rest of the data stream is filled with the next taken data.

#### 4.4.1 The MicroSemi option

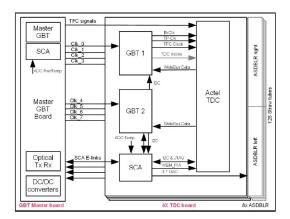

The MicroSemi<sup>VII</sup> option is under development by a group at NIKHEF<sup>VIII</sup>. It is based on an Actel Proasic3E flash based FPGA<sup>IX</sup> and uses a similar setting as the actual FE Box. The GOL board will be replaced by a Master GigaBit Transceiver (GBT) board, which will perform the same tasks the GOL board does at the moment. Besides forwarding the GBT information from the TDC boards to the off detector electronics, the Master GBT board hosts the power converters for the whole FE Box and a Slow Control Adapter (SCA). As Figure 4.11 illustrates an additional GBT for the fast control, called Timing and Fast Control (TFC), and the slow control is implemented on the Master GBT board to provide a connection to the overall controlling systems. These include the slow control for the configuration of the FE and the TFC, which provides the FE amongst others with the LHC-clock and Bunch Crossing Identification (BxID) information. The OTIS boards will be replaced by TDC boards. These will include the TDC FPGA, two widebus GBTs and an SCA. Each FPGA will contain a 32 channel TDC, which generates a five bit drift time with a resolution of about 780 ps. To decrease the bandwidth at the GBTs a zero suppression will be performed on the FPGA.

Additional tasks are monitoring and performing the TFC and slow control commands. The GBTs are used for sending the data out of the TDC board and the SCA performs as another control instance.

VIIMicroSemi is an FPGA manufacturer formerly known as Actel.

VIIINIKHEF: National Institute for Subatatomic Physics, which is located in the Netherlands (National institute voor subatomaire fysica).

$<sup>^{</sup>m IX}$ The difference between flash based and SRAM FPGAs will be discussed in Chapter 6.

Figure 4.11: MicroSemi based upgrade plans as developed at NIKHEF [33]. This scheme with four TDC boards and a Master GBT board would replace the actual OTIS and GOL boards.

#### 4.4.2 The Altera option

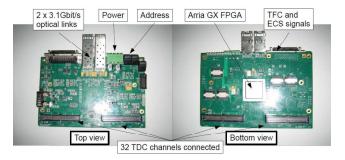

The Altera<sup>X</sup> option was developed at the Ruprecht-Karls-Universität Heidelberg [34]. The tested FPGA was an Static Random-Access Memory (SRAM) based Altera Arria I. This FPGA solution includes transceivers (transmitter and receiver) capable of sending the data as fast as the GBT chip in the MicroSemi option. Thus, no Master GBT board would be needed as every task would be performed not only on a single board, but also just on one FPGA for 32 straw tube channels. The TDC with a resolution of about 780 ps as well as the transceivers can be implemented on the FPGA along with the monitoring, the zero suppression and the interpretor for the TFC and slow control. Figure 4.12 shows a preliminary version of such a board, which has already been used for radiation tests and could be used in the OT upgrade with small adoptions in board design and functionality.

Figure 4.12: Altera based upgrade plans as developed at the Ruprecht-Karls-Universität Heidelberg [34]. A similar board could replace an OTIS board, whilst the GOL functions would be included.

<sup>&</sup>lt;sup>X</sup>Altera is an FPGA manufacturer mainly known for their Stratix and Arria devices.

## 5 The LHCb back end electronics upgrade

The LHCb upgrade requires an upgrade of the whole back end electronics. The current LHCb electronics is designed to process incoming data with 1.1 MHz, whereas the requirement after the upgrade will correspond to an average of 40 MHz [25]. Due to this, a new back end electronics architecture is being developed. In the following, this electronics architecture upgrade will be discussed, whereat the information is taken from [35], [36] and [37], unless indicated otherwise.

## 5.1 The back end electronics upgrade structure

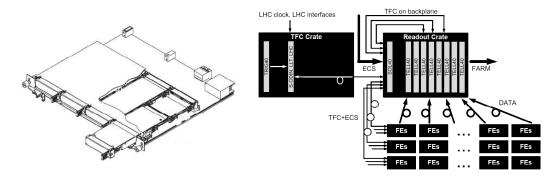

The back end electronics is located off detector in a dedicated room outside the radiative detector area, where no radiation hardness of the electronics is required. Therefore, the commercial Advanced Telecommunications Computing Architecture (ATCA) standard will be used<sup>I</sup> [35]. Positioned inside an ATCA crate, the back end electronics will consist of an ATCA carrier board with four Advanced Mezzanine Card (AMC) slots, as shown in Figure 5.1. A special ATCA carrier board, the ATCA40<sup>II</sup>, is being developed to acquire the needs for the LHCb upgrade. With AMC40s for different functions, the ATCA boards get different purposes, determined by the AMC40 firmware. For example a TELL40 board would be an ATCA40 carrier board equipped with four AMC40s programmed for data acquisition. An example for a complete setup, which is able to take data, is shown in Figure 5.1. It is built of a TFC<sup>III</sup> crate including a TRIG40 and a S-ODIN board and a readout crate built up of TELL40 boards able to process data coming from the FEs and sending them to the farm. Further information about the boards is given in [36], whereas the data processing version of the AMC40s will be discussed in the course of this thesis.

<sup>&</sup>lt;sup>I</sup>Commercial components reduce costs in research, development and production and are therefore favoured.

<sup>&</sup>lt;sup>II</sup>The 40 in ATCA40 refers to the naming convention of the upgraded back end electronics to correlate to the 40 MHz readout scheme and differentiate it to the actual TELL1 back end electronics.

<sup>&</sup>lt;sup>III</sup>The upgraded TFC is also called S-TFC to distinguish it from the current electronics, whereas the "S" stands for "Super".

Figure 5.1: An outside view of an ATCA carrier board with four AMCs is shown on the left [35]. On the right a schematic view of a complete ATCA40 setup is illustrated [37]. A TFC crate with a connected readout crate, to which FEs are connected.

### **5.2 The ATCA40**

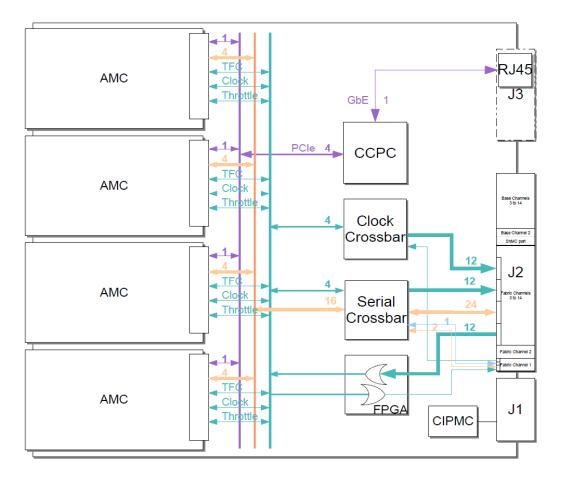

The ATCA40 is a specialised ATCA based carrier board for the LHCb upgrade. As Figure 5.2 implies, four AMC40 boards can be equipped on an ATCA40 and connected via different electrical lines guided to different parts on the ATCA40. Besides basic voltage supply, the ATCA40 carries devices to interact between the AMC40s and the backplane and therefore other electronics inside the same crate.

The Credit Card Personal Computer (CCPC) is linked via four Peripheral Component Interconnect Express (PCIe) buses to the AMC40 boards and with a Gigabit Ethernet (GbE) link to the outside of the board. The CCPC reads and writes registers on the AMC40 FPGAs and connects to the Electronic Control System (ECS) through the Ethernet interface. The clock crossbar allows to route clock signals between the AMC40s and the backplane of the ATCA40 board, and from AMC40 to AMC40. It is used for transferring the LHC clock synchronously to all AMC40s. The serial crossbars purpose is to route high speed signals between the AMC40s, an additional connection to the backplane enables an exchange of signals between AMC40s on different ATCA40 carrier boards. A part of the transferred signals are not defined in advance, because every AMC40 configuration uses a different format to interact with other AMC40 boards of the same configuration IV. The only predefined signal is the TFC signal, which carries the commands for every AMC40 configuration in the same format. Additionally, a general purpose FPGA is positioned on the ATCA40 board, whose main task is to concatenate the throttle information and send it to the AMC40s. The last active part on the ATCA40 is the CIPMC. This controller allows changing the AMC40 boards without rebooting the ATCA40 and collects sensoring information from the AMC40 boards via the Intelligent Platform Management Bus (IPMB).

<sup>&</sup>lt;sup>IV</sup>These signals are called X FPGA in Figure 5.3.

Figure 5.2: Schematic view of an ATCA40 board, with four AMCs connected [35]. All data carrying electrical lines are shown as well as the connectors to the backplane of the crate. Additionally, the active working parts are indicated. There are the CCPC, the Clock Crossbar, the Serial Crossbar, an FPGA and the CIPMC.

## 5.3 The AMC40

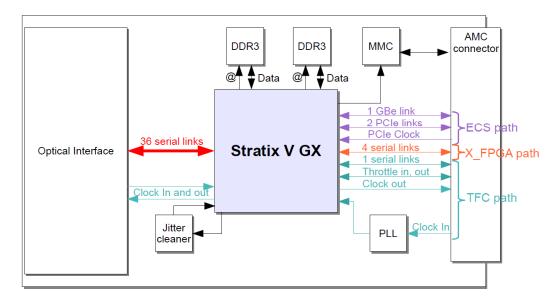

The AMC40 boards are connected via the AMC connector with different protocols to the ATCA40 carrier board as already described. Figure 5.3 shows a simplified architecture of the AMC40. The main component on the AMC40 is the "Stratix V GX" FPGA. The FPGA performs nearly every active part on the AMC40, including the data processing in a TELL40 configuration, which will be explained in detail for the OT in Section 7.2. The FPGA is connected to every other part on the AMC40, which are the optical interface, the Random Access Memory (RAM), a Module Management Controller (MMC), the AMC connector, a Phase Locked Loop (PLL) and the jitter cleaner.

<sup>&</sup>lt;sup>V</sup>The Stratix FPGA series is a product of Altera Corporation.

Figure 5.3: A schematic view of the AMC40 architecture [35]. The AMC40 is centred around the Stratix V GX FPGA. The optical interface ensures the connection to the FEs, whereas the AMC connector does the same to the ATCA40, via the described links. The other parts seen in the illustration are supporting parts and described in this chapter.

Hereby, the RAM consists of two blocks of DDR3 RAM of a still undecided size with a maximum interface speed of 667 MHz. Its main purpose is to buffer data for the TELL40 configuration of the AMC40. The optical interface is made of three twelve-channel transmitters and three twelve-channel receivers from Avago<sup>VI</sup> able to handle data at up to about 10 Gbps. It is connected via 36 bidirectional serial links to the Stratix V so that each of the 36 optical links can be converted from optical signals outside the board to electrical signals on the board, the FPGA is able to interpret. The MMC assures the interface with the Intelligent Platform Management Interface (IPMI) bus, which allows exchanging AMC40 boards without rebooting the ATCA40 and communicates with the CIPMC on the ATCA40. The jitter cleaner is a support circuit which reduces the amount and strength of jitters on the connections of the FPGA to the other parts on the AMC40. Hereby, a jitter is to be understood as a fluctuation in the flank of a digital signal as shown in Figure 5.4.

Figure 5.4: An example for a jitter in a flank of a digital signal. The flank in the dark green signal could vary in the green area, which would be called a jitter.

VIThe used transceiver will be an Avago AFBR-77D1Z.

## 6 Field Programmable Gate Arrays

FPGAs are Integrated Circuits (IC) containing programmable blocks and connections, which in contrast to Application-Specific Integrated Circuits (ASICs) can be configured after manufacturing the chip. FPGAs are often used in R&D, as the ability to be reprogrammed allows an extensive testing and changing of its behaviour, for which an ASIC had to be realised as a new chip in hardware. So custom made electronics can be equipped with an FPGA and the logic on this FPGA can be tested and varied through the whole electronics lifetime. In electronics for large experiments FPGAs are preferred, due to their possibility of being enhanced and debugged during the experiment's lifetime.

Due to the fact that the work of this thesis is done on FPGAs and the extensive use of FPGAs in particle detector electronics, a short introduction shall be given in this chapter. After a short introduction into FPGA technologies, internal structures of an FPGA are explained, followed by an explanation of the typical working procedure with FPGAs.

## 6.1 FPGA technologies

Different basic FPGA technologies are used in modern electronics. Most of them are only one-time programmable, like Fuse, Antifuse, Programmable Read-Only Memory (PROM) and Erasable Programmable Read-Only Memory (EPROM), and only used in specific cases, like low cost serial production or in extreme environments (e.g. under high radiation). Three reprogrammable FPGA technologies are SRAM, Electrically Erasable Programmable Read-Only Memory (EEPROM) and Flash, whereas Flash based memory is an advancement of EEPROM [38]. While EEPROM memory has to be erased completely before being rewritten, Flash memory is capable of being erased partially. Thus, the two most promising memory technologies, SRAM and Flash, will be discussed in the following, whereas the information in this chapter is taken from [38], [39] and [40].

FPGAs are basically built of transistors and working as Integrated Circuits (ICs). Since the connections between those transistor blocks are programmable, it is necessary to save the information for the FPGAs usage inside the transistor environment. So the main difference in technologies is the used memory.

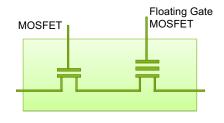

SRAM is a volatile memory, whereas volatile means, that the stored information is lost at losing the FPGA voltage. An SRAM based programmable cell is built of an SRAM memory and a transistor, which is set through the information stored inside the SRAM memory, as Figure 6.1a illustrates. The SRAM memory, in its simplest way, works as an electronic flip-flop as it can be build of NAND elements in Figure 6.1b. There are more advanced versions of used flip-flops in SRAM memories, information about these can be found in [39] or [40].

(a) An SRAM cell inside an FPGA. The SRAM memory defines the status of the transistor. Depending on the information stored inside the SRAM the transistor opens or closes and defines the connection as logical "1" or logical "0".

(b) A NAND flip-flop as possible memory in an SRAM. This flip-flop can only serve as a one bit memory, more complex ways to store information inside flip-flops can be found in [39] or [40].

Figure 6.1: SRAM memory structure.

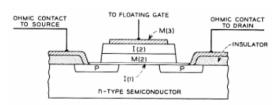

As already mentioned Flash memory has the same working procedure as EEPROM, with the ability to delete smaller parts. Therefore, the raw functionality will be explained with an EEPROM. A schematic view of an EEPROM cell is shown in Figure 6.2a. It consists of two transistors, a normal Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) and an EEPROM transistor (a floating gate MOSFET). A floating gate transistor is usable as a non-volatile memory unit. The floating gate can be programmed to keep the transistor open or closed by adding charge to the floating gate or removing it. A schematic view of a floating gate transistor is given in Figure 6.2b. Detailed information on using floating gate transistors can be found in [41], also more complex variations of floating gate usage can be found in [39] and [40]. Both technologies are used in current FPGAs, depending on the aim of their final use and cost. In Section 4.4 research on FPGAs with both technologies has already been mentioned. Especially the radiation hardness is of high interest and investigated for the OT FE electronics upgrade. Detailed information about the research in radiation hardness on the FPGAs intended for the OT FE upgrade can be found in [33] and [34].

- (a) An EEPROM cell as it can be used inside an FPGA. The floating gate MOSFET is capable of staying open or closed, whereas the MOSFET in front of the floating gate is capable of erasing the floating gate MOSFET.

- (b) Schematics of a floating gate transistor as invented by D. Khang [41]. Modern floating gate MOSFETs still use a similar setup.

Figure 6.2: EEPROM memory structure.

#### 6.2 FPGA structures

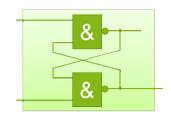

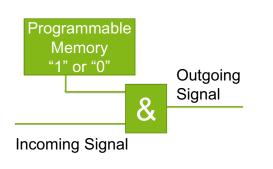

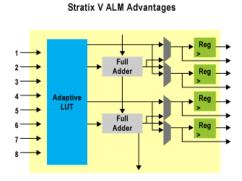

Simple defined bits, respectively opened or closed transistors, will not provide any action since they will not change without reprogramming. Combining these fixed bits with more transistors, logic and connections inside and to the outside of the FPGA leads to combinatorics which can perform defined actions. An easy example is given in Figure 6.3a. Depending on the programming of the "Programmable Memory" the incoming signal can manipulate the outgoing signal. If the memory is programmed to be "0" the outgoing signal will remain "0", programmed as "1" the outgoing signal will be the same as the incoming signal. This is a simple example how a Look-Up Table (LUT) can be created, manipulated and used (in this case it is the simple LUT of an AND logic). This can be enhanced to bigger LUTs, with a definable number of input and output signals and various logic functions or combinations. The combination of LUTs, logic and transistors as a block is named and used differently among FPGA vendors. For example, Altera calls their combination Logic Element (LE) or Adaptive Logic Module (ALM) depending on the device family. A Stratix V ALM block diagram is shown in Figure 6.3b<sup>I</sup>.

The other important configurable parts of an FPGA are the reprogrammable interconnections. With the help of this feature the programmed blocks can be connected in any desired combination. So each outcome of an LE can have an impact on any other used LE and therefore develop huge and complex logics. A simple generic architecture with four programmable FPGA LEs and interconnections is shown in

<sup>&</sup>lt;sup>I</sup>Since the FPGAs used within this thesis are made by Altera their nomenclature will be used.

Figure 6.4. Modern FPGAs are built of thousands of these structures<sup>II</sup> and are able to perform a large amount of actions.

(a) A simple example for a programmable Logic Element. Depending on the programmed value inside the memory the outgoing signal behind the AND-logic is set to zero or the value of the incomming signal.

(b) A block diagram of a Stratix V ALM [42]. It consists of eight inputs with an adaptive fracturable LUT, two embedded adders and four dedicated registers.

Figure 6.3: Logic elements inside an FPGA.

Figure 6.4: A top-down view of a simple generic FPGA architecture, with four LEs (green), five programmable interconnections (darkgreen) and the connecting lines between them (orange).

FPGAs are logic driven instances. Thus, a change on one signal changes the outcome. However, a clock driven logic is preferred. This means, that an external or internal quartz or another kind of clock provides the FPGA with a never-ending signal of alternating logic "1" and "0". The signal is changed with a specific frequency, which is measured from one rising flank to the next. So a distance of 25 ns between two

<sup>&</sup>lt;sup>II</sup>The Stratix V GX 5SGXEA7, which will most likely be used on the AMC40 boards, consists of 938,880 registers and 234,720 ALMs, which would be an equivalent of 622,000 LEs [43].

rising edges would represent a clock frequency of 40 MHz. The clock frequency can be changed by logic inside the FPGA, but the principle of performing actions on a change of the clock remains. Since every logic is stored inside the LEs, the manipulated signals are sent from one block to another each clock cycle. Thus, every step programmed inside the FPGA is performed exactly at the same time each clock cycle, if not programmed otherwise.

## 6.3 Working with FPGAs

Developing a firmware for an FPGA is done in several steps: Coding, simulation, synthesis, programming and testing. These steps will be explained in the following.

The logic on an FPGA is described with a specific Hardware Description Language (HDL). The most widely used HDLs are Verilog and VHSIC Hardware Description Language (VHDL)<sup>III</sup> as they are standardised in the IEEE Std 1364-2001(Verilog) [44] and IEEE Std 1164-1993(VHDL) [45]. The language of choice in this thesis is the VHDL IEEE 1164 standard. This standard defines representative values for driving logic. The most significant ones are the two strong values "1" and "0", which are seen as logic "1", high or true, and "0", low or false. Based on this binary encoding and pairing multiple signals, every bit of data can be decoded to a higher level, like numbers (binary to decimal) or even alphabetical symbols using binary American Standard Code for Information Interchange (ASCII)<sup>IV</sup>. This variable interpretation of bits and bit vectors as boolean or values can drive decisions and be formed to logic serving for nearly every occasion. To keep track of all functions implemented inside the code, small functionable blocks are programmed. These blocks are called "entities" and consist of an entity declaration and an architecture. The declaration includes the input and output ports and their width and optional generics, in principle everything that connects to the outside of the entity. A simple example is given below.

```

ENTITY example IS

GENERIC (

example_value : std_logic := '0';

example_counter : std_logic_vector(3 downto 0) := "0000");

PORT (

clk : in std_logic;

reset : in std_logic;

counter_input : in std_logic_vector(3 downto 0);

counter_output: out std_logic_vector(3 downto 0);

overflow : out std_logic);

END ENTITY;

```

IIIVHSIC stands for Very High Speed Integrated Circuit.

<sup>&</sup>lt;sup>IV</sup>ASCII is a character encoding scheme for 128 specified characters including the alphabet.

The declaration in this example consists of two parts, a list of generics and a list of ports. First the generic list will be explained along with some syntax. This generic list consists of two "generics", named example\_value, a "std\_logic" type, and example\_counter, a "std\_logic\_vector" type. The vector is generated with a width of four bit by (3 downto 0), whereas the definition downto sets the counting of the single bits. A downto vector is initialised with the index of the highest number (in this case "3") on the left, so that the vector can be read as a binary combination v, whereas a to vector is initialised and read vice versa. The := interpreter sets a default value if no value is set from outside the block when it is initialised. The generics are then accessible from the outside of the block and a defined value can be assigned for each instance of this block.

The port list is the most important part of an entity description. It declares the incoming and outgoing signals and their width. The port list in the given example consists of three inputs (clk, reset and counter\_input), symbolised by the declaration in, and two outputs (counter\_output and overflow), symbolised by the declaration out. Hereby the clk signal will be used as the clock driving this block. With the declared ports and generics a simple adder will be programmed in the architecture (the behaviour) of the block, shown below.

```

ARCHITECTURE behaviour OF example IS

signal temp : std_logic_vector(4 downto 0) := "00000";

BEGIN

adding : process (clk)

BEGIN

IF rising_edge(clk) THEN

IF reset = '1' THEN

counter_output <= "0000";</pre>

overflow <= '0';</pre>

temp <= "00000";

ELSE

IF example_value = '1' THEN

temp <= std_logic_vector (unsigned('0' & example_counter)</pre>

+ unsigned('0' & counter_input));

ELSE

temp <= '0' & counter_input;</pre>

END IF;

counter_output <= temp(3 downto 0);</pre>

overflow <= temp(4);</pre>

END IF;

END IF;

END PROCESS;

END ARCHITECTURE;

```

The first step inside the architecture, after naming and assigning it, is to declare the internal used signals, which in this case is the five bit wide vector temp. Afterwards,

VThe binary combination is read as:  $2^3$   $2^2$   $2^1$   $2^0$ .

BEGIN marks the beginning of the code to be processed. Next, a process is defined (adding), which is performed each time the signal in its sensitivity list experiences a change in its value (in this case the clk). An architecture may have any number of processes with the same, different or various sensitivity signals. The first if-statement checks whether the change on the signal clk is a rising edge from "0" to "1"(rising\_edge{clk}). Not deciding on an edge, rising or falling, would perform the assigned logic at each change in signal, and thereby work with the double clock frequency. Then, the reset signal is checked and each outgoing and internal signal set to zero, by a positive decision.

Afterwards, the working logic description begins. If example\_value is set to "1" the sum of example\_counter and counter\_input, including a leading "0" is written into the internal signal temp. One could also set this allocation to an outgoing signal. The redefining in unsigned and back to std\_logic\_vector are needed to instruct the compiler to handle the std\_logic type as numbers. If example\_value is set to "0" only the value of counter\_input is set to temp with a leading "0". In the next clock cycle, simultaneously with the temp-setting logic, the stored value in temp is set to counter\_output and the fifth bit is sent out in the overflow signal.

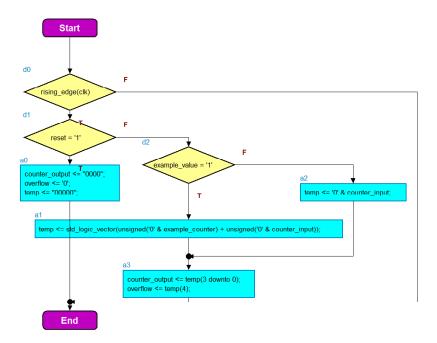

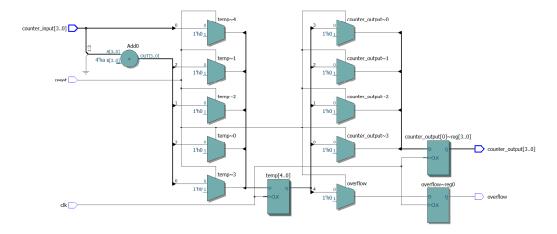

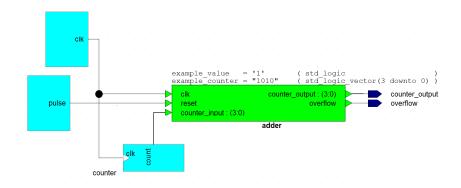

This code example will be used to explain the compilers behaviour. The code can be visualised as a block with inputs and outputs, as it is shown in Figure 6.5, and combined with other blocks by connecting their signals. A software like the used "HDL Designer" can interpret this code and visualise it as a flowchart as it can be seen in Figure 6.6. The code is then "synthesised" by a software of the manufacturer VII. This means it is translated into logic and adapted to the FPGA considering special needs of the preset FPGA. Along the way an optimisation is performed, which tries to minimise the used logic, by analysing the code. The generated logic equivalent to the example code is visualised in the Register Transfer Level (RTL) and shown in Figure 6.7. Afterwards, the produced file can be programmed on the FPGA and is ready to be used.

```

example_value = '0' (std_logic example_counter = "0000" (std_logic vector(3 downto 0))

clk counter_output: (3:0) overflow counter_input: (3:0)

adder

```

Figure 6.5: The example code visualised as a block one level above the code.

To test the written code two possibilities are given, which both should be used. The first one is to simulate the code with a specific software VIII. This method allows to

VIHDL Designer is a software developed by Mentor Graphics. The used versions were 2009.a and 2012 b.

$<sup>^{</sup>m VII}$ Altera provides their software Quartus II. Used Versions: 9.0 to 13.1.

VIII The used software was ModelSim developed by Altera.

Figure 6.6: A flowchart of the example code generated by the HDL Designer.

show the value of each signal at every moment during processing. To simulate the built block correctly, stimuli are needed to perform all tasks which would be provided by the FPGA. Figure 6.8 shows a setup which can be simulated. All inputs to the block shown in Figure 6.5 are driven by a simulated stimulus, a clock, a pulse for the reset mechanism and a four bit counter for the input.

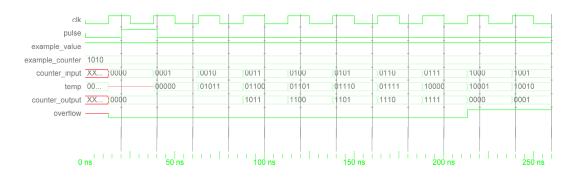

The simulated example code is visualised as signal value over time in Figure 6.9. On the left, the name of the simulated signal is shown, followed by the visualised signal variation over time including the value at that time. On every rising edge of the signal clk the process is executed. The example\_value is added to the counter\_input and stored in the five bit vector temp. On the following rising edge of the clk signal this value is split into the four bit vector counter\_output and the std\_logic value overflow when the fifth bit is needed to display the sum, while at the same time the example\_value is added to the new counter\_input and stored in the temp signal.

If the simulation shows the desired working procedure, the project, without the simulation stimuli, can be synthesised. Beforehand, the input and output ports of the project have to be allocated to the correct pins on the FPGA. During synthesis the code is ported and routed to the characteristics of the used FPGA. The code is also checked for further errors, which did not occur during simulation, and a timing analysis is done. This timing analysis shows if the code can be routed without any constraints to the working procedures in providing data at different blocks to the time expected. With a wrong timing, especially for an ongoing data processing,

Figure 6.7: A view of the RTL generated from the example code by QuartusII.

Figure 6.8: A block diagram of the example code and the stimuli (clock, pulse and counter) to be simulated with ModelSim.

parts of the data could be pulled out of their group and assigned to another.

The then produced file can be programmed onto the FPGA and tested. One way to program an FPGA is via a "joint test action group" connection, which can be established with any serial connection to the FPGA, e.g. USB or RS232. Another possibility is to store the program on a dedicated memory from which it is loaded on startup to the FPGA. There are also different ways to test a firmware on an FPGA. One is to simply put it into action and see if it works correctly. Another way is using a specified testboard or a development kit with indicators or a read out to determine the correct function of the firmware. For example a "Stratix IV GX Development Kit", as shown in Figure 6.10, is used in this thesis. It is equipped

<sup>&</sup>lt;sup>IX</sup>Joint test action group (JTAG) is the common name for the IEEE 1149.1 Standard Test Access Port and Boundary-Scan Architecture.

<sup>&</sup>lt;sup>X</sup>Used kit: Stratix IV GX Development Kit DK-DEV-4SGX230N.

#### 6 Field Programmable Gate Arrays

Figure 6.9: Simulation of the example code for the first 260 ns. The signals without the same name as in the example code are: clk=clock and pulse=reset. On every rising edge of the clock the example code is executed.

with an FPGA<sup>XI</sup>, usable Light-Emitting Diodes (LEDs), a programmable Liquid-Crystal Display (LCD) and a few different Input/Output (I/O) buses, like PCIe. With this I/Os the firmware can be supplied with data to process and the outcome can be observed on a readable device. A few examples of test setups will be given in Chapter 8.

Figure 6.10: Picture of the used Stratix IV Development Kit DK-DEV-4SGX230N.

XIThe DK-DEV-4SGX230N uses the Stratix IV EP4SGX230N-C2.

# 7 The AMC40 firmware for the OT upgrade

The firmware on the AMC40 is split into a common part and a subdetector specific part. The subdetector specific part is declared as "Data Processing" in the following. The common part will be provided by a group at the Laboratoire d'Annecy-le-Vieux de physique des particules (LAPP) in Annecy [46], while the data processing part for the OT is described in this thesis.

The task of the AMC40 and its firmware is to receive data sent from the FEs, process it and then send it out to the DAQ, as already explained in Section 5.3. In the following, the common part will be explained, followed by a detailed view of the subdetector specific data processing part for the Outer Tracker.

## 7.1 The AMC40 common part

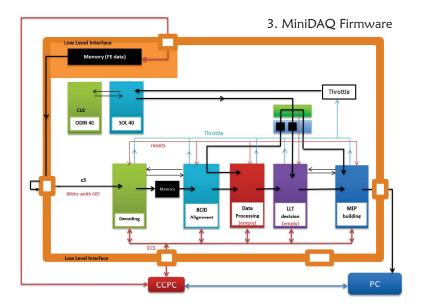

The common part of the AMC40 firmware will be the same for each subdetector. Figure 7.1 gives an overview on the AMC40 design for the MiniDAQ<sup>I</sup>. Excluding the number of links and some additional functions, it resembles the layout of the final design. The purpose of each block, except the "Data Processing", will be explained shortly in the following. The relevant common parts for the AMC40 firmware design, as depicted in Figure 7.1, are "Decoding", "BCID Alignment", "LLT Decision" and "MEP building".

The "Decoding" block searches for the header in the incoming data stream and aligns the data. The BxID<sup>II</sup> and the header are separated and checked for inconsistencies. Afterwards the data is stored in a memory block.

The following "BCID Alignment" is a crucial part to the "Data Processing". Due to different cable's lengths and processing time inside the FEs, the data arrives asynchronous according to the timing on the AMC40 and the bunch crossings respectively. So, the data has to be aligned consistently with the BxID between the different optical link inputs to guarantee a faultless data processing. Furthermore, a timeout has to be performed; if data with the matched BxID from one or more

<sup>&</sup>lt;sup>I</sup>The MiniDAQ is an AMC40 test system and will be described briefly in Chapter 8.

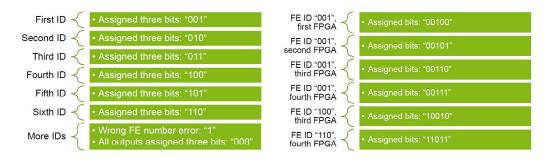

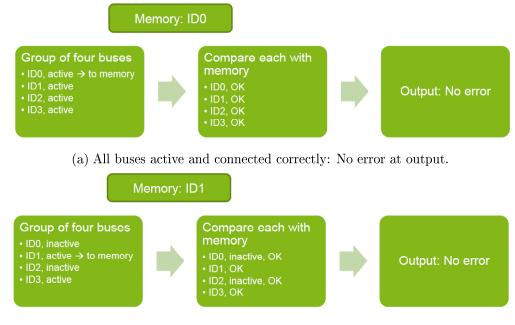

<sup>&</sup>lt;sup>II</sup>Also called BCID as in Figure 7.1.