# Memory-Aware Mapping Strategies for Heterogeneous MPSoC Systems

#### Dissertation

zur Erlangung des Grades eines

### DOKTORS DER INGENIEURWISSENSCHAFTEN

der Technischen Universität Dortmund an der Fakultät für Informatik von

Olivera Holzkamp (geb. Jovanovic)

$\begin{array}{c} {\rm Dortmund} \\ 2017 \end{array}$

Tag der mündlichen Prüfung: 16.03.2017

**Dekan / Dekanin:**Prof. Dr. Gernot A. FinkGutachter / Gutachterinnen:Prof. Dr. Peter MarwedelProf. Dr. Jens Teubner

# Acknowledgments

First and foremost, I would like to express my sincere gratitude to my advisor Prof. Dr. Marwedel for the continuous support and guidance of my Ph.D study and for his patience and immense knowledge. I would also like to thank him for giving me the chance to work in his group and to realize this thesis. Next, I would like to thank Prof. Dr. Teubner for his support and commitment to review this thesis. Furthermore, many thanks to my committee members, Prof. Dr. Heinrich Müller and Prof. Dr. Peter Buchholz.

A lot of colleagues supported me throughout my thesis. Many thanks to Robert Pyka, Markus Buschhoff, Helena Kotthaus, Michael Engel, Andreas Heinig and Florian Schmoll. Robert, Helena and Markus helped me a lot through my thesis with fruitful discussions, proof-reading and motivation. Robert Pyka deserves special thanks for helping me through hard times and always keeping me motivated. In fact, we accompanied each other through all highs and lows during our work. Andreas Heinig, Florian Schmoll, Daniel Cordes and Robert Pyka helped me with technical discussions and technical setup within the MNEMEE framework. I also wish to acknowledge the contribution and cooperation that was provided by the student Nils Kneuper.

Many people outside the department deserve my special thanks. Prof. Dr. Christiane Floyd provided advice and motivation which has been a great help during my work. I would also like to extend my thanks to Iuliana Bacivarov and Sander Stujik for their support and constructive feedback during the planning and development of the tools in this work. Next to Prof. Dr. Marwedel, Prof. Dr. Petru Eles, Dr. Alexandru Andrei and Prof. Dr. Jens Wagner contributed in awakening my interest in research and PhD.

A part of this work was kindly supported by the SFB 876 research project of the Deutsche Forschungsgemeinschaft (DFG). However, a great part was developed within the MNEMEE project, i.e. EC Seventh Framework Program FP7 / IST-216224. The members of these projects deserve special thanks for their kind cooperation, support and the fruitful discussions. Furthermore, the mentoring<sup>3</sup> program initiated by Universitätsallianz Metropole Ruhr (UAMR) supported me with great input, a great mentor and great PhD students. Many thanks to all these institutions for their resources and their guidance.

Last but not least, I wish to thank my family and friends for their support and encouragement throughout my study. Words cannot express how grateful I am to my parents Elica and Stojan, who always believed in me and encouraged me to keep going. My special thanks are extended to my beloved husband Stephan for his support, motivation and all his patience during these years. My mother-in-law Ingrid also deserves my very great appreciation for her support and motivation. I thank all of them for keeping me free of other tasks, so that I was able to finish this thesis.

# Abstract

Embedded systems, such as mobile phones, integrate more and more features, e.g. multiple cameras, GPS sensors and many other sensors and actuators. These kind of embedded systems are dealing with increasing complexity due to demands on performance and constraints in energy consumption. The performance on such systems can be increased by executing application tasks in parallel. To achieve this, multiprocessor systems-on-chip (MPSoC) devices were introduced. On the other side, the energy consumption of these systems has to be decreased, especially for battery-driven embedded systems. A reduction in energy consumption can be achieved by efficiently utilizing the hardware resources on these devices. MPSoC devices can be either homogeneous or heterogeneous. Homogeneous MPSoC devices usually contain the same type of processors with the same speed, i.e. clock frequency, and the same type and size of memories for each processor. In heterogeneous MPSoC devices, the processor types and/or clock frequencies and memory types and/or sizes may vary.

During the last decade, research has dealt with optimizations for the efficient utilization of hardware resources on MPSoCs. Central issues are the extraction of parallelism from sequential code and the efficient mapping of the parallelized application tasks onto the processors of the system. A few frameworks have been developed which distribute parallelized application tasks to available processors while optimizing for one or more objectives such as performance and energy consumption. They usually integrate all required, foregoing steps such as the extraction of parallelized tasks from sequential code and the extraction of a task graph as input for the mapping optimization. These steps are performed either manually or in an automated way. These kind of frameworks help the embedded system designer to significantly reduce design time. Unfortunately, the influence of memories or memory hierarchies is neglected in mapping optimizations, even though it is a well-known fact that memories have a drastic impact on the runtime and energy consumption of the system.

This dissertation investigates the effect of memory hierarchies in MPSoC mapping. Since a thread based application model is used, a thread graph extraction tool is introduced. Furthermore, two approaches for memory-aware mapping optimization for homogeneous and heterogeneous embedded MPSoC devices are presented. The thread graph extraction tool extracts a flat thread graph with important annotations for software requirements, hardware performance and energy consumption. This thread graph represents all required input information for the subsequent memory-aware mapping optimizations. Dependent on the complexity of the application, the designer can choose between a fine-grained and a coarse-grained thread graph and thus influence the overall design time.

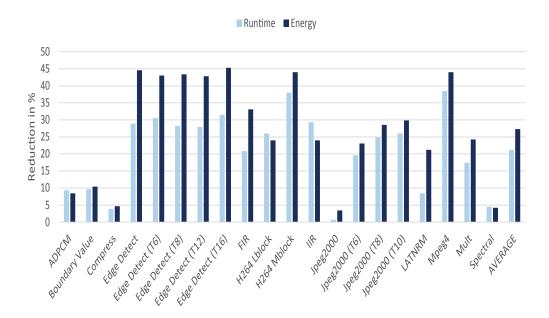

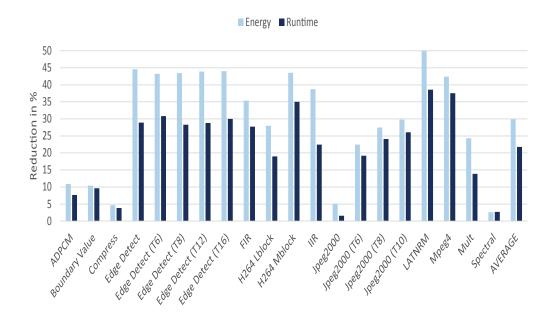

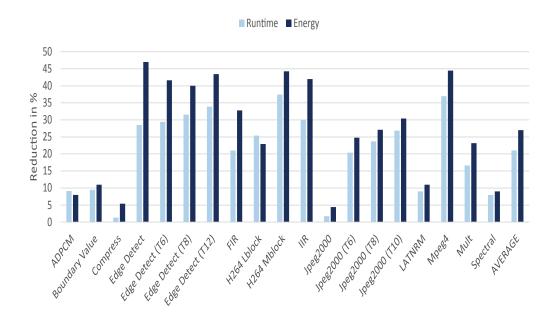

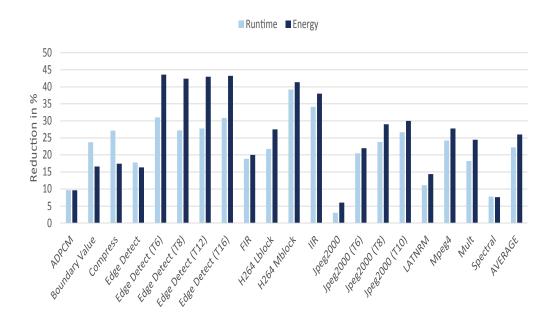

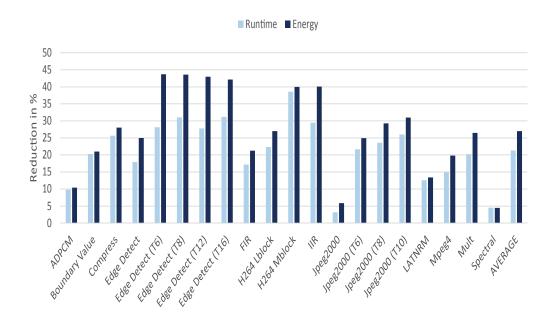

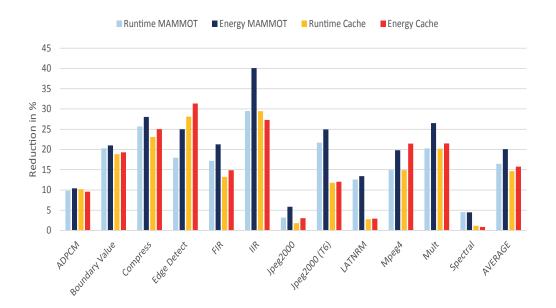

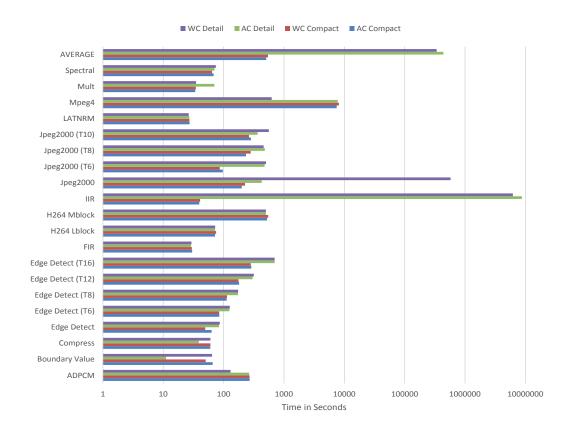

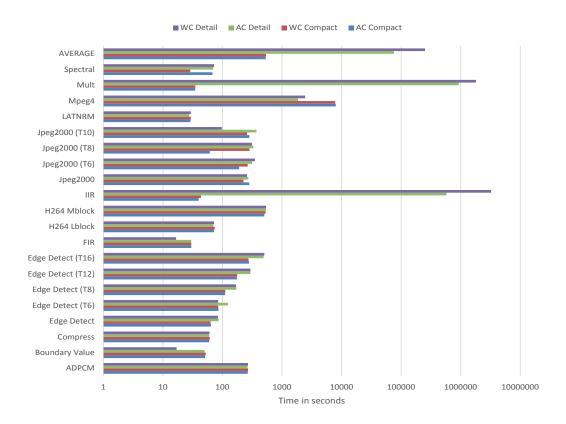

The first presented memory-aware mapping approach handles single objective optimizations, which reduce either the runtime or the energy consumption of the

system. The second presented memory-aware mapping approach handles a multiobjective optimization, which reduces both, runtime and energy consumption. All

approaches additionally reduce the work of the embedded system designer and thus

the design time. They work in a fully automated way and are integrated within the

MACCv2/MNEMEE tool flow. The MNEMEE tool flow also provides all required

foregoing steps such as the parallelization of sequential application code. The presented evaluations show that considering memory mapping during MPSoC mapping

optimization significantly reduces the application runtime and energy consumption.

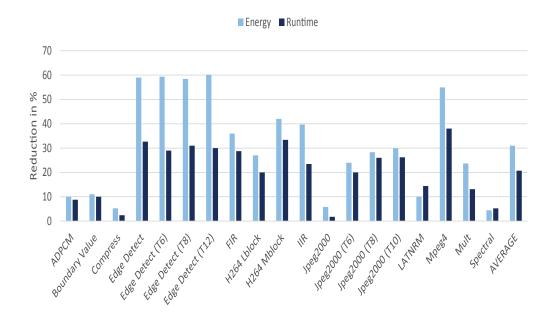

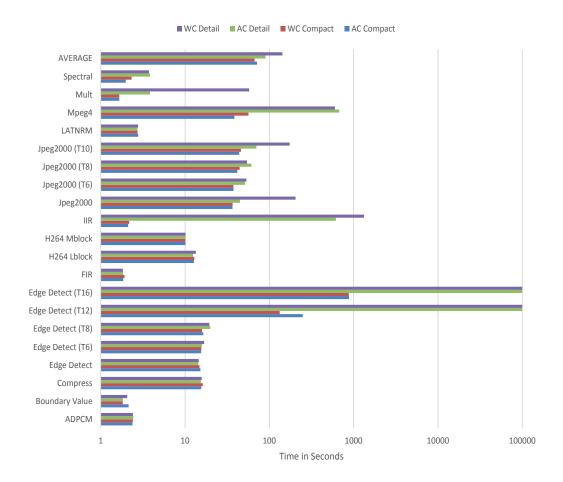

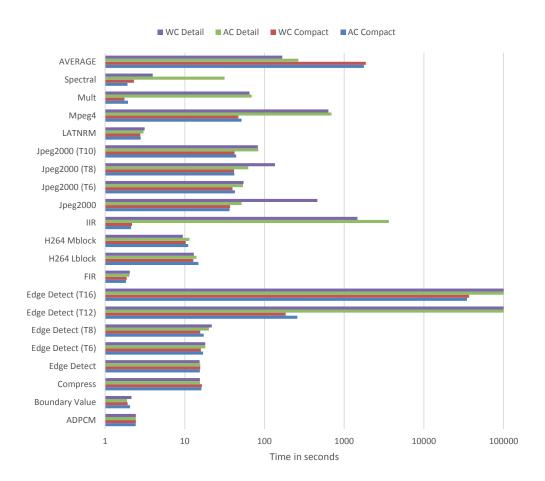

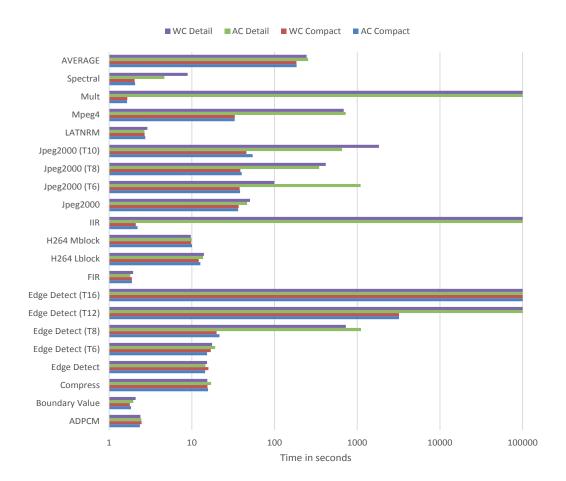

The single objective optimizations are able to achieve an average reduction in runtime by about 21% and an average reduction in energy consumption by about 28%.

The multiobjective memory-aware mapping optimization achieves an average reduction in runtime by about 21% and an average reduction in energy consumption by

about 26%. Both presented optimization approaches were validated for homogeneous and heterogeneous MPSoC devices. The results clearly show that neglecting

the memory subsystem can lead to wasted optimization potential.

# Contents

| 1 | Intr | oductio | on .                                                                                                                       |

|---|------|---------|----------------------------------------------------------------------------------------------------------------------------|

|   | 1.1  | Introdu | ıction                                                                                                                     |

|   | 1.2  | Embed   | ded Systems Architecture                                                                                                   |

|   | 1.3  | Design  | of embedded systems                                                                                                        |

|   | 1.4  | Mappir  | ng problem                                                                                                                 |

|   |      | 1.4.1   | Mapping of memory objects to memories                                                                                      |

|   |      | 1.4.2   | Mapping of application tasks to processors                                                                                 |

|   | 1.5  | Contrib | outions                                                                                                                    |

|   | 1.6  | Outline | a                                                                                                                          |

|   | 1.7  | Author  | rs Contribution to this dissertation                                                                                       |

| 2 | Mo   | dels an | d Tools                                                                                                                    |

|   | 2.1  |         | $\mathbb{C} \mathbf{s}$                                                                                                    |

|   | 2.2  |         | ation and architecture models                                                                                              |

|   |      | 2.2.1   | Memory Architecture Model                                                                                                  |

|   |      | 2.2.2   | Model of Communication                                                                                                     |

|   |      | 2.2.3   | Model of Computation                                                                                                       |

|   | 2.3  | Mappin  | ng Problem description                                                                                                     |

|   |      | 2.3.1   | Architecture Model                                                                                                         |

|   |      | 2.3.2   | Application Model                                                                                                          |

|   |      | 2.3.3   | Mapping Complexity                                                                                                         |

|   | 2.4  | Related | d Work                                                                                                                     |

|   |      | 2.4.1   | Mapping of memory objects to memories                                                                                      |

|   |      | 2.4.2   | Single Core Systems                                                                                                        |

|   |      | 2.4.3   | ${\bf Multiprocessor~Systems/MPSoCs~.~~.~.~.~.~.~3}$                                                                       |

|   |      | 2.4.4   | Mapping of tasks to processors                                                                                             |

|   |      | 2.4.5   | Design Frameworks                                                                                                          |

|   |      | 2.4.6   | Combined mapping to processors and memories 4                                                                              |

| 3 | MN   | EMEE    | 4-                                                                                                                         |

|   | 3.1  | Introdu | $action \dots \dots$ |

|   | 3.2  | The M   | NEMEE toolflow                                                                                                             |

|   |      | 3.2.1   | The MACCv2 Framework                                                                                                       |

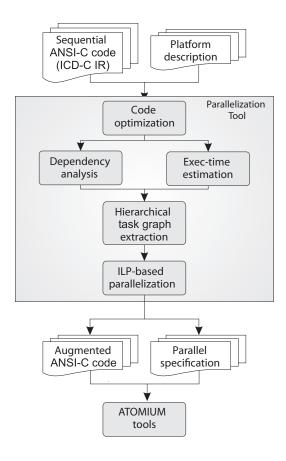

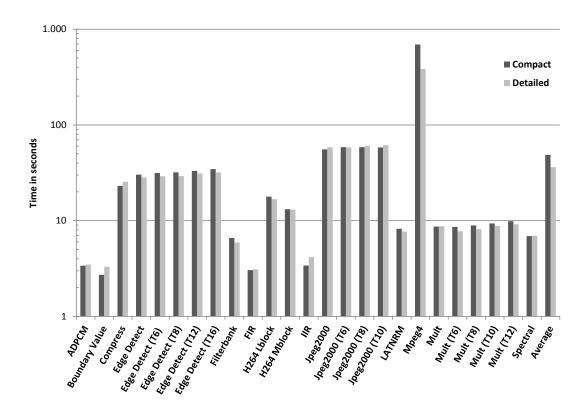

|   |      | 3.2.2   | DDTR Tool (ICCS)                                                                                                           |

|   |      | 3.2.3   | Parallelization Tool (ICD)                                                                                                 |

|   |      | 3.2.4   | MPMH (IMEC)                                                                                                                |

|   |      | 3.2.5   | DMMR (ICCS)                                                                                                                |

|   |      | 3.2.6   | Thread Model Extraction Tool (TUE / IMEC / ICD & TU                                                                        |

|   |      |         | $Dortmund)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                               |

|   |      | 3 2 7   | Mapping Tools 5                                                                                                            |

Contents

|   |                |                                                   | 0 |

|---|----------------|---------------------------------------------------|---|

|   |                | / / / / / / / /                                   | 3 |

|   | 0.0            |                                                   | 3 |

|   | 3.3            | Achieved Results                                  | 3 |

| 4 | $\mathbf{Thr}$ | ead Model Extraction 5                            | 5 |

|   | 4.1            | Introduction                                      | 5 |

|   | 4.2            | Related Work                                      | 6 |

|   | 4.3            |                                                   | 0 |

|   | 4.4            | Tool Overview                                     | 2 |

|   | 4.5            | Safe-Annotation and Simulation                    | 2 |

|   | 4.6            | Thread Model Extraction                           | 4 |

|   |                | 4.6.1 Structure of the Thread Model 6             | 4 |

|   |                |                                                   | 6 |

|   |                | 4.6.3 Constraints                                 | 9 |

|   | 4.7            | Architecture Information                          | 9 |

|   | 4.8            |                                                   | 0 |

|   |                |                                                   | 1 |

|   |                | •                                                 | 2 |

|   |                | 4.8.3 Extracted Thread Models                     | 4 |

|   |                |                                                   |   |

| 5 | Sing           |                                                   | 9 |

|   | 5.1            |                                                   | 9 |

|   | 5.2            | -                                                 | 1 |

|   | 5.3            | - r                                               | 2 |

|   |                | 1                                                 | 2 |

|   |                | r                                                 | 9 |

|   |                |                                                   | 1 |

|   | 5.4            |                                                   | 2 |

|   |                | 5.4.1 Simulation Environment                      | 2 |

|   |                | 5.4.2 Experimental Setup                          | 4 |

|   |                | 5.4.3 Experimental results                        | 5 |

|   |                | 5.4.4 Conclusions                                 | 1 |

| 6 | Moi            | mory-Aware Multiobjective Mapping Optimization 10 | 5 |

| U | 6.1            | Introduction                                      |   |

|   | 6.2            | Tool Overview                                     |   |

|   | 0.2            | 6.2.1 Application specification                   |   |

|   |                | 6.2.2 Architecture Specification                  |   |

|   |                | 6.2.3 Mapping Optimization                        |   |

|   | 6.3            | Optimization Objectives                           |   |

|   |                |                                                   |   |

|   | 6.4            | Evolutionary Algorithm                            |   |

|   | 6.5            | Evaluation                                        |   |

|   |                | 6.5.1 Experimental Setup                          |   |

|   |                | 6.5.2 Experimental results                        | U |

| ${f Contents}$ | X | ч |

|----------------|---|---|

|                |   |   |

|    |        | 6.5.3  | Conclusions             | 12 | 4 |

|----|--------|--------|-------------------------|----|---|

| 7  | Sun    | nmary  | and Future Work         | 12 | 7 |

|    | 7.1    | Summ   | ary and Conclusion      | 12 | 7 |

|    | 7.2    | Future | · Work                  | 13 | 0 |

|    |        | 7.2.1  | Memory-Aware Mapping    | 13 | 0 |

|    |        | 7.2.2  | Thread Graph Extraction | 13 | 1 |

|    |        | 7.2.3  | Design Frameworks       | 13 | 2 |

| Bi | ibliog | graphy |                         | 13 | 5 |

| Li | st of  | Figure | es                      | 14 | 7 |

| Li | st of  | Tables | 5                       | 14 | 9 |

# Introduction

#### Contents 1.1 1.2 2 3 4 4 6 7 1.6 Outline 9 Authors Contribution to this dissertation . . . . . . . . . . . . .

#### 1.1 Introduction

1.7

The process of miniaturization of electronic circuits began with the invention (1947) and distribution of transistors, which replaced large vacuum tubes. The first integrated circuit (IC) was realized 1958 at Texas Instruments where transistors, capacitors and resistors formed an electronic circuit on an area of only few square millimeters. The next important step towards miniaturization and computing power was the introduction of the first, commercial microprocessor Intel 4004 with 2,300 transistors in 1971 [1]. In the following years, the computation power increased while the size of the components and the manufacturing costs shrunk continuously. In 2012, Intel introduced the multicore Xeon Phi Coprocessor with about five billions transistors and up to 62 cores [2].

This increase was consistent with Moore's law, which states that the number of transistors on integrated circuits doubles every two years [3]. In 2010, the International Technology Roadmap for Semiconductors (ITRS) confirmed this trend up to the end of the year 2013 [4]. In 2014, ITRS decided that Moore's law would no longer be followed. Instead, application requirements are the basis of the new "application guided technology" roadmap. Seven focus teams are going to analyze applications and identify new technology requirements. They include heterogeneous components and heterogeneous integration as well as "continued shrinking of horizontal and vertical physical feature sizes to reduce cost and improve performance" |5|

However, the low manufacturing costs of electronic devices and the miniaturization led to a proliferation of special-purpose systems. Contrary to general-purpose systems as personal computers (PCs), special-purpose systems fulfil a specific, customized task. Some examples are smart phones, digital cameras or tablets. These special-purpose systems are defined as embedded systems or as cyber-physical systems

**Definition 1.1 (Embedded Systems)** Embedded systems (ES) are information processing systems embedded into a larger product - Peter Marwedel [6]

**Definition 1.2 (Cyber-Physical Systems)** Cyber-Physical Systems (CPS) are integrations of computation with physical processes - Edward Lee [7]

Cyber-physical system can be also defined as embedded systems in a physical environment [6]. These systems are characterized by their interaction with the environment through information processing with the help of sensors and actuators. Since they are usually also embedded in larger products, e.g. automotive, their presence is less apparent. The main goal of these systems is to make our lives easier or more comfortable. They are already an inherent part of our daily life. We are surrounded by these systems everywhere:

- consumer electronics: television, cameras, tablets, mp3 player, media player, video game consoles, etc.

- telecommunication: smart phone, telephone switches for network, modem / router, USB Internet sticks, etc.

- transportation: automotive (e.g. ABS, airbag, navigation), aircraft (e.g. collision detection), railway, etc.

- household appliance: refrigerator, vacuum robots, washing machine, microwave oven, etc.

- home automation: security, control lights, climate, surveillance, etc.

- robotics, medical equipment, etc.

## 1.2 Embedded Systems Architecture

The progress in hardware development is making embedded systems more efficient, powerful and faster. The hardware progress and the cumulative demands of applications of these systems are a reason for their increasing complexity. For example, the first functions of a mobile phone were short message service (SMS) and telephone service. Nowadays, a smart phone has an integrated camera, internet access, touch screen, GPS, different applications, etc. With the increasing demands, the complexity in the design of these systems has also increased. Furthermore, in the beginning

of embedded systems, the hardware was plain, e.g. consisting of micro controller including memory and input/output functions. Afterwards, systems-on-a-chip (SoC) was introduced where all functions or components of an electronic system are integrated into one circuit, including processors that are more powerful. Nowadays, different hardware architectures are available for embedded systems, from SoCS to homogeneous and heterogeneous multiprocessor system on chips (MPSoCs). MPSoCs integrate multiple processors on a chip, where the processors can be identical (homogenous) or of different types (heterogeneous). Depending on the application area of the embedded system, the hardware has to be chosen properly by the embedded system designer. Some designers work already on a given, fixed architecture, other designers have to design an appropriate architecture.

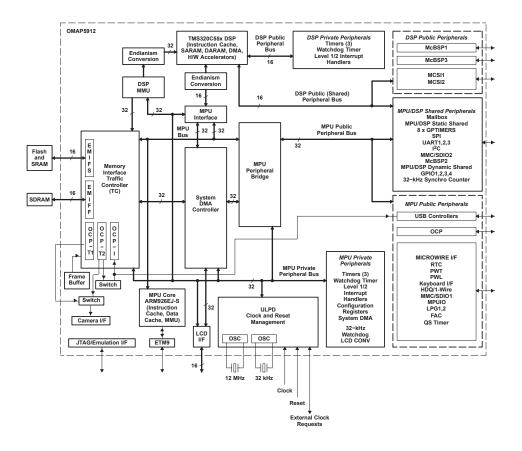

Different terms occur considering concurrent execution: multiprocessor, multicore processor and MPSoCs. A multiprocessor is a hardware architecture containing two or more processing units, which share (main memory and) peripherals. A multicore processor is a processor containing two or more cores or central processing units (CPU), respectively. Both are processing blocks while MPSoCs integrate a complete system solution, e.g. which can contain video and graphics solution [8]. Figure 2.1 on page 13 illustrates a MPSoC, i.e. a functional diagram of the OMAP 5912 from Texas Instruments.

To sum up: In embedded systems, concurrent execution is usually realized through homogeneous or heterogeneous MPSoC systems, which are required in order to satisfy the demands of high-performance computing applications. The development of MPSoCs and state-of-the-art systems are described in more detail in Section 2.1.

## 1.3 Design of embedded systems

For the design of embedded systems, different design steps have to be performed including optimizations, e.g. for the reduction of runtime, energy consumption, code size, bus traffic, etc. Next to these different optimizations, the designer has to face various other challenges, e.g. managing concurrency and also meeting the main demands such as security, robustness, safety, timing aspects, dependability, reliability, availability, maintainability, decrease hardware and software costs of design, etc. In a first step, the designer has to decide which application model, specification language and hardware or hardware description are suitable for the characteristics of the system that has to be designed. Afterwards, optimizations can be performed for hardware (e.g. dynamic voltage scaling, utilize memories and buses, etc.) and software (e.g. code optimizations). All these design steps confront the designer with huge and complex tasks, which have to be accomplished as fast as possible due to time-to-market constraints. Time-to-market constraints define the time of a product from design until its availability for sale. With an earlier release of the new system, the industry gains advantages in competition and market share. In the last decade, MPSoCs and the resulting requirement to manage more and more concurrency as

well as the therefore resulting increasing performance and functionality demands on these systems increased the complexity for embedded system design even more.

Different optimization tools are introduced in research for the different design steps. However, these tools frequently cannot be connected to each other for many reasons. For example, the tools work on different internal models for application and architecture specification due to the manifold models that are existing for embedded systems. Even if the tools work on the same models, it is not guaranteed that the optimization tools can interconnect. Due to different interfaces, the output does not fit to the input of other design optimization tools or the internal data structures of one tool does not fit to other tools, respectively. Here, the designer has on the one side help in form of an optimization tool, which speeds up the design time and decreases the complexity. However, on the other side, now the designer has either to take care of the interconnection of different tools or design an optimization tool on his/her own, which can be connected to another optimization tool.

In both cases, this means again a huge delay in design time. Another problem, which occurs during design time, is the proper analysis and validation of the optimizations on the system. For this, cycle-accurate simulators are required in order to obtain valid results. However, the setup of these simulators, including the setup of the operating system and the interconnection with the underlying synchronization and communication library (e.g. OpenMP, MPI) are a very time-consuming job, which requires a lot of knowledge in these fields. Moreover, an energy and runtime model has to be available for the chosen architecture. It is very difficult and time-consuming to obtain all these energy and runtime values. These issues confront the designer and the researchers with huge timing and management problems. For this reason, research is also concentrating on the automated integration for the different design optimization steps. Some frameworks, which integrate the most important design steps, were introduced. An overview of these frameworks is given in Section 2.4.4. The development and updating of these frameworks is taking years, and their scope can fill several PhD theses.

# 1.4 Mapping problem

In this section, two important design optimization steps are introduced. Both optimizations solve an allocation problem where software (application threads or memory objects) has to be efficiently mapped onto the hardware (processing elements or memories). These optimizations optimize for a single objective goal or for several objective goals as the reduction of energy consumption or runtime.

#### 1.4.1 Mapping of memory objects to memories

The mapping of memory objects to memories is an important optimization that is often neglected during design. Memories or the memory subsystem have a drastic influence on the system's runtime and energy consumption due to the still existing memory wall problem [9]. This problem describes the huge gap between the speed

of processors and the speed of memories. The speed of processors grows much faster than the speed of memories. Thus, the access time to memories limits the performance and memories consume a lot of energy. In a SoC, the access to the main memory can take up to 100 cycles. This problem is also valid for MPSoC systems where the access time to off-chip DRAM also consumes a great amount of time.

Memory hierarchies were introduced in order to cope with this significant problem by placing smaller, faster and more energy-efficient memories (i.e. on-chip memories) close to the processor, building a memory hierarchy with one or more levels. The idea is to place frequently used instruction or data memory objects onto on-chip memories and thereby to reduce runtime and energy consumption. For example, an on-chip memory on level-1 is located next to the processor and has ideally only one cycle access time. On-chip memory on level-2 are also common. There is a larger distance between the level-2 memory and the processor. Dependent on this distance, the access time increases as well as the energy consumption compared to the access and energy consumption to the level-1 memory.

On-chip memory hierarchies either consist of cache or scratchpad memories. Especially in the design of real-time embedded systems, scratchpad memories are extensively used [10]. The content of these memories is known in advance. They are predictable with respect to runtime and energy consumption. These advantages are achieved because they are explicitly allocated by the application designer or an optimization software, respectively. Furthermore, they consume less energy and die area than caches since no additional hardware in the form of control logic is required for the management of their content. For these reasons, we explicitly consider only scratchpad memories instead of caches.

Due to the drastic influence of the memories on runtime and energy, intelligent algorithms or optimizations are required in order to map efficiently the most accessed memory objects onto the memories. Important achievements in this research field is described in Section 2.4.1. Next, some trends in the memory hierarchy of MPSoCs are introduced, which will lead the research in a new direction with new challenges in the memory mapping optimization.

The trends in MPSoC systems show that level-1 and level-2 caches are common. One example is the Exynos Octa 5410 architecture, which contains two level-1 and one level-2 cache for each processor. Another trend is the heterogeneity in the memory hierarchy. For example, the OMAP architecture contains usually a GPU and an ARM processor. In the OMAP 5912, the ARM926EJ processor has access to a 16 KB instruction and to a 8 KB data cache. The TMS320C55x DSP core has access to a 64 KB on-chip dual-access RAM, a 96 KB on-chip single-access RAM and a 24 KB instruction cache [11].

The OMAP 5430 includes a dual-core with two ARM Cortex-A15, a DSP subsystem with a TMS320DM64 DSP processor and an image-processing unit (IPU) subsystem. Each Cortex-A15 core contains a separate instruction and data cache of 32 KB and both cores have access to a level-2 cache of 2 MB. The DSP has access to a level-1 32 KB cache and a 128 KB level-2 cache. The dual-core Cortex-M4 in

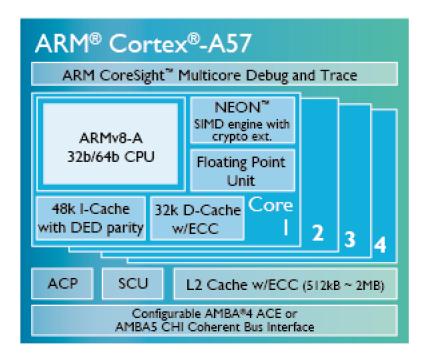

Figure 1.1: ARM Cortex-A57<sup>1</sup>

the IPU subsystem has a shared access to level-1 32 KB cache and a shared level-2 64 KB cache and a 16 KB ROM. Also, a multicore GPU architecture is integrated with two SGX544 cores containing a shared system-level cache of 128 KB [11].

The ARM Cortex-A57 processor can have a more heterogeneous memory hierarchy containing a 48 KB instruction cache and a 32 KB data cache, as illustrated in Figure 1.4.1. The level-2 caches can have a size from 512 KB to 2 MB.

These real-world examples show the upcoming trend of heterogeneity in the memory subsystems in MPSoC systems. A more detailed overview of MPSoCs is given in Section 2.1. A classification of MPSoC systems concerning their memory organization is described in Section 2.3.1.

### 1.4.2 Mapping of application tasks to processors

The design step of mapping of application tasks onto the processing elements of the architecture has evolved from the development of parallel execution in hardware architectures. The goal is to efficiently map parallel application tasks in order to achieve an increase in performance or in order to decrease the energy consumption.

The preceding step is a parallelization, which is performed either manually by the designer or automatically by special parallelization tools. After this step, the former sequential application or parts of this application are split into several tasks, which can be executed in parallel. These tasks can have the same workload, different

<sup>&</sup>lt;sup>1</sup>Image reproduced with permission of the rights holder, ARM Ltd.

workloads, or a mixture of both. This depends on the application, its types of operations, access patterns, complexity, etc. Moreover, the type of parallelization performed on the application influences the workload of each task (pipeline, loop-level, etc.). After the parallelization, the mapping optimization has to distribute these tasks efficiently. For this, the characteristics of the underlying architecture have to be considered, as the number of processors and the characteristics of each individual processor (e.g. clock rate, energy consumption). The complexity and solution/design space for this optimization increases if two or more contradicting objective goals are considered. In research, this design step was also immensely explored. Related work of this topic is described in Section 2.4.4. As already stated in the previous Section 1.2, the trends in MPSoC design go towards heterogeneity and towards heterogeneous processors and thus to the mapping of tasks to these processors.

#### 1.5 Contributions

Research tries to alleviate the burden of the designer by introducing different optimization techniques for the diverse, complex design steps. This thesis focuses on memory optimizations in homogeneous and heterogeneous MPSoC systems. It combines two separately considered optimizations into one optimization step since state-of-the-art MPSoC architectures require this combined view in order to utilize the full optimization potential. Usually, two optimization steps are performed. One optimization step is the mapping of concurrent application threads among the processors of a homogeneous/heterogeneous MPSoC. The other optimization step is the mapping of memory objects to a local memory or to different memories in the memory hierarchy. Both are common optimization steps in the design of embedded systems, which try to efficiently utilize the resources of the system.

This thesis gives a more detailed view on the complexity of the combined mapping of the application threads together with their memory requirement onto the architecture's processors and their underlying memory hierarchy in 2.3.3. Since the trend of MPSoC systems goes towards heterogeneous systems with heterogeneous processors and a heterogeneous memory subsystem, this thesis focuses on this kind of architecture. Heterogeneous MPSoC systems increase the complexity of this optimization.

In application to processor mapping, the focus lies only on the characteristics of the processors (e.g. speed, energy consumption, type). Due to the drastic influence of the memory wall problem on runtime and energy, it is crucial to consider the underlying memory hierarchy. The architecture resources have to be matched to the application's requirements, or vice versa. This thesis focuses on this matching. Focus is laid on both, the architecture and application characteristics with the goal to efficiently utilize the system resources in order to achieve a high optimization potential. The optimization goals are the reduction of energy consumption and/or runtime.

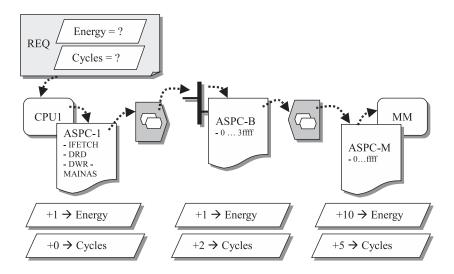

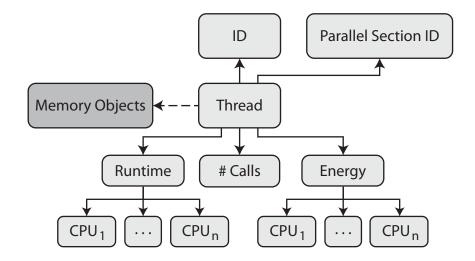

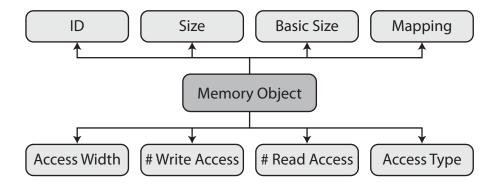

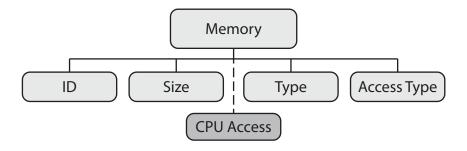

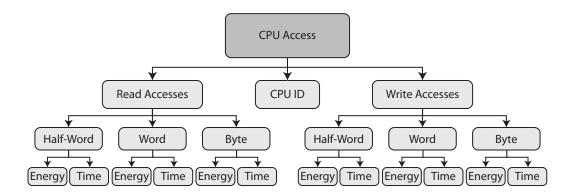

The thesis concentrates on the extraction of a detailed analysis model for all introduced optimization. On the architecture side, the processor's energy consumption for active and idle mode is included as well as the performance capability. Since processors have access to their underlying memory hierarchy with different memories on different levels, these are captured in detail as well. All memories have various characteristics as size, type (instruction, data or unified). Furthermore, access speed and energy consumption differ depending on the access type, i.e. read or write access and access width (Byte, half-word, word). The characteristics of the underlying buses, that are accessed, are also considered. On the application side, the characteristics of the application threads have to be considered in detail, i.e. workload of a thread and thus all requirements of the memory objects as size, type of memory object (data or instruction), number of read and write accesses, etc. Furthermore, communication between threads is considered as well, taking into account the data send over a communication channel (i.e. data size, number of data send, etc.). All this information is taken into account for the optimization and analysis model. It is verified against cycle-accurate simulation.

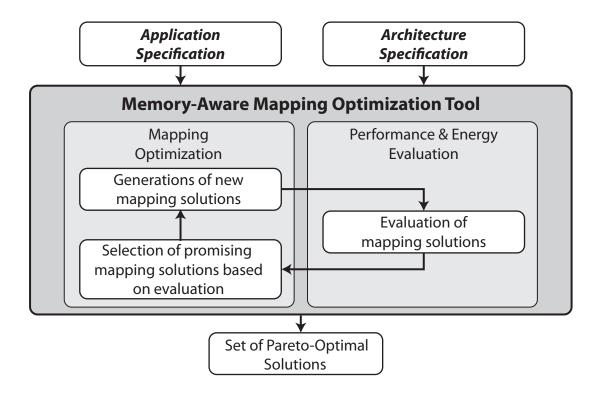

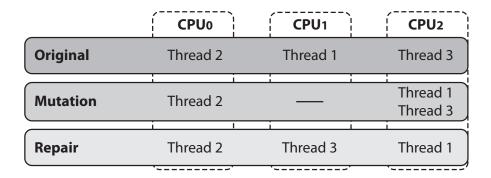

For the separate consideration of either the reduction of runtime or energy consumption, an integer linear programming (ILP) optimization is introduced. Furthermore, a multiobjective optimization for the reduction of runtime and energy consumption at the same time is also introduced. All optimizations are available as separate tools, which can be used by designers, dependent on the designer's system requirements. Both optimizations use the detailed analysis model. An evolutionary algorithm is used for the multiobjective memory-aware mapping optimization. It generates a set of mapping solutions by crossover and mutation. These solutions are evaluated and generated in a design space exploration loop. At the end, a set of mapping solutions is provided as solution.

Another important design step is the extraction of an extended thread graph from parallelized source code. This thread graph extraction gained also attention in research and is handled by this dissertation. This step is performed before the application-to-architecture mapping and is required in order to perform the mapping optimization properly. The challenge is an accurate extraction of a detailed representation of the parallel threads, including dependences as control-flow and data-flow. Furthermore, the mapping tools also require information on threads, which include architectural characteristics, e.g. as the runtime of a thread on different processors or the memory sizes of memory objects, which are dependent on the architecture. All these manifold and additional information have to be extracted and annotated to the thread graph. This extraction is handled by this thesis.

Except for the memory-aware mapping ILP optimization, these optimizations were developed within the EU project MNEMEE with the goal to integrate memory-awareness in the embedded system design and to alleviate the work of the designer by providing an automated tool flow for the complex design optimization steps.

To the best of our knowledge, we are the first, which integrate a homogeneous and a heterogeneous memory subsystem in the optimization step of mapping concurrent threads onto processors.

1.6. Outline 9

#### 1.6 Outline

The remainder of this book is organized as follows:

• Chapter 2 describes the common architecture and application models as well as all underlying models of this work and a more detailed problem description. Furthermore, an overview over the related work is given.

- Chapter 3 presents the EU project MNEMEE including the goals and the description of the fully automated design framework.

- Chapter 4 presents the *Thread Model Extraction Tool* which extracts an annotaded thread graph from parallelized C-Code.

- Chapter 5 describes the *Memory-Aware Mapping Optimization Tool* based on integer linear programming (ILP) for the reduction of energy consumption or for the reduction of runtime, respectively.

- Chapter 6 describes the *Memory-Aware Mapping Optimization Tool* based on an evolutionary algorithm for the multiobjective optimization for energy consumption and runtime.

- Chapter 7 presents the summary of this work and gives an overview over future work.

#### 1.7 Authors Contribution to this dissertation

In §10(2) of the "Promotionsordung der Fakultät für Informatik der Technischen Universität Dortmund vom 29. August 2011", a dissertation has to provide a separate list which presents the author's contribution to research and results in cooperation with other researchers.

Therefore, the following list provides an overview over the contribution of the author on the presented results for each chapter:

- Chapter 2: This chapter describes related work and gives an overview over application and architecture models. Thus, in this chapter the author of this thesis presents research results by other authors.

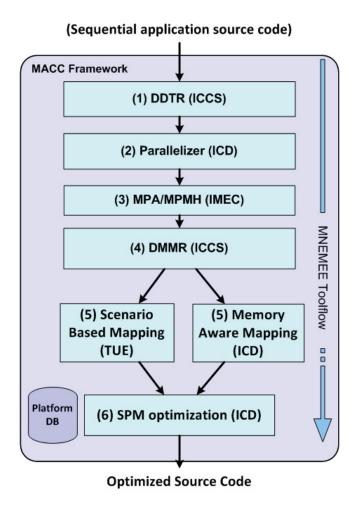

- Chapter 3: The MNEMEE toolflow [12],[13] was created by almost all MNE-MEE partners. However, the main part of the MACCv2 framework [14], which is the basis of the toolflow, was developed by ICD in cooperation with TU Dortmund. The author has also worked on this framework, especially by integrating the tools/optimizatons that are introduced in the next chapters. A great part of the framework is used for analysis, optimization and evaluation of this thesis. All tools within the MNEMEE toolflow are described in publications [12],[13].

- Chapter 4: The *Thread Model Extraction Tool* was developed within the MNE-MEE project [12], [13]. The pre-processing steps of the thread graph extraction were developed in collaboration with IMEC, Sander Stuijk(TUE Eindhoven) and the author. The thread graph extraction itself was entirely developed by the author and is described in detail in Chapter 4.6. The author also integrated the thread graph extraction and 70% of the pre-processing step into the MACCv2 framework.

- Chapter 5: The memory-aware ILP optimizations for the reduction of runtime and energy were developed by the author in cooperation with her master's student Nils Kneuper, who realized the majority of the implementation. About 60% of the ILP formulations were contributed by the author. The resulting publication [15] was written by the author. Guidance and inspiration was provided by Prof. Peter Marwedel. The employed cycle-accurate CoMET simulator was donated by Synopsys Inc. [16]. The implementation of the heterogeneous platform within CoMET and the MACCv2 framework was entirely performed by author.

- Chapter 6: The memory-aware multiobjective optimization was entirely developed by the author and published in [17]. Guidance, inspiration and motivation were provided by Prof. Peter Marwedel and Prof. Lothar Thiele. The initial problem definition was provided by Prof. Marwedel. Iuliana Bacivarov helped with guidance and a lot of fine-tuning in the optimization and implementation. The system-level framework called distributed operation layer (DOL) [18] was used as a basis for the implementation of the optimization. The optimization goals of DOL were exchanged by the author's optimization goals. Furthermore, the author implemented several extension and changes. First, the process network model was exchanged by a thread-based model, which includes parallel sections. The application model was extended to include memory objects and all required characteristics/information of memory objects (e.g. size, number of reads/write, instruction/data/shared, etc.). The architecture model was extended to include more memory characteristics (memory types, energy consumption/runtime for different type of accesses, etc.). The author also performed the integration and interfacing of this tool into the MNEMEE tool flow or MACCv2 framework, respectively. This optimization is also described in [12] and [13] as part of the MNEMEE tool flow.

# Models and Tools

| Contents | S              |                                                |   |

|----------|----------------|------------------------------------------------|---|

| 2.1      | MP             | SoCs                                           | 2 |

| 2.2      | $\mathbf{App}$ | olication and architecture models              | í |

|          | 2.2.1          | Memory Architecture Model                      | 7 |

|          | 2.2.2          | Model of Communication                         | ) |

|          | 2.2.3          | Model of Computation                           | ) |

| 2.3      | Мар            | pping Problem description 23                   | } |

|          | 2.3.1          | Architecture Model                             | } |

|          | 2.3.2          | Application Model                              | Į |

|          | 2.3.3          | Mapping Complexity                             | ; |

| 2.4      | Rela           | nted Work                                      | 7 |

|          | 2.4.1          | Mapping of memory objects to memories          | 3 |

|          | 2.4.2          | Single Core Systems                            | 3 |

|          | 2.4.3          | Multiprocessor Systems/MPSoCs                  |   |

|          | 2.4.4          | Mapping of tasks to processors                 | 3 |

|          | 2.4.5          | Design Frameworks                              | 3 |

|          | 2.4.6          | Combined mapping to processors and memories 41 |   |

|          |                |                                                |   |

The design of embedded systems is a challenging and quite complex task. Consumer demand and improvements in hardware have even increased this complexity. State-of-the-art embedded systems get more and more complex and have to fulfill many aspects such as efficiency (energy, runtime, code, costs), timing aspects (hard/soft deadlines, real-time aspects, etc.), dependability (i.e. reliability, safety, security), etc. [6]. All these aspects must be considered and have to be an integral part in the design flow in order to guarantee the full functionality of the desired system. It is impossible to develop a standard design flow for the abundance of different embedded systems and all their resulting manifold characteristics (i.e. functionality and requirements). Furthermore, the time and effort spent in the design of the system also depends on the characteristics of the desired system. For example, the design of a flight control system in an airplane is much more complex than an electric-driven, classic DVD player. Some of these different systems need the same optimization steps in the design flow. However, since these different systems have

different underlying software and hardware, it can happen that the same optimization problem has to be implemented in a different way with a different approach for different design flows.

Section 2.1 gives an overview over the development of MPSoCs and state-of-theart MPSoCs. Next, Section 2.2 introduces the common application and architecture models in embedded system design. Afterwards, Section 2.3 gives an overview over the considered models for the mapping optimization problem in this work. Related work is presented in Section 2.4.

#### 2.1 MPSoCs

MPSoCs arose from the requirement to perform parallel execution instead of sequential execution in order to achieve an increase in performance. The first area of application was the fast solving of large and complex problems such as weather modeling, simulation of the evolution of galaxies, data mining, etc. This includes all scientific and engineering calculations. The first supercomputer CDC 6600 was invented 1964 in order to solve large scientific problems and to use time sharing for smaller problems. The supercomputer included 10 peripheral processors, each of them containing a small memory for program and buffer area (4096 memory words with 12 bit length). A central processor was also included. All processors had access to a central memory. The first multiprocessor occurred in the 1970s. The Illiac IV processor included four control units, which controlled 64 arithmetic logic units (ALUs). With this multiprocessor, vector and array operations could be performed in parallel. The C.mmp multiprocessor contained 16 processors which were connected to a memory through a crossbar [19]. Also, the occurrence of superscalar, very long instruction word (VLIW) and explicitly parallel instruction computing (EPIC) processors have the common goal to improve performance by the parallel work of a certain number of execution units.

MPSoCs have emerged in the past decade. The architecture design mainly depends on the underlying embedded application. In this section, some representative MPSoCs are introduced. One of the first MPSoC, *Lucent Daytona* was introduced in the year 2000. It contained four CPUs, which were attached to a high-speed bus. Each CPU has a 8 KB 16 banks local memory. Each bank can be configured as instruction/data cache or scratchpad memory. This MPSoC was designed for wireless base stations where identical signal processing was performed on a number of data channels [19].

Another well-known MPSoC for multimedia processing is the *Philips Viper Nexperia* which was designed for advanced TVs, set-tops and home media servers. It consists of two CPUs: a MIPS and a Trimedia VLIW processor. Buses are integrated for each CPU as well as for the external memory interface. The MIPS processor is the master running the operating system, while the Trimedia is integrated as the slave which executes the commands from MIPS. Hardware accelerators performed computations such as color space conversion [19].

2.1. MPSoCs 13

Figure 2.1: TI Omap 5912 - Functional Diagram [11]

The Texas Instruments (TI) OMAP architecture is a well-known MPSoC which was widely used for mobile phones. Many implementations exist for this architecture. For example, the OMAP 5912 implementation has an ARM9 and a DSP processor (TMS320C55x). A functional diagram of the OMAP 5912 is illustrated in Figure 2.1.

Almost all implementations of OMAP contain a (dual-core) ARM processor together with a DSP or PowerVR graphics processing unit (GPU). Another famous MPSoC is the CELL architecture. It contains one 64-bit power processor element (PPE) and 8 specialized synergistic processor elements (SPEs) together with a high-bandwidth bus and a high-speed memory controller. The SPEs consist of a synergistic processor unit (SPU) which includes a 256 KB local memory. All processing elements communicate over a high-speed bus. A direct transfer between the local memories of different SPUs is possible through a DMA controller. The CELL architecture was implemented in the Playstation 3 video-game console from Sony and for some HDTVs from Toshiba. Other application areas such as visualization, image and signal processing, and various scientific and technical workloads are also suitable [19, 11].

The ARM11MPCore is a multiprocessor consisting of one to four (identical)

processors that are known for their low dynamic power consumption and which are often used within MPSoC systems for smartphones. Each processor has a separate instruction and data cache. The sizes for each cache can vary from 16 KB to 64 KB. The Arm Cortex-A processors are the follow-on products of the Arm11MPCore. They also contain separate instruction and data caches on level 1 with different memory sizes from 8 to 64 kB and a shared L2 Cache with sizes from 128 kB to 2 MB. The ARM big.little architecture is actually one of the state-of-the-art MPSoCs. The first-generation architecture consists of one to four ARM Cortex-A15 processors together with one to four ARM Cortex-A7 processors. The second generation of this architecture consists of ARM Cortex-A57 or Cortex-A72 processors together with ARM Cortex-A53 or Cortex-A35 processors. The biq Cortex-A15 can be used for heavy workloads while the *little* energy-efficient Cortex-A7 is used for smaller workloads that have to be accomplished all the time, e.g. operating system activities, user interface, etc. Different variations in the clock rate and the number of coprocessors are available as a quad core with two copies of each processor or also a system with four big and two little processors [20], [21]. This architecture can be used for many computation intensive applications as well as for a mixture of network traffic and computation (e.g. STB, WLAN), for OS GUI environments in netbooks, smartphones etc. Actually (in 2016/2017), this big.little architecture is implemented in state-of-the-art smartphones such as Samsung Galaxy S7 or Samsung Galaxy Note devices within different available Samsung Exynos processor chips.

The Exynos 5 Octa chip (5410/5420) contains four Cortex-A15 cores and four Cortex-A7 cores. Compared to earlier Exynos processors, Samsung claims that it reduces power consumption (by up to 70%) while maximizing performance. The 5410 chip contains a PowerVR SGX544 MP3 533 MHz GPU for console-like 3D games and a 13 Mp 30 fps ISP (Image Signal Processor). The (local) memory sizes are not published yet by Samsung [22], [23].

An existing Exynos Octa 5420 development board is based on Exynos 5 Octa and integrates four Cortex-A15 processors with 32 KB of instruction and 32 KB of data level-1 Cache and a 2 MB level-2 Cache. The four Cortex-A7 processors also include a separate 32 KB instruction and 32 KB data level-1 cache and a 512 KB level-2 cache. A 64 KB ROM for secure booting and 336 KB internal RAM for security functions is included. Other features are a 3D graphic accelerator with multi-core GPU, and a separate 2D graphic accelerator [24].

The Exynos 7 Octa chip (5433/7420) introduced the new ARM Cortex-57 and 53 cores and integrated four Cortex-A57 and four Cortex-A53 cores. In 2016, Samsung maintained the big.little architecture and introduced the Exynos 8 Octa chip containing a custom core CPU by Samsung (based on Armv8) and Cortex-A53 cores [25].

Further processor chips are based on the big.little architecture such as Qualcomm Snapdragon 808 MSM8992 and 810 MSM8994 (two to four ARM Cortex-57, four Cortex A-53 cores in LG, HTC and Microsoft Lumia smartphones) [26], [27] and Nvidia Tegra X1 (four ARM Cortex A57, four Cortex A-53, Nvidia Android TV) [28].

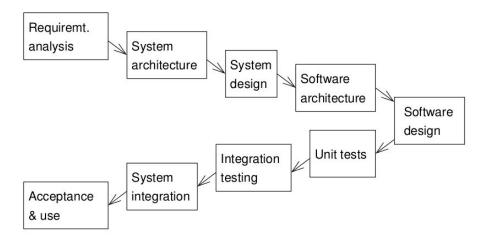

Figure 2.2: V-model (rotated standard view) [6]

To sum up: Different MPSoC alternatives exist which integrate homogeneous or heterogeneous components such as processors and memory subsystems. The modeling of these different systems is described in the next section.

## 2.2 Application and architecture models

Various specification languages, models and design flows exist. The designer is confronted with a huge number of possibilities and has to decide which design flow, specification language or model specifies the behavior and functionality of the desired system properly. Unfortunately, no specification or design flow exists which covers all requirements completely.

The embedded system design includes several steps, which can start from an idea up to the prototype of a system. Typically, the design flow starts with a specification of the system behavior, hardware and software with the aid of models and specification languages. Here, the specification depends on the preliminary infrastructure, i.e.: Is the hardware and/or software (partly) already fixed or is a new hardware or software design required? Based on the infrastructure, the designer has to decide which design flow to choose.

Many design flows exist. If the designer cannot find a proper design flow, he/she can choose an individual design flow which reflects the desirable design steps in the most suitable way. Here, three instances of design flows are introduced, which represent the common steps in the design of embedded systems.

The V-model (version 97) with all required steps is shown in Figure 2.2. The first axis represents the design and implementation phase while the other axis represents the validation and test phase. It is widely used in the German government sector. A

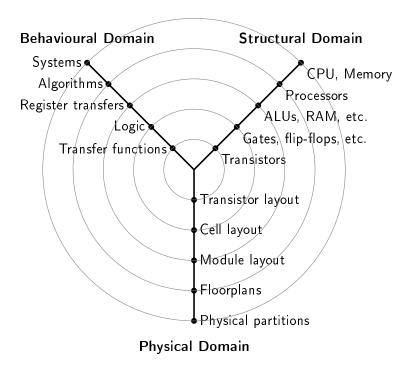

Figure 2.3: Gajski-Kuhn Y-chart

more recent model with better scalability is available with extended and modifiable design steps [29].

Gajski's Y-chart is another well-known flow for hardware design, which is illustrated in Figure 2.3 [30]. This design flow has three dimensions: the behavioral, structural and geometrical dimension. The geometrical layout contains information about chips and the structural layout contains information about hardware components. The abstraction increases from the inner to the outer circle. Each circle and axis defines a model. The high-level model describes the overall behavior while the models on the lower-level describe the behavior of components. Different design paths can be chosen. They are usually performed step by step and typically take their path from a coarse behavioral level to a fine-grained geometrical level.

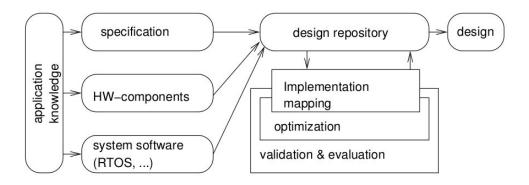

Another design flow, which includes essential design steps, is shown in Figure 2.4 and is taken from [6]. Boxes with rounded corners represent stored information in a design repository. The rectangles represent transformations on data. After the specification of the system behavior, the hardware components and the system software, further design steps and optimizations are required. First, the application tasks have to be mapped onto the execution platform. Different optimizations can be performed during the mapping and afterwards, e.g. high-level transformations, runtime and energy minimization strategies, etc., can be applied. At the end, an evaluation step should be performed in order to evaluate the effect of the different optimizations on the system (i.e. performance, energy consumption, etc.) and to adjust some optimization if necessary. Furthermore, a validation step should check

Figure 2.4: Design flow from Marwedel [6]

the correctness of the design.

However, next to the decision which design flow to choose, also a decision has to be made concerning the hardware and concerning the software model or model of computation, respectively. The model of computation is an abstraction for certain functionality and represents design specifications. No model of computation can meet all specification requirements. Linked to the decision of hardware and software specification, the decision about the parallel programming model is also important.

The decision about the hardware platform depends on the characteristics of the system that has to be designed. Often, the architecture is already fixed since it is reused or only slightly changed from previous designs. In this case, the focus lies more on software design. Even if the hardware is fixed, it is often desirable to model the hardware at another abstraction level because at the validation step, it is less time-consuming to simulate the system and perform optimizations.

Next, a short overview is given over the common hardware (memory / communication models) and models of computation for multiprocessor systems.

#### 2.2.1 Memory Architecture Model

First, different memory architectures for multiprocessor systems exist:

- shared memory architecture (UMA and NUMA)

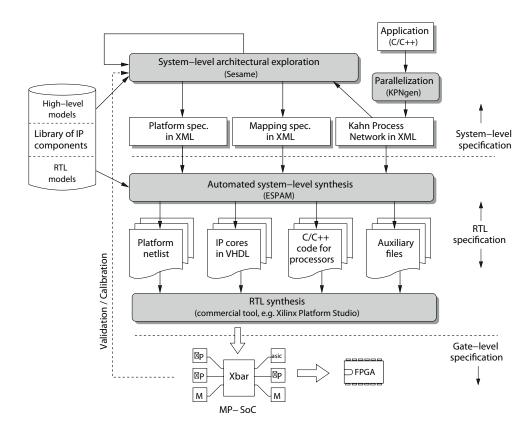

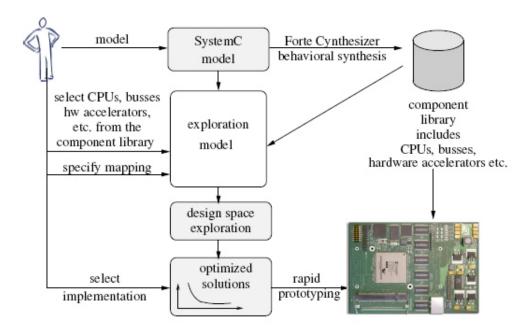

- distributed memory architecture

- hybrid distributed shared memory architecture

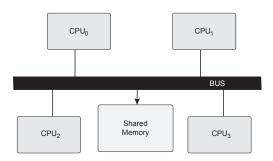

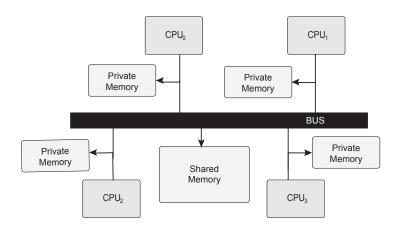

In the shared memory architecture, the processors can access all memory in the global address space [31]. This means, that the memory and all changes made to it are visible to all processors and all processors can change the memory content. The shared memory architecture can be divided into two classes, which differ in the memory access time: UMA (uniform memory access) and NUMA (non-uniform memory access). Figure 2.5 illustrates the UMA shared memory architecture and

Figure 2.5: Shared Memory Architecture (UMA)

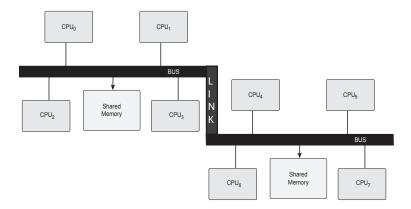

Figure 2.6 shows a NUMA shared memory architecture. The UMA shared memory architecture usually contains identical processors which have equal access time to the memory. The NUMA shared memory architecture often links two UMA architectures together as illustrated in Figure 2.6. The memories are accessible by both sides through the link. Since the access across the link is slower, the memory access times can vary. Contrary to the shared memory architecture, in the distributed memory architecture, each processor has exclusive access to its own memory as shown in Figure 2.7.

A communication network connects the memories of the different processors. If data has to be shared among different processors, the programmer has to define the communication and synchronization. Both memory architectures have their advantages and disadvantages. In the shared memory architecture, there is usually one bus for several processors. Several conflicts can occur on the bus when two or more processors want to access the bus at the same time. This problem increases when the number of processors increase. In the distributed memory architecture, the

Figure 2.6: Shared Memory Architecture (NUMA)

Figure 2.7: Distributed Memory Architecture

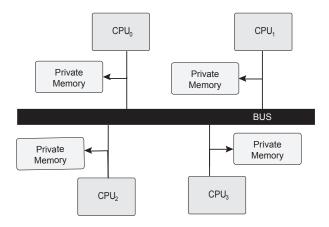

processors can access their memory rapidly without any conflicts. The disadvantage here is that the programmer has to take care for the data communication between the different processors. Also, mapping an existing data structure from a shared memory architecture to a distributed memory architecture is extremely difficult. The shared memory architecture is more user-friendly since the data sharing is fast and in the most architectures uniform. However, the hybrid distributed shared memory architecture combines both memory structures and also the advantages of both. The processors can work on their own memory without any bus conflicts. The access to a shared memory is only performed for access to shared data [31]. An example is illustrated in Figure 2.8.

Figure 2.8: Hybrid Distributed Shared Memory Architecture

#### 2.2.2 Model of Communication

The selection of the hardware influences the model of communication and the selection of the proper model of computation and vice versa. The model of communication can be either shared memory or message passing. Shared memory communication is performed through a common memory which is accessible by all processors. Message passing is performed by sending and receiving messages. It can be also implemented when no common memory is available, but it is slower than shared memory communication. Three different strategies can be implemented for message passing: asynchronous, synchronous or remote invocation. For the asynchronous message passing, the sender can send its messages and a channel buffer stores these messages. The recipient does not need to confirm the received message. In the synchronous message passing, it is contrary to the asynchronous process. Here, the sender and the recipient have to be ready for the communication exchange. In the remote invocation strategy, the sender can only send its message after it has received a confirmation from the recipient [6]. The designer selects the model of computation based on the underlying architecture and communication model.

#### 2.2.3 Model of Computation

The requirements for any design-flow are adequately defined abstraction levels and models. The hardware and software/specification models on any level trade off accuracy for efficiency but alleviate the complexity of the system design specification. On the other hand, models have to be defined with the right amount of detail that will allow rapid and meaningful (design space) exploration, synthesis and validation. These abstraction levels are also valid for the models of computation, which are required for the description of system behavior. The system behavior is specified in a first step. The models of computation impact the design of specification languages.

There are several requirements for specification models: timing behavior, concurrency, reliability, modularity, synchronization, communication, security, etc. Since no model can meet all specification requirements, it is extremely important to choose the appropriate model for a successful design of the system. Different types of models exist: state based, thread based, actor based or data flow models. State based models are usually finite state machines (automata), state charts and timed automata. They describe state-oriented behavior. Timed automata include timing information. The state charts model includes several features such as the modeling of hierarchy (super and sub-states), concurrency (and/or states), history mechanism, etc. Another state-based model is the specification and description language (SDL). The basic elements are processes, which are modeled as finite state machines. Processes also perform operations on data (declarations, assignments, decisions) and are interacting with other processes. For this interaction, asynchronous message passing is performed through FIFO queues where each process has one queue for signals. SDL was standardized by the International Telecommunication Union (ITU). SDL is suitable for distributed applications, and it also has been used for specifying ISDN. However, it is not deterministic. For an implementation, the upper bounds for the length of FIFOs have to be determined. It is not a suitable model for hard deadlines [6].

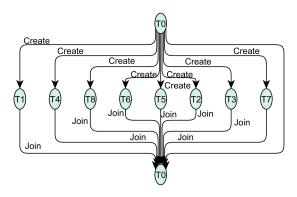

Furthermore, task graphs or process networks can be used to represent dependences between computations, i.e. control- and data-flow between different tasks or processes. Even more detailed task graphs can be selected, which can represent e.g. the amount of data consumed at each edge. Also, an organization as a hierarchical task graph is possible if required by the designer. Task graphs can be used at different steps in the design, e.g. for mapping of tasks to processing units or for aggregation or generation of tasks in the parallelization step.

Further models can be actor-based, such as communicating finite state machines (cfsm) and data flow models such as synchronous data flow graphs (SDF) or Kahn process networks (KPN). Kahn introduced the Kahn process networks (KPN) for parallel/distributed execution [32]. The actors can be implemented as processes in the programming language C. The communication is asynchronous and performed via unbounded FIFO channels. The channels are point-to-point queues with one producer and one consumer per channel. The synchronization is performed via blocking read and non-blocking write. An advantage is that KPNs are deterministic.

A disadvantage is that KPNs are difficult to implement because the size of infinite FIFOs has to be implemented on limited physical memory [33]. Furthermore, too small buffers can lead to an artificial deadlock which has to be resolved at runtime [34].

The synchronous data flow graph by Lee and Messerschmitt is also an actor-based model where the actors are executed concurrently [35]. Each actor produces and also consumes a fixed number of tokens per firing. Let us assume an actor A which produces tokens is connected to an actor B which consumes the tokens of actor A. In a SDF, a balance equation exists for each channel where the number of firings  $f_A$  of actor A multiplied by the number of tokens N produced by actor A is equivalent to the number of firings  $f_B$  of actor B multiplied by the number of tokens M consumed by this actor:  $f_AN = f_BM$ . The communication between the actors is buffered. The data flow is synchronous since all tokens are consumed at the same time. The message passing is asynchronous, i.e. the actors do not have to wait until an output is accepted. SDF can be scheduled statically. The schedule can be determined at compile-time. Furthermore, the buffer memory requirements and deadlocks are decidable problems.

Carl Adam Petri introduced Petri nets in 1962 [36] They model casual dependencies and are suited for message passing. The key elements are conditions, events and flow relations. Conditions can be met or not, and events take place when certain conditions are met. Flow relations relate conditions and events. Petri nets model resources, mutual exclusion and synchronization. Three different kinds of Petri nets exist: condition/event nets, predicate/transition nets and place/transition nets. Condition/event nets are simple nets with only one token per condition. They are a special case of bipartite graphs. With place/transition nets, more than one token per condition is possible. Here, conditions are defined as places, and transitions

represent events. Predicate/transition nets are useful for large condition/events or place/transition nets since they are able to reduce the size of these nets. A famous example used for predicate/transition nets is the "dining philosopher's problem".

Thread based execution is defined within the Von-Neumann model. The Von-Neumann model is characterized by sequential execution. It is still vastly used in many designs since languages as C, C++ and Java are widely spread and many applications were already written in these languages. However, many languages do not provide communication and synchronization mechanisms for the execution on multiprocessor systems. As described in [6], the languages CSP and ADA have already built-in communication. In the remaining languages, the communication is provided by selecting different libraries. Java supports concurrency by using threads. The communication type can be selected by choosing different libraries. In Kahn process networks (KPN), the processes are also executed in a sequential manner. However, the emphasis lies in the communication while the details of the execution within the processes has less emphasis. In data flow languages, the movement of data has the most priority while in von-Neumann-languages the control-flow has more priority. The disadvantage of thread-based models is that they are not deterministic and that through the use of mutexes, deadlocks can occur. Here, the programmer has to take care of deadlocks properly.

Discrete event based languages are VHDL, Verilog and Sytem C. They are usually used in shared memory systems. In discrete event modeling, the events are sorted in a timeline queue by the time at which they are processed. The event is processed at its scheduled time, all corresponding actions are performed, and it is then removed from the queue. Sometimes the event enters new events into the timeline queue. A comparison over models of computations and languages is given in [6].

In a design flow, there can often exist a mixture of different languages or models of computation. An overview over the different models of computation and languages and their references to the different communication models is given in Figure 2.9.

#### Communication libraries

MPI, POSIX threads and OpenMP are among the communication libraries that exist for C/C++. As the name already indicates, the message passing interface (MPI) is used for message-based communication between processors. It allows asynchronous or synchronous message passing. POSIX threads is an application programming interface (API) for threads at operating system level. It provides procedures for thread management (create, join, etc.), synchronization between threads and also for mutexes. POSIX threads are used for shared memory hardware. "OpenMP is a specification for a set of compiler directives, library routines, and environment variables that can be used to specify shared memory parallelism in Fortran and C/C++ programs" [37]. Here, parallelism is expressed with pragmas and it takes the least amount of effort for parallelization for the user. For more information on the libraries, please refer to [6]. For all communication libraries, the programmer has

| Communication/<br>Organization of components | Shared memory            | Messa<br>synchronous               | nge passing<br>asynchronous    |

|----------------------------------------------|--------------------------|------------------------------------|--------------------------------|

| Undefined components                         |                          | Plain text, use cases<br>(Message) | s<br>sequence charts           |

| Communicating finite state machines          | StateCharts              |                                    | SDL                            |

| Data flow                                    | (not useful)             |                                    | Kahn networks<br>SDF           |

| Petri nets                                   |                          | C/E nets                           | , P/T nets,                    |

| Discrete event (DE) model                    | VHDL, Verilog<br>SystemC |                                    | imental systems) DE in Ptolemy |

| Von Neumann-<br>model                        | C, C++, Java             | C, C++, Java<br>CSP, ADA           | , with libraries               |

Figure 2.9: Overview over MOCs and languages considered [6]

to define parallel processes or threads and take care for the accurate communication and synchronization.

### 2.3 Mapping Problem description

This section describes the considered underlying architecture and application models of this work. Furthermore, the complexity of the integration of memory-awareness into the application to architecture mapping optimization is described in more detail. The underlying optimizations that are introduced in this work were mainly developed within the EU-project MNEMEE which is introduced in Section 3. The application and architecture model that is used in this work were specified in cooperation with all MNEMEE partners, based on their requirements and the tools that were already partly provided by these partners.

#### 2.3.1 Architecture Model

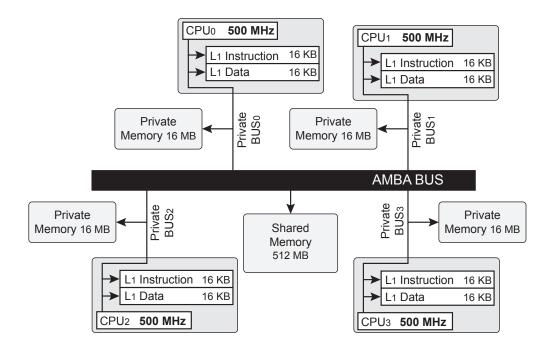

The considered architecture model is based on the hybrid shared distributed memory model. Hence, a shared memory is available, which is accessible by all processors. All shared communication is performed on this memory. Each processor has also exclusive access to its own private memory where instructions and data can be allocated. This prevents conflicts on the bus as in the shared memory architecture, and it also prevents slow communication between the tasks as in the distributed mem-

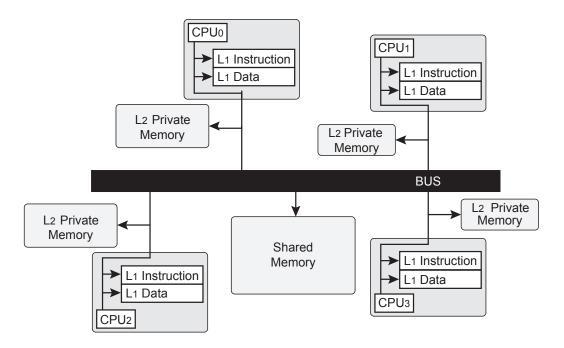

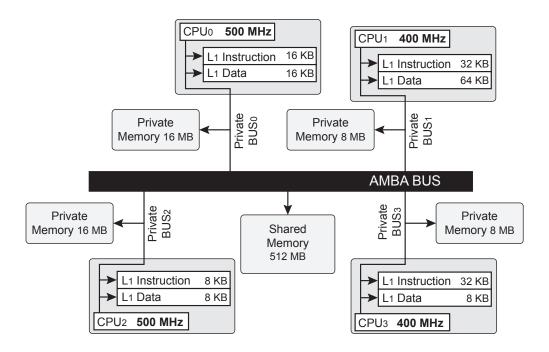

Figure 2.10: Heterogeneous MPSoC architecture with multi-level memory hierarchy

ory architecture. The architecture is already given and fixed and thus it does not have to be designed. The architecture has n processors, which can be homogeneous or heterogeneous, i.e., differ in type and/or clock rate. Each processor can have a distinct memory hierarchy, which can have different hierarchy levels and different sizes on each level. The local memories can differ in memory type (instruction only / data only / unified). Each memory has different energy and runtime values, which depend on type, level and size of the memory. Furthermore, the energy and runtime for bus accesses which lead to the memory have to be considered.

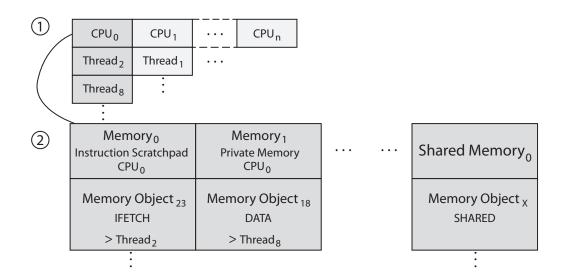

Figure 2.10 illustrates an example architecture. In this architecture, four processors  $CPU_0$ - $CPU_3$  are defined. Each processor has a separate local instruction and data scratchpad memory on level 1 and a private main memory on level 2. The processors have exclusive access to these memories. Furthermore, the architecture has at least one shared memory, which is accessible by all processors and which is used for inter-thread communication and synchronization. The shared memory can be accessed through an on-chip network or bus. Section 2.1 shows that this model is based on state-of-the-art MPSoC architectures.

#### 2.3.2 Application Model

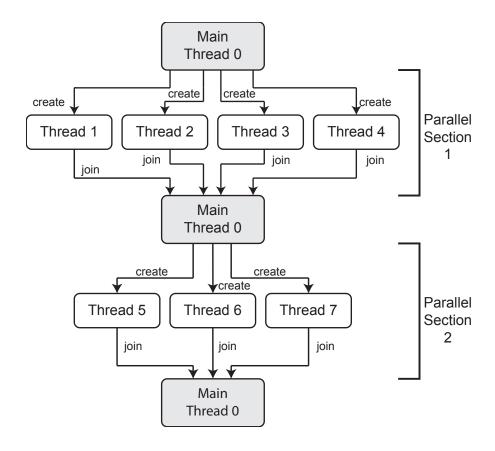

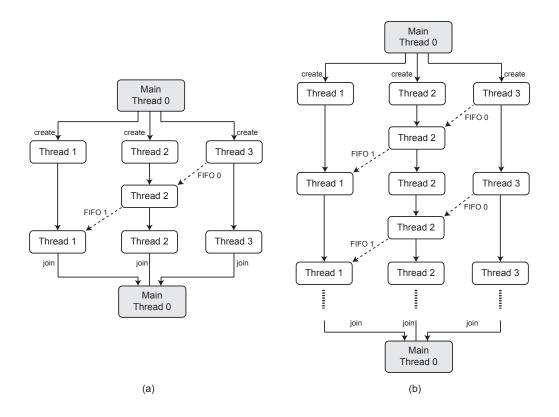

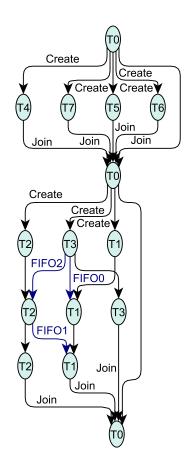

In the application model, it is assumed that an already parallelized application is given. A representation of the application in the form of an acyclic task graph is required for the mapping optimization. A thread-based application model as depicted in Figure 2.11 is used. Here, a main thread accomplishes computation,

Figure 2.11: Thread-based application model

creates new threads and hereby initiates the parallel execution. The newly created threads can run in parallel and communicate via FIFOs. After they accomplish their computation, the main thread joins them and continues its execution. The section where newly created threads run in parallel is called *parallel section*. An application can have one or more parallel sections. An example is illustrated in Figure 2.11. Here, the application has two parallel sections with four threads in parallel section 1 and three threads in parallel section 2. Each thread, including the main thread, has to be mapped onto a processor of the underlying architecture platform. This application model can be generated from existing sequential C-code applications by using automated tools. More details on these tools are given in section 3.2.1.

Each thread consists of memory objects, which are either instruction code or data. They are mainly characterized by their size and the frequency of read and write accesses. The memory objects define the computation requirements of a thread. Depending on the memories they are allocated to, they essentially influence the performance and energy consumption of the system.

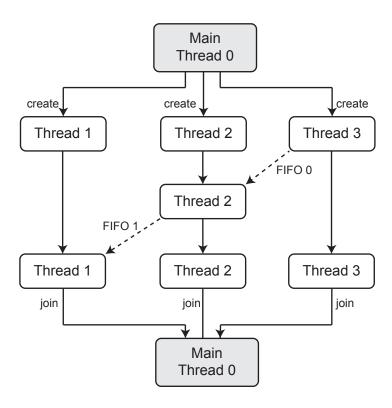

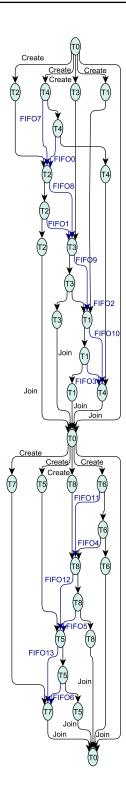

Based on the characteristics of the application, our model can also contain FIFO (First-in First-out) queues for inter-thread communication as depicted in Figure 2.12. In this case, a thread can be composed of several thread nodes. The edges be-

Figure 2.12: Task graph including FIFO communication

tween the different thread nodes illustrate either FIFO (i.e., communication) edges or control flow edges. As shown in Figure 2.12, the second node of thread 2 cannot proceed its execution until thread 3 has written something into the FIFO. This specification ensures a more precise determination of runtime since a thread node cannot be executed until all predecessor nodes have finished their execution or communication, respectively.

#### 2.3.3 Mapping Complexity