# Memory-aware platform description and framework for source-level embedded MPSoC software optimization

# Dissertation

zur Erlangung des Grades eines

Doktors der Ingenieurwissenschaften

der Technischen Universität Dortmund an der Fakultät für Informatik

von

Robert Pyka

Dortmund 2017

Tag der mündlichen Prfung: 16.03.2017

**Dekan / Dekanin:** Prof. Dr.-Ing. Gernot A. Fink Gutachter / Gutachterinnen: Prof. Dr. Peter Marwedel Prof. Dr. Jens Teubner

# Acknowledgements

It is my pleasure to acknowledge the roles of several people who were instrumental for completion of this work.

First and foremost, I would like to thank my advisor Prof. Dr. Peter Marwedel for providing me with the opportunity to work on my PhD thesis in his group. I acknowledge his unwavering support over the last few years, his guidance and advice in so many discussions. He gave me the freedom to pursue my work in the most interesting direction, while contributing his vast knowledge and advice to shape this thesis into a valuable contribution to the research community. I have learned a lot from him, far beyond what can ever be concluded in a dissertation. I would also like to acknowledge all the helpful suggestions from my co-reviewer Prof. Dr. Jens Teubner and the committee members Prof. Dr. Heinrich Müller and Prof. Dr. Peter Buchholz.

Among all my former and current colleagues, I would like to mention in particular Felipe Klein, Florian Schmoll, Olivera Holzkamp and Daniel Cordes. They have been the most involved MACCv2 users and contributors. They spent countless hours on fruitful discussions and provided numerous improvement suggestions, bug reports and actual implementation contributions. Many personal thanks go to Olivera Holzkamp. She is the one who has always found the right words to keep me going and finalize this thesis. I am also indebted to Manish Verma for providing the initial inspiration to this work. A special thanks goes also to Rowena Worsley-Potthoff as well as to Michael Engel for their support, reviews and valuable comments and improvement suggestions to this dissertation.

This work has been supported in significant part by the EC Seventh Framework Program FP7 / IST-216224. I would like to express my gratitude to the members of the MNEMEE project. In particular, I am indebted to Stylianos Mamagkakis and Arindam Malik who coordinated this project and finally agreed on using the MACCv2 framework in this project, to Sander Stuijk for always supporting my work within the project and finally, to all the other participants who have lead the project to success and in this way made it a success story for MACCv2 as well.

Finally, many thanks goes to the students who I have been able to work with. I appreciate a lot all their cooperation and contribution to this work. In particular, thanks goes to Christoph Faßbach for his contribution of an exemplary optimization technique and to Selma Jabour and Frank Benneker for working on the Eclipse-IDE integration.

I owe my family my gratitude because they always supported and believed in me. I do so in particular to my parents, Barbara and Herbert. They have always been there for me. Above all, I would like to express my deepest thanks to my wife, Patricia, who gave me all her patience and comprehension for such a long time since the beginning of this adventure.

Düsseldorf, March 2017

# Contents

| 1        | $\mathbf{Intr}$ | oduction                               | 1  |

|----------|-----------------|----------------------------------------|----|

|          | 1.1             | Context                                | 1  |

|          | 1.2             | Contribution to Research Community     | 6  |

|          | 1.3             | Author's Contribution                  | 8  |

|          | 1.4             | Structure Overview                     | 8  |

| <b>2</b> | Rela            | ated Work and Design Context           | 13 |

|          | 2.1             | Introduction                           | 13 |

|          | 2.2             | System Modeling                        | 13 |

|          | 2.3             | Frameworks                             |    |

|          | 2.4             | Targeted Optimization Techniques       | 19 |

|          | 2.5             | Common-Object-Class Services           | 21 |

|          | 2.6             | ICD-C Framework                        | 22 |

|          | 2.7             | MNEMEE Project                         | 26 |

|          |                 | 2.7.1 Project Overview                 |    |

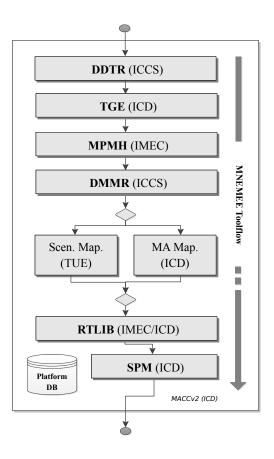

|          |                 | 2.7.2 Toolflow Structure               | 27 |

|          |                 | 2.7.3 Project Outcome                  | 29 |

| 3        | Des             | ign Specification                      | 33 |

|          | 3.1             | Introduction                           | 33 |

|          | 3.2             | Motivation                             |    |

|          | 3.3             | System Description                     |    |

|          |                 | 3.3.1 System-Model Structure           |    |

|          |                 | 3.3.2 Address Spaces                   |    |

|          |                 | 3.3.3 Access Model                     |    |

|          |                 | 3.3.4 Access Routing and Mapping       |    |

|          | 3.4             | Aspect Modeling                        |    |

|          |                 | 3.4.1 Aspect Definition                |    |

|          |                 | 3.4.2 Value Composition                |    |

|          | 3.5             | Framework                              |    |

|          |                 | 3.5.1 Processing-Step Integration      |    |

|          |                 | 3.5.2 Supplementary Framework Services |    |

|          | 3.6             | Conclusion                             |    |

| 4        | Imr             | lementation                            | 75 |

|          | 4.1             | Introduction                           |    |

|          | 4.2             | Framework Services                     |    |

|          |                 | 4.2.1 Common Base Class                |    |

|          |                 | 4 2 2 Code Representation              |    |

# Contents

|               |       | 4.2.3   | Runtime Environment                                   |     |  |

|---------------|-------|---------|-------------------------------------------------------|-----|--|

|               |       | 4.2.4   | User-Interface Abstraction                            | 93  |  |

|               |       | 4.2.5   | Practical User-Interface Implementations              | 98  |  |

|               | 4.3   | System  | Modeling                                              | 105 |  |

|               |       | 4.3.1   | Practical Component and Channel Models                | 106 |  |

|               |       | 4.3.2   | Common Aspect-Handler Examples                        | 118 |  |

|               | 4.4   | Process | sing Step Integration                                 | 121 |  |

|               |       | 4.4.1   | Tool Implementation                                   | 121 |  |

|               |       | 4.4.2   | Tool Specialization and Abstract Tools                | 123 |  |

|               |       | 4.4.3   | Processing-Step Interaction and Configuration Options | 124 |  |

|               |       | 4.4.4   | Toolflow Construction                                 | 126 |  |

|               | 4.5   | Conclu  | sion                                                  | 129 |  |

| 5             | Eval  | luation | Results                                               | 131 |  |

|               | 5.1   | Motiva  | tion                                                  | 131 |  |

|               | 5.2   | System  | n Design Effort                                       | 132 |  |

|               | 5.3   | Abstra  | ction-Level Considerations                            | 136 |  |

|               | 5.4   | Target  | -Platform Representation Precision                    | 137 |  |

|               | 5.5   | •       |                                                       |     |  |

|               |       | 5.5.1   | Application in MNEMEE Project                         | 144 |  |

|               |       | 5.5.2   | Application in Teaching                               |     |  |

|               |       | 5.5.3   | Application for Present Techniques                    |     |  |

|               | 5.6   | Conclu  | sion                                                  |     |  |

| 6             | Con   | clusion | 1                                                     | 161 |  |

|               | 6.1   | Summa   | ary                                                   | 161 |  |

|               | 6.2   | Future  | Work                                                  | 162 |  |

| $\mathbf{Bi}$ | bliog | raphy   |                                                       | 165 |  |

| Li            | st of | Figure  | es ·                                                  | 171 |  |

## 1 Introduction

### 1.1 Context

Software development is a challenging task. Implementing algorithms is similar to the way humans communicate to each other, there is a myriad of ways to pass-on given abstract information. Assuming a given language, the knowledge of expected audience enables a more concise representation by reducing the amount of context information or using particular commonly known phrases. Choosing a particular way to express some information is typically guided by a set of limiting factors. Most likely, the primary factor is the time frame available for a given speech or the number of pages available in a publication. Finding the most informative representation within the given set of limitations is clearly a challenging Optimization Problem. Coming back to the software development process, straightforward relations to the natural language formulation exist. The target platform can be denoted as the audience. Detailed knowledge of the target-platform properties enables an implementation which reduces code overhead and utilizes all available hardware components. The motivation for implementing an algorithm in a particular way is analogous. The implemented task needs to be performed within a given time limit or a given energy budget. Finding sufficiently fast or energy saving implementation is again an optimization task. In contrast to natural languages, for computer programming languages, automated transformation and optimization approaches exist, which can be used to achieve a more appropriate representation while preserving the semantic notion. The work presented in this thesis provides the implementation foundation for a set of such optimization techniques which benefit especially from detailed target-platform knowledge.

Target platforms which closely interact with the surrounding environment often expose tight limiting factors. Primarily, manufacturing costs, reliability requirements and size and/or weight limits translate immediately into limited memory size, low computational power or a tight energy budget. Nevertheless, these *Embedded Systems* are becoming omnipresent and are required to perform increasingly complex tasks. These tasks vary across application domains. The automotive and avionic domains expose tasks in the area of engine control, position estimation, mitigation of injuries or human interaction devices. Typically, this domain exposes high reliability requirements in a harsh environment and especially in the automotive area also exposes high demand for cost efficient solutions. Besides the automotive domain, industrial applications are driven by embedded systems as well. This includes small-sized actuator and motor control at various power levels as well as large-scale distributed production process control networks. Finally, an interesting domain is the still emerging domain of mobile communication devices and corresponding networks. Especially hand-held devices expose all

kinds of limiting factors like weight, size, battery capacity, while requiring vast computational power enabling these devices to provide an appealing user experience and high data throughput. Common to all these applications is the focus directed towards the actual task to be performed, less towards the presence of a processor-based computer which is executing software. Actually, in many cases, a typical user will not be aware of using a computer. Nevertheless, a software-based approach helps to provide a flexible and eventually an in-field modifiable implementation. Knowledge of both the target application (which most likely will not change throughout the embedded system's life time) and the obscured computational part allow for choosing a well-tailored hardware platform. Especially, adding dedicated hardware blocks (i.e. communication processors, graphic processing units, etc.) and finding a reasonable trade-off between total system cost, necessary computational power and memory size are the knobs to be adjusted for a particular target application. Even though this non-exhaustive enumeration already spans a multidimensional design space, recent embedded systems designs add another dimension: The number of processing units. Many applications can be divided into concurrent subtasks. In terms of energy consumption it is advantageous to distribute these tasks to multiple, but slower, processing units, instead of executing them sequentially at high speed on a single CPU. As described by Rabaey et al. [1], this is primarily due to the power dissipation dependency on switching frequency and supply voltage in CMOS circuits. Due to the size limitations and interconnection performance requirements, multiprocessor embedded systems are implemented as Multi Processor Systems on a Chip (MPSoCs).

With respect to the initial example, in case of embedded software development, the challenge of implementing a particular application is comparable to having to give a talk on the same or similar topic to a variety of audience. On the positive side, for each particular talk, the audience is well-known. The straightforward approach would imply preparing the talk for each audience from scratch. Obviously, this is the least efficient approach. Nevertheless, initially in the case of embedded software development similar approaches were used. In those days, devices were programmed in assembler language. This allows for highly efficient implementations, but on the down side, the tractable complexity is limited. Furthermore, regarding current days' time-to-market requirements, prohibitively long development times would occur and the resulting software would still tend to be error-prone. In contrast to assembler languages where the main focus is directed towards the capabilities of the target processor, high-level programming languages provide an architecture-independent set of control-flow statements, a uniform way to express arithmetic and logic computations, a type-safe data storage management and typically a set of language-domain-specific features (i.e. message passing primitives in case of distributed systems programming languages). Using high-level programming languages moves developers' focus away from the actual target-platform peculiarities towards to the algorithm to be implemented.

The C programming language [2] has evolved to be the preferred language over recent years for embedded system software development. Primarily, the combination of aforementioned high-level language features, a small runtime-environment footprint and

the possibility to express efficient access to hardware components has rendered this language a good choice for embedded software development. The wide popularity of this language spurred development of corresponding compilation techniques. The C programming language is based on a sequentially imperative programing model. This model is well-suitable for single core architectures. Nevertheless, current embedded systems evolve towards multicore systems where concurrent execution of multiple processing threads is possible. Since there is no native representation within the C language which would allow implementing concurrently executing threads, typical approaches are based on function calls which encapsulate thread invocation, synchronization and data transfer.

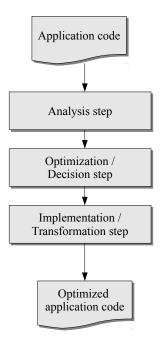

Translation of C programs into assembler language representation and finally into an executable binary is typically performed via a tree pattern matching approach. Prior to this step, various Source-Code Transformations are going to be performed. In general, source-code transformations replace a sequence of statements or expressions with another one, which is semantically equivalent, but can be later translated into a more efficient binary representation in terms of runtime or energy consumption. The challenging task in supporting development of such source-code transformations is related to finding a solution for following requirements:

- Provide a precise application-code representation which fully covers all C language features: Especially for source-level transformations, the application-code representation must not perform any automated code simplification. All language patterns have to be preserved in the internal representation.

- Provide a conversion path back to plain textual source-code representation: Typically, source-level optimizations rely on a present compiler infrastructure. Once all optimizing transformations have been performed, the resulting source code has to be reconstructed to be fed into the compilation toolchain.

- Provide an interface which allows for easy modification but ensures correct application-code syntax: Performing syntactically-correct code modifications is non-trivial. The application-code representation has to provide an API which maps the code structure onto an object graph, where transformations of this graph relate to source-code transformations. This way application of only syntactically valid transformations can be ensured.

- Provide support for data-flow and control-flow analysis: Besides code transformations, optimization techniques need to analyze the code structure and corresponding data-flow paths in advance of taking optimization decisions. A graph-oriented representation is also beneficial for this task.

- Provide tight integration with the system model: Typically, optimization techniques relate application-code fragments and variations of those to particular system-model item. A uniform representation among both domains simplifies this task.

The work presented in this thesis relies on a well-suited source-code representation. Fortunately, the ICD-C [3] compiler framework could be used for this purpose. It offers an object-oriented interface to the application-code representation, conversion paths between plain-text and internal representation and several analysis and standard optimization steps. The challenging task in context of this thesis was related to the integration of the system model and the application-code representation into a uniform optimization technique foundation.

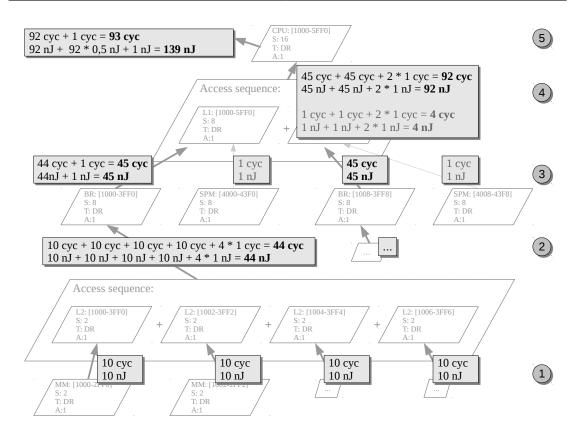

The actual benefit of such source-code transformations is dependent on the target-platform properties and the compiler used to generate the binary code representation. In straightforward approaches some trivial assumptions are made (i.e. less source code will result in a smaller binary code footprint, which in turn likely results in faster execution). Obviously, these assumptions do not always hold. Therefore, optimization techniques, which take target-platform properties into account, can achieve much better results. Superior to iterative approaches, where several transformations are evaluated on the target platform, and the one being most efficient is chosen, are optimization techniques which use model-based target-platform descriptions. These optimization techniques can immediately take the most suitable optimization decisions for a given platform. In particular, performing optimizations which take memory-subsystem properties into account can result in significant gains. Each instruction fetch and each data movement involves some memory accesses. Directing frequent accesses to fast or energy-efficient memories shows immediate benefits.

Among all the system-modeling languages developed in recent years, some incorporate a memory model. In almost all cases, they target generation of simulators, transformation to hardware description languages or code generator generation. Actually, none of them fits very well the needs of source-level optimizations. The first class of languages implements a behavioral model, which can be transformed into executable code on the host platform and thus supports simulation. Transformations to HDLs require primarily structural information. A fixed set of properties per component is required to interpret the description and translate it to lower-level HDL. Furthermore, a high level of detailed information is required right from the beginning of system specification, since generation of a complete and synthesizable hardware description is at focus. In contrast to this, for memory-aware optimizations, a quite abstract system model is usually sufficient. Finally, models for code generator generators focus on the internal structure and instruction set of processing units. In contrast to the application-code representation, the lack of a suitable system-model description led to the proposal of a novel approach which primarily targets source-level optimizations.

The major challenge in provision of a target-platform model suitable for source-level optimizations is related to finding a balanced representation, which provides sufficient information, while being as abstract as possible, to achieve low construction effort. In addition, in most cases more than one optimization technique is applied to a given source code. Ideally, each of them uses the same target-platform model to reduce the risk of contradicting optimization decisions. Basically, such an system-modeling approach has to fulfill following requirements:

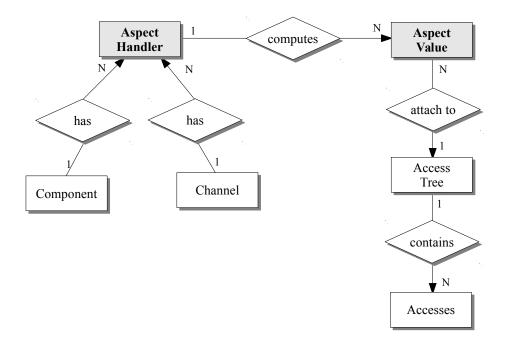

- Provide a combined locally scoped structural model with the typically required component-centric full-system property perspective: There are in general two contradicting requirements: The system-model designer prefers a self-contained view of each system-model component, while the optimization technique developer prefers system-global property values which take all the particularities of a system into account. Especially by the means of proposed aspect handlers, the system-modeling approach provides a satisfactory solution for both requirements.

- Provide a system-modeling approach feasible for modeling of a wide range of target-platform types: Covering a wide range of target platforms implies either a vast set of predefined properties and system components, or a fully open set of properties. In the first case, significant implementation effort would be required, while still retaining the drawbacks of a closed system model. In the second case, optimization techniques need additional, often implicit, knowledge about the item names, and structural properties of the system description to be able to retrieve particular system property values. The approach proposed in this thesis uses component inheritance and the aforementioned aspect handlers to overcome these drawbacks.

- Provide precise system property access at optimization technique runtime: Typical full-system-simulation-based system property evaluation exposes a prohibitively prolonged response time. This renders optimization techniques which rely on such data infeasible for being applicable in compilers runs occurring in typical application development processes. The system-modeling approach proposed in this thesis provides a balanced implementation which is capable of provision of system property values at a precision level comparable to full-system-simulation-based approaches, while offering a fast, application-structure-independent and query-based interface. This allows for implementing optimization techniques being applicable in typical compiler runs.

The system-modeling approach proposed in this thesis fulfills aforementioned requirements and therefore solves the challenging task of provision of a versatile, precise and runtime-applicable system description.

Finally, supporting source-level optimization technique development is also related to provision of an implementation framework. The most challenging task in this domain is related to finding the right set of features being beneficial for development of source-level optimizations. Typical infrastructural properties of several optimization technique approaches in the domain of memory-aware source-level optimizations have been analyzed. This results in the following set of typical requirements related to the optimization technique framework:

• Provide self-contained optimization technique representation: A modular, self-contained optimization technique highly increases chances for successful reuse

in further optimization flows. The challenging task here is related to finding simple, uniform but sufficiently flexible interface definition.

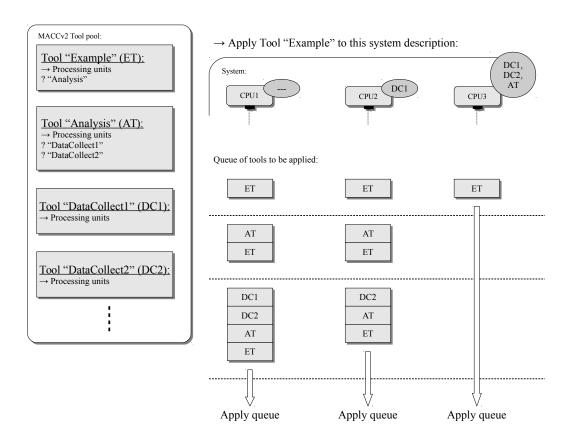

- Provide support for application in hierarchical optimization flows: Optimization techniques are typically subdivided into fine-grained steps. These steps tend to consist at least of further analysis or transformation sub-steps. The framework proposed in this thesis provides a processing-step interface, which can be used uniformly across all hierarchy levels, while being able to keep track of tool dependencies across these levels.

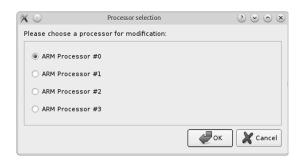

- Provide user-interaction facilities: Optimization techniques may require user interaction while being applied to particular application code. Especially, in the case of current research work, where new ideas are evaluated, user interaction is beneficial. Within this framework a highly abstracted user-interface model has been developed, which allows for interactive optimization technique implementations which are independent of the current execution environment.

- Provide data exchange and storage support: Besides the actual application-code representation, multi-step optimization techniques need to pass additional meta-data between correlated processing steps. The challenging task in this context is related to provide an easily accessible, preferably native-language-based, method for data retention and data communication. The framework proposed in this thesis offers a sophisticated object model, which provides uniform and serializable data representation across the system-model description, the application-code representation and supplementary optimization technique data.

In general the framework solves the challenging task of bringing support and facilities for research-grade optimization technique development, while keeping focus on applicability of these techniques in production-grade compilation environments.

Concluding the introductory context overview, the work proposed in this thesis targets the domain of memory and target-platform-aware source-level optimization techniques. A well-balanced approach of application-code representation, target-platform model and supplementary services framework is proposed. This combination of these building blocks has shown its real-life applicability in the MNEMEE project.

### 1.2 Contribution to Research Community

Developing source-level optimization techniques for embedded MPSoC platforms is a challenging endeavor. The work presented in this thesis provides an infrastructure which facilitates this task.

There are two major areas of contribution. The first deals with platform representations. Applying optimizing code transformations typically requires knowledge of target-platform properties while taking optimization decisions, in particular since such optimizations are expected to improve performance either in terms of runtime or energy

consumption on a given target system. There are numerous ways to provide this information. Starting from implicit assumptions in the optimization technique implementation, over some lookup-table-based approaches, up to more generic optimization-techniquespecific system descriptions. Even those system descriptions are limited to suit best one particular optimization technique implementation. The contribution in this area is provision of a uniform system-modeling approach which fits well the requirements of a wide range of memory-aware optimization techniques for embedded MPSoC platforms. The system model is located at a quite abstract system-modeling level, the processor-memoryswitch level. This abstraction level fits well requirements of memory-aware optimizations which typically need to acquire a system overview first (i.e. type and count of memories) and later on need detailed memory-component-related information (i.e. per-access energy consumption). This system-modeling approach features a unique method to calculate on-the-fly system-wide properties based on local definitions within components and interconnections. This allows for a very modular approach, while still providing precise system-level properties to optimization techniques. A growing set of components and channels, which can be easily combined and adjusted, enables low effort modeling of various system-model descriptions. The object-oriented system-modeling approach allows for well-structured component and channel property representation. Especially, inheritance relations are a valuable way of finding a particular class of system-model components or acquire class-specific details. The system-modeling approach presented here has found community acceptance at the LCTES'10 conference. Refer to Pyka et al. [4].

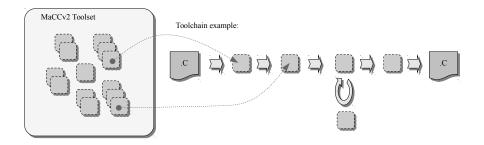

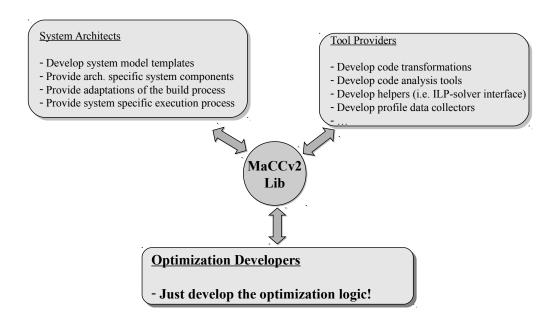

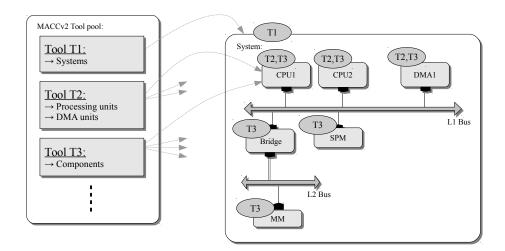

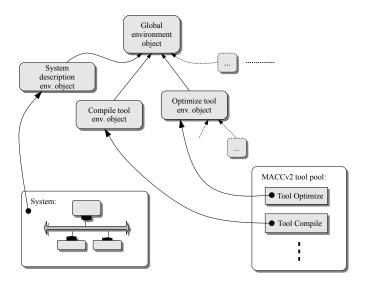

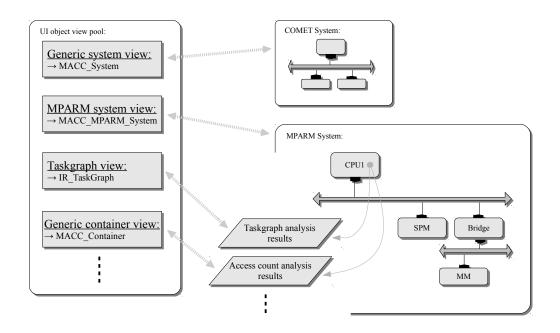

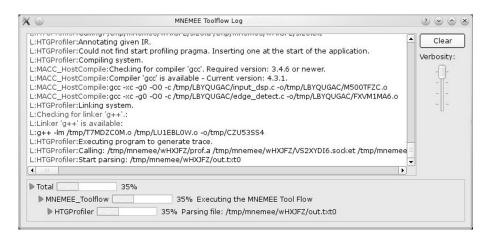

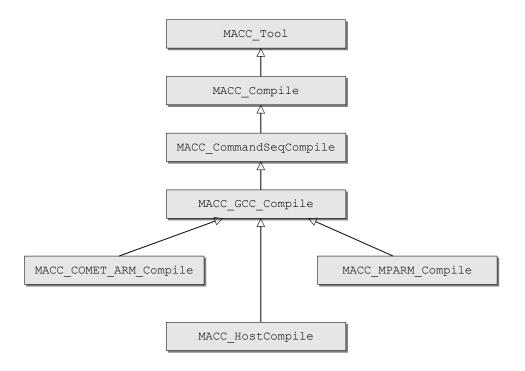

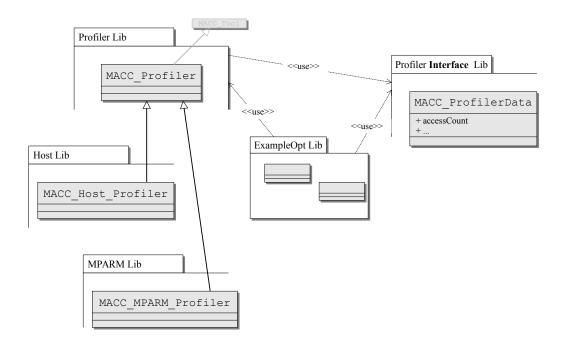

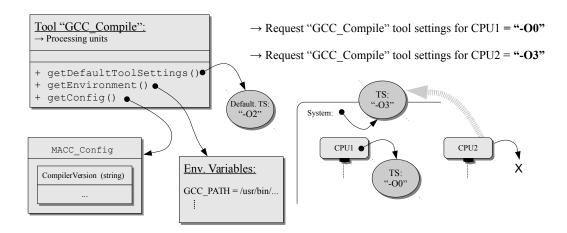

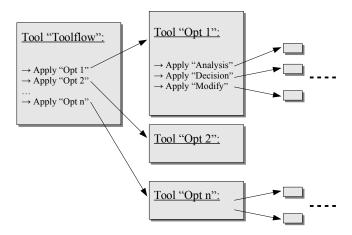

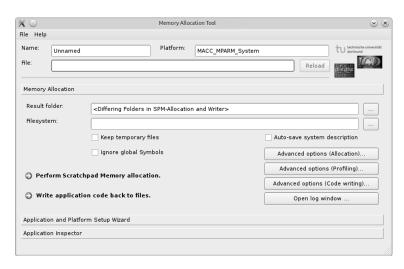

In the second area of contribution an optimization technique framework is presented. Proposing a theoretical system-modeling approach in isolation would be of limited benefit once an actual optimization technique has to be implemented. Therefore, the systemmodeling approach presented in this thesis has been embedded into an optimization technique framework. The unique combination of an infrastructure which supports optimization technique cooperation and data exchange, accompanied by the aforementioned system-modeling approach and a detailed application-code representation provides a solid foundation for rapid optimization technique development. Encapsulating optimization, analysis and code transformation techniques into so-called tools which expose uniform invocation interfaces is one of the key properties of this framework. This simplifies invocation of a variety of commonly occurring tasks. As can be observed later on for the MNEMEE toolflow in Section 5.5.1.3, especially construction of toolflows of such self-contained building blocks becomes available at significantly reduced effort. Furthermore, the framework provides commonly-used services to optimization techniques. This includes data retention, source-code and system-model annotation techniques, a common-object-class model and corresponding reflection methods and a user-interface abstraction layer.

The proposed MACCv2 framework, including the system-modeling approach, has been successfully used as the core integration service in the MNEMEE project. The project's resulting optimization toolflow translates an initially sequential application code into a parallel representation. The primary goal targets a more energy-efficient utilization of

available processing resources and related memories. Furthermore, the MACCv2 framework has been used in teaching activities at ALaRI [5]. The object placement computed in the scratchpad-memory optimization could be interactively presented to students in hands-on sessions. The approach supports effortless tweaking of target-platform properties (i.e. memory sizes or energy-model values) and observing the resulting optimization decisions.

Concluding the contribution, the approaches presented in this thesis have been able to show their added value in a real-life project, teaching, related PhD theses and subsequent research work.

#### 1.3 Author's Contribution

Summarizing author's contribution to the work presented in this thesis two areas of contribution are considered separately. Regarding conceptual work, models and approaches Table 1.1 shows an enumeration of author's contribution to particular topics of this thesis. Except for the source-code representation, the author is the only contributor.

Table 1.2 shows an overview of author's contribution to the implementation topics relevant in this thesis. Here, full contribution has been limited to the core MACCv2 framework components, while contribution to remaining implementation topics, which have been primarily performed in the context of MNEMEE project, has been limited to provision of implementation support and starting point templates.

#### 1.4 Structure Overview

This thesis is structured into six chapters. Following this introductory chapter, references to related work and design context are given next.

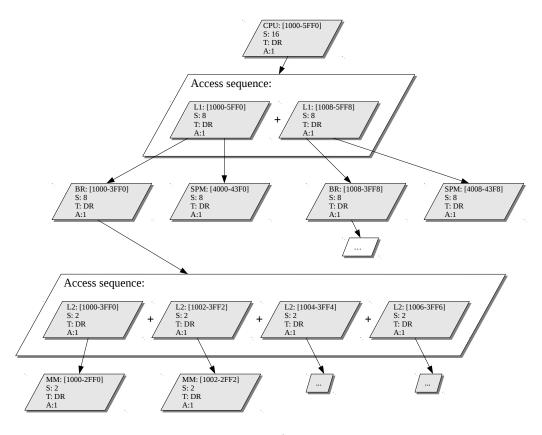

Chapter 3 presents models and design specifications regarding the major contributions of this thesis. Preceded by an introduction and motivation, the proposed system-modeling approach is presented first. Key properties are enumerated and a structural overview is presented to the reader. The next section presents the aspect-modeling approach. Aspects in terms of this thesis are arbitrary values which will be computed on-the-fly according to the system-model structure, while still being accessible in a database-like style. The last section focuses on the framework. A structural overview is presented, followed by a description of major framework services. In particular these are:

- Interfaces to the system-model representation.

- Target-platform property computation.

- Processing-step representation.

- A set of supplementary runtime services.

A final conclusion summarizes the proposed design specification.

| Topic                                       | Aprox. contrib. % | Remarks                                                                             |

|---------------------------------------------|-------------------|-------------------------------------------------------------------------------------|

| System description                          | 100%              |                                                                                     |

| Access enumeration                          | 100%              |                                                                                     |

| Aspect handlers                             | 100%              |                                                                                     |

| Framework basic services                    | 100%              |                                                                                     |

| Framework tool model                        | 100%              |                                                                                     |

| Framework user interface abstraction        | 100%              |                                                                                     |

| Framework runtime env. and library handling | 100%              |                                                                                     |

| Exemplary opt. technique in Section 5.5.3   | 10%               | Developed in context of diploma thesis advised by author.                           |

| ICD-C code representation                   | 5%                | Product of ICD e.V. The author added common object class and serialization support. |

Table 1.1: Author's contribution to concepts and models.

Chapter 4 takes a close look at the actual implementation and corresponding examples. The set of general framework services around a common-object-class model is presented first. In particular these are:

- Base-class services.

- Code representation.

- Runtime environment.

- User interfaces.

Based on this foundation, implementation details of the system-modeling approach and processing-step representation are described. As appropriate, sections are accompanied by practical example of presented items. A final conclusion summarizes the proposed implementation.

Within Chapter 5, the system-modeling approach and framework evaluation results are presented. Evaluation has been performed according to a set of goals initially motivated: First, the effort required to provide a system model is discussed. Especially, the possibility to control the effort by choosing the appropriate level of detail is a valuable property of this approach. Next, a subsection focuses on the abstraction level chosen

for this system-modeling approach. Here again, a trade-off between level of detail and accessibility exists. The processor-memory-switch level has been identified as the most appropriate abstraction level for the needs of memory-aware optimization techniques. Finally, the precision of this approach is discussed. Since the access method significantly differs from known methods (i.e. simulation-based approaches) a comparison is performed, showing this approach as being capable of providing similarly precise values in a fraction of time compared to state-of-the-art methods. Hereafter, the applicability of this approach to real-life problems is evaluated. There, the benefits for the MNEMEE project are presented, applicability in courses has been shown, and finally the effort and benefits of porting an already existing optimization technique to this framework is discussed.

This thesis is concluded in Chapter 6. The proposed system-modeling approach and framework qualifies as a viable way for rapid development of memory-aware source-level optimization techniques. Towards the end of this chapter, limitations and possible future extensions are discussed.

| Topic                                | Aprox. contrib. % | Remarks                                                                                           |

|--------------------------------------|-------------------|---------------------------------------------------------------------------------------------------|

| MACCv2 core library                  | 100%              |                                                                                                   |

| Basic source-code optimizations tool | 100%              |                                                                                                   |

| Compiler/build tools library         | 30%               | Developed by other MNEMEE participants. The author provided templates and implementation support. |

| Run/profiling tools library          | 20%               | Developed by other MNEMEE participants. The author provided templates and implementation support. |

| Generic command-line executables     | 100%              |                                                                                                   |

| Host platform template               | 100%              |                                                                                                   |

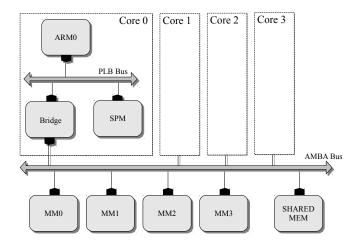

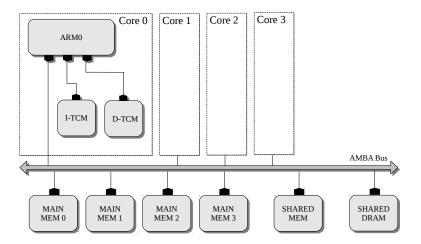

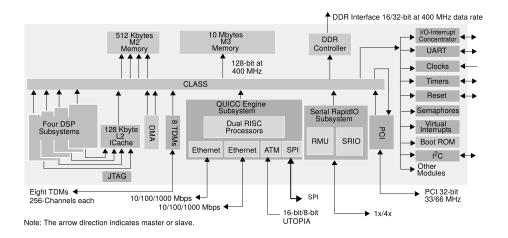

| MPARM platform template              | 40%               | Structural model provided by the author. Energy and latency handlers provided by Klein [4].       |

| COMET platform template              | 10%               | Developed in the context of the MNEMEE project.                                                   |

| MSC8144 platform template            | 10%               | Developed in the context of the MNEMEE project.                                                   |

| UI texmode                           | 100%              |                                                                                                   |

| UI graphical (Qt)                    | 100%              |                                                                                                   |

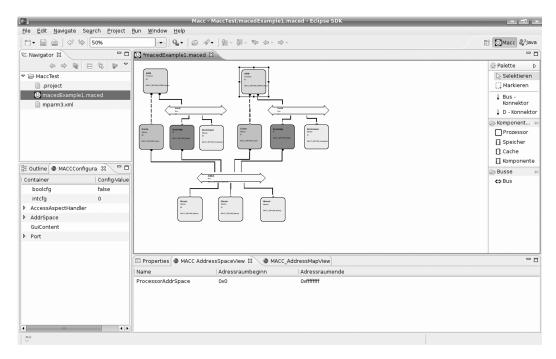

| UI for Eclipse-IDE                   | 10%               | Developed in the context of a diploma thesis advised by author.                                   |

| MNEMEE toolflow integration          | 60%               | The author provided a top-level tool and templates for tool interfaces classes.                   |

| MNEMEE optimization steps            | 5%                | Developed by other MNEMEE participants. The author provided implementation support.               |

| MNEMEE toolflow frontend UI          | 100%              |                                                                                                   |

| Application in teaching              | 5%                | The author provided contributions to the graphical user interface.                                |

Table 1.2: Author's implementation-related contribution.

# 2 Related Work and Design Context

### 2.1 Introduction

The work presented in this thesis incorporates several disjoint aspects which have relations to previously performed work in the research community. First of all, the proposed system-modeling approach is put into relation to previous research. In particular, the general classification according to the abstraction level is of prominent importance. Since besides the system-modeling approach a fullfledged framework supporting development of memory-aware optimization techniques is proposed, corresponding related work is analyzed next.

Next, an overview of possible application domains for this framework and systemmodeling approach is given. This is done by providing a concise enumeration of targeted optimization techniques for which this framework is expected to be beneficial.

Later on, implementation techniques used in this framework are referenced and shortly introduced. In particular, these are the various common-base-class services and the application-code representation ICD-C.

Finally, the MNEMEE project is presented in the last section of this chapter. The work presented in this thesis has been primarily carried out in the context of this project. The contribution presented in this thesis has been used as the integrating foundation in MNEMEE.

## 2.2 System Modeling

This thesis proposes a framework for fast and effort-efficient development of memory-aware optimization techniques. One of the highlighted features of this framework is the target-system description. Using a common system description across various optimization techniques, integrated by the means of this framework, allows for well-coordinated

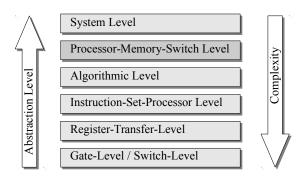

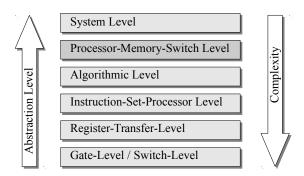

Figure 2.1: System-modeling levels

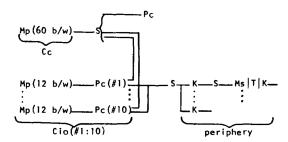

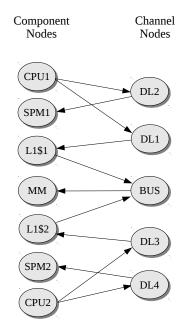

Figure 2.2: Exemplary Bell/Newell PMS representation of a CDC 6600 system. [7]

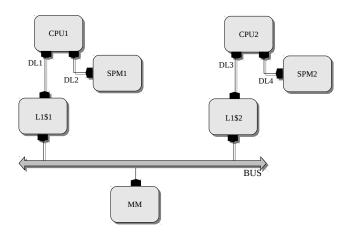

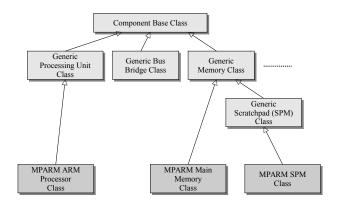

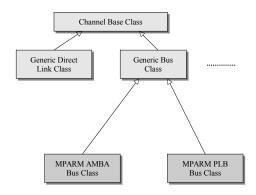

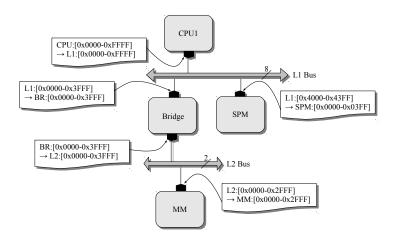

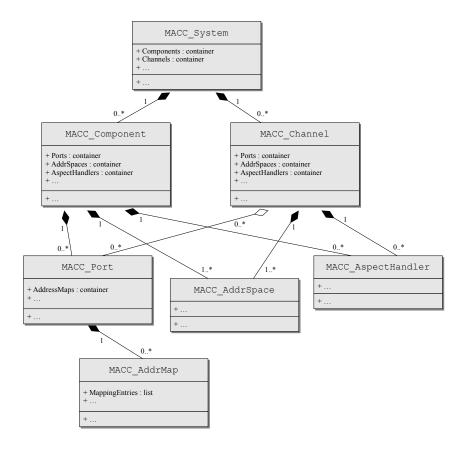

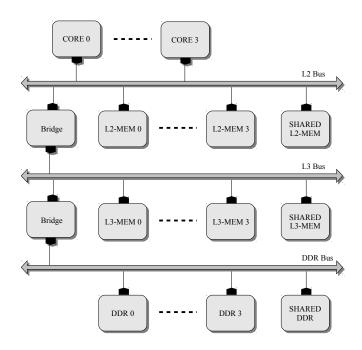

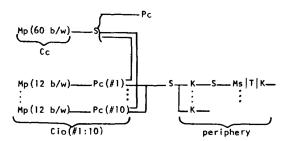

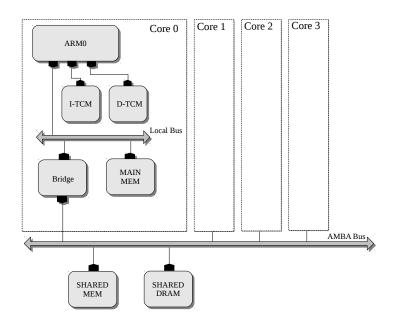

processing and higher optimization gains. Furthermore, for reasonably fast executing optimization techniques, target-platform properties need to be accessible instantaneously without prolonged full-system simulation. Such a target-system description requires a definition using a suitable system-modeling language. According to the classification of system-modeling languages along the abstraction level as shown in Figure 2.1, the description language presented in this thesis can be assigned to the PMS level. Processor-Memory-Switch models were introduced by Bell and Newell [6]. They describe the system at an abstract level where the main building blocks are the system components (i.e. processors and memories) and the interconnection between them. The primary application for PMS models was provision of a description of structural properties of computer systems and the interconnections between them. Originally, PMS models define seven item types:

- Processors

- Memories

- Switches

- Links

- Data operation

- Transducers

- Controllers

In a graphical representation, instances of these items were connected via lines to each other to represent a relation between them. Annotations to these items provide further classification and higher level of detail, if required. These optional annotations allow for subsequent refinement of system models. Figure 2.2 presented by Bell and Newell depicts such an exemplary structure.

Nowadays, improvements in chip manufacturing enable much higher integration, resulting in on-chip structures which resemble full computer networks at the time of introduction of PMS models. Refer to Jantsch and Tenhunen [8] for a description of further

properties of such Networks-on-Chip (NoCs). Nevertheless, the need for a representation of such systems still persists. Therefore, the corresponding PMS abstraction level has preserved its value. The system-modeling approach presented in this thesis takes advantage of the PMS abstraction level. Especially, for the domain of memory-aware optimization techniques a balanced system description is required. It is expected to expose sufficient target-platform properties, without being difficult to handle, due to excessive level of detail. Please refer to Section 3.2 for a more in-depth motivation.

Subsequently, various architecture description languages (ADLs) have been developed in recent years. One comprehensive approach to classify them is by the main application target. A first application target is the automatic transformation into a hardware description language. This helps in automating hardware development as well as in shortening the development cycle, where precise simulators can be derived in advance from a HDL representation. A second main application target is the automatic generation of development tools like compilers, assemblers and linkers. Both application targets impose almost disjoint requirements on the ADL. On the one hand, hardware description requires precise structural information, on the other hand, automatic tool generation requires a behavioral and semantic description of the system. In the domain of memory-aware optimization techniques, focus has been put on the actual optimization technique. In most cases an ad-hoc approach has been used which provides the required parameters in an optimization-technique-specific way. Therefore, this thesis proposes a new systematic approach in the domain of memory-aware optimization techniques, which is based on a common target-platform model. Since memory optimizations typically require abstract structural properties enriched by individual semantic information, several ADLs used in the domain of HDL construction and development tools generation are relevant to this thesis. Even though they provide a valuable foundation, none of them offers the appropriate scope to be directly usable within the MACCv2 framework.

LISA [9] is an ADL which targets primarily automatic generation of application-specific hardware and corresponding simulators and low-level tools. Primary architectural targets are signal processing and generic irregular single processor architectures. The language has been extended later towards automatic compiler generation. To accomplish this task, an additional semantic instruction set model has been added by Ceng et al. [10]. Since the main target of LISA is the cycle-true description of a digital signal processor, neither a sophisticated system model nor detailed memory model exists. The timing model integrated into LISA focuses on the specification of the pipeline behavior. No energy model is incorporated into LISA. Muhammed et al. [11] describe a subsequent extension to LISA, which provides a resource model. Still, this resource model is quite processor-centric and targets a simple enumeration of memories and their sizes and few other resource types.

ArchC [12] is another currently available ADL. ArchC was designed to support processor architecture description. While the language has evolved, also the possibility to design memory hierarchies has been added. Similar to LISA, ArchC covers the structural and behavioral view of a system model. Since ArchC is based on the SystemC language, which provides extensions to C++ for description of timing and concurrency, ArchC

models are described in C++ code as well. On the positive side, this allows for the description of a large variety of different systems, on the negative side, once it comes to other tasks than simulator generation, it is really hard to extract any semantic meaning from such a model. The SystemC language offers all the expression possibilities of the C++ language. This is perfect for simulation, since this allows for efficient implementation of compiled-simulation simulators, which is the fastest simulation method available. Recent work by Schürmans et al. [13] shows even the applicability of SystemC models for power estimation in full-system simulation. But even the task of statically extracting timing information out of such a model without imposing any restrictions to the modeling style is an almost intractable problem. Closely related to ArchC is PDesigner [14]. Basically, it is a graphical editor which can be used for an intuitive, component-based development of ArchC system models.

Specialized system descriptions targeting mapping of applications on MPSoCs are another group of system-modeling languages. In this context, references to the SpecC language developed by Gajski et al. [15], the ADL used in DAEDALUS [16] or the hardware platform description in the CIC-based (common-intermediate-code-based) retargetable parallel programming framework for MPSoC by Kwon et al. [17] are provided. Finally, the Distributed Operation Layer (DOL), as presented by Thiele et al. [18], can be considered to be within this group as well. In general, these system descriptions are from the structural point of view similar to the one presented in this thesis. Especially, SpecC exposes a similar channel- and component-based structure. The major difference to the work presented in this thesis is the application centric platform view of these modeling languages. On the one hand, platform specifications as occurring in DOL focus on the communication structures important to the target application. In the first place, such a model is not going to resemble the actual physical target-platform structure, but will contain abstract channels which represent end-to-end links between processing units. On the other hand, approaches like SpecC focus on target-platform hardware structure adaptation for a particular application. Trying to use these modeling languages in the reverse scenario for application-code modification on a fixed platform would require various optimization-technique-specific annotations to the system model. These approaches would suffer from the fact that changes to the properties of one component need to be annotated in several places of the system description. The energy consumption of a memory component would be an example for such an annotation. In contrast to this approach, a change of such a value would also affect the per-access energy values annotated to processing elements. In general, this will require user interaction and in-depth system knowledge to precompute these values.

EXPRESSION [19] was developed in the late 90's. It aims primarily at automatic generation of software development tools. The motivation for this language was faster design space exploration (DSE) on a single processor of the SoC. To accomplish this task, EXPRESSION describes the system in a structural and behavioral way. In contrast to previous languages, EXPRESSION offers an explicit memory model. There is only a fixed set of parameters which can be used to describe properties of memories available

to the processor. On the downside of this ADL, there is no method to convert the description into a HDL for automatic generation of processor hardware.

Regarding design space exploration, an interesting approach is presented by Diewald et al. [20]. The proposed Exploration Meta-Model (EMM) focuses on coordination of design space explorations in the context of Model-Driven Development (MDD). Since the MACCv2 system description can be used for fast exploration of target-platform variations, but models for guiding these variations are out of the scope of the MACCv2 framework, both approaches perform complementary roles. Therefore, DSE-related optimization techniques are expected to benefit from a combined application of both approaches.

A slightly different application scenario is specified for the TDL [21] language. The primary goal of this language is to support development of retargetable post-pass optimizations at assembly level. This is what comes closest to the approach proposed in this thesis. TDL includes a structural description of resources present in the system. This includes memories and corresponding cache hierarchies. Furthermore, a behavioral description of the instruction set is the second key part of the TDL language. Nevertheless, there are significant differences to the proposed ADL. The semantical information in the resources section does not allow for modeling structural dependencies between memories. Furthermore, only single processor-based memory hierarchies can be described.

A related approach for platform description is presented by Kessler et al. [22]. Their XPDL language targets a similar application scenario as the one presented in this thesis. In general, system-level target-platform properties can be retrieved via a C++-based API. These properties are stored precomputed within the XML system description. If some properties are missing, a microbenchmarking-based profiling step is triggered to estimate these values. In contrast to the approach presented in this thesis, which calculates these values on-the-fly solely from locally scoped properties attached to each component, the XPDL approach operates similar to typical table-lookup approaches. Frequent platform modifications require time-consuming reprofiling of these values.

Finally, a vast variety of other ADLs exists. As examples, references to hardware-related ADLs like IP-XACT [23], nML [24], ISDL [25] and MIMOLA [26] are given. All of them do not focus on development of memory-hierarchy-aware source-code transformations. The common goals are simulation, HDL extraction or compiler generation. None of them satisfies all the requirements imposed once source-level optimizations for multicore platforms are targeted. In a broader scope, the set of software-related ADLs also has to be taken into account. Examples in this class of ADLs are Wright [27] or Darwin [28]. In contrast to this approach, these ADLs concentrate on description of the application architecture instead of the platform the application is being executed on.

Concluding the overview of system-modeling-related work, several system-modeling approaches have been identified. In general they can be classified into two groups. The first one, which focuses on behavioral models, targets construction of full-system simulators. The second one, which focuses primarily on structural properties of processing units targets compiler and design tool development automation. Actually, none of them takes

requirements of memory-aware source-to-source transformations into account. Furthermore, the preferable abstraction level, and therefore the level of detail, highly depends on intended application scenario. The PMS abstraction level offers the best suitable balance between modeling complexity and level of detail.

## 2.3 Frameworks

The system-modeling language presented in this thesis is embedded into a framework which provides a foundation for the development of various optimization techniques. Several of previously-referred system-description languages have a similar relation to a framework in their specific domain. Most noticeable are LISA [9], DEADALUS [16] or MIMOLA [26]. The MACCv2 framework proposed in this thesis focuses on source-code transformations which strive to achieve an optimized representation of a target application in terms of energy consumption or runtime. A relative in this domain is the LLVM-framework [29]. LLVM provides an infrastructure targeting compiler implementation for various programming languages. Typically, several subprojects concentrate on parsing of source code (i.e. Clang, Dragonegg), debugging (LLDB), providing a set of core libraries which implement transformation, optimization and lowering steps which translate the source-code representation into an assembler-like intermediate representation. This low-level representation can be later on translated into target-platform executables regardless of the programming language used up-front. To some extent both frameworks, LLVM and MACCv2, perform the same task, namely, performing code transformations. Nevertheless, major differences exist: LLVM focuses on code compilation, and provides corresponding optimization techniques, while MACCv2 focuses on source-to-source transformations which target efficiency improvement in terms of energy consumption or runtime via optimized memory-access patterns. In contrast to this framework, where a fullfledged model of the target-platform memory subsystem exists, the LLVM framework offers a set of target-platform properties, which are relevant for code generation and therefore are focused towards processor unit description. An example in this area is the work presented by Grech et al. [30]. They propose a processor centric application-code energy-consumption estimation. The estimation is based on a per-instruction energy-consumption model which does not model any further platform properties. In general, LLVM can be considered to have the same scope as the ICD-C compiler framework being a component integrated into the work presented here.

A framework which also targets memory-aware compilation has been presented by Verma et al. [31]. It consists of compilation and simulation parts which operate on a common energy data base. Both parts are focused towards an ARM7 architecture. A self-implemented compiler and corresponding analysis steps allow for implementation of dedicated and deeply integrated optimization techniques. Nevertheless, this approach comes to its limit, once retargetability becomes frequent and more important. The implementation effort for setting up the specific compiler and simulator infrastructure for each new target platform is prohibitively high. This has been the initial motivation for provision of a framework which is also capable of exploiting memory hierarchy properties

in optimization techniques, but does not have such a static structure and utilizes existing tools and compilers to achieve a similar compilation and evaluation loop.

A similar approach of combining a fixed set of tools for MPSoC-related software optimization is provided by Iosifidis et al. [32]. The framework, called MPMH, consists of three dedicated transformation steps targeting distinct aspects of application-code optimization. First, the application code is transformed into a parallel representation according to some annotations passed along the actual application code. The second step takes care of appropriate static data allocation and finally the last one does dynamic data structure transformations. A simple, list-based, platform description provides the enumeration of target-platform properties guiding these transformation steps. In contrast to the work presented in this thesis, MPMH framework does not focus on providing a foundation for development of memory-aware optimizations. Therefore, even though the targeted application scenario is the same, the scope is completely different. In a comparison, MPMH framework would rather relate to a particular instance of combined optimization techniques implemented using the MACCv2 framework. This relation can be observed in the evaluation section, where the application of MACCv2 framework as foundation for the MNEMEE toolflow [33] is presented. In particular, the MNEMEE toolflow incorporates wrappers for MPMH optimization steps. Hence these steps have been used as individual processing step within this optimization flow.

Concluding the framework-oriented related work, efficient implementations of memory-aware optimization techniques are best founded on a common framework. Well-known frameworks focus either on hardware extraction or compilation. Especially, the last type of frameworks contributes a variety of source-code transformations. Nevertheless, they do not take memory-subsystem properties into account. The work presented in this thesis, provides a unique combination of an abstract system model and a corresponding framework which targets the domain of memory-aware source-level optimizations on embedded multicore systems.

### 2.4 Targeted Optimization Techniques

Designing embedded systems always has the abstract goal of finding the most efficient implementation. Unfortunately, there are contradicting limitations like cost, size and timing constraints which reduce this goal to finding some balanced implementation among these constraints. Initially, both hardware and software were freely adopted to the target scenario, which results in high development effort. Once chip manufacturing costs hit millions of dollar per mask and short time-to-market times were demanded, platform-based design became the predominant design approach. Sangiovanni-Vincentelli and Martin [34] provide an overview of platform-based design aspects. Along the transition towards platform-based design, source-level code optimizations become more and more relevant. In particular, platform definitions are accompanied by a mature compilation toolset. Often the rapid time-to-market inhibits development of platform instance optimized compilers. Therefore, target-platform-aware source-to-source optimization are the

preferred method to achieve an efficient mapping of application code onto a particular target-platform instance.

Performing source-level optimizations has a long history. In the late 70s, Loveman [35] proposed various loop transformation methods targeting high-level programming languages. In this work it has already been recognized that applying source transformations leads to a target-platform-dependent benefit. Loop transformations have been important optimization methods for years. Sophisticated approaches which utilize polyhedral modeling have been presented by Falk and Marwedel [36]. Especially, benefits of high-level representations and source-to-source transformations have been analyzed and promoted in their work.

Regarded at a broader scope, loop optimizations can be considered as a subset of optimization approaches which gain their benefits due to reorganized memory-access sequences. Even though typically not at the same optimization point, both runtime reduction or energy-consumption reduction can nevertheless be achieved this way. Especially, energy-consumption reduction under the constraint of keeping runtime within required bounds is a prevalent topic in embedded system design and particularly in embedded software development. There are numerous aspects to be considered which could, depending on target-architecture properties, lead to desired energy-consumption reduction. On the one side, there are optimizations, like the aforementioned loop optimizations, which lead to energy savings due to reduced memory-access counts, either due to reduced code size, reduced data accesses counts or beneficial cache access sequences. On the other side, optimized placement of a particular code or data item has also a significant effect on energy consumption and runtime. Typically, embedded systems expose complex memory hierarchies with several memories differing in size, access latency, energy consumption or accessibility. More details on fundamental computer architecture properties are provided by Hennessy and Patterson [37] and a view more focused toward embedded systems is given by Marwedel [38].

Finding an efficient and feasible placement of application code and data has been a challenging task for years and still engages the research community. Panda et al. [39] provide a survey on a broad set of optimization techniques, while Wolf and Kandemir [40] present a more software-focused view on possible approaches. For practical examples references to the work done by Lai et al. [41] in the data-flow-oriented application domain, as well as to the work done by Wehmeyer and Marwedel [42] in the control-flow-oriented application domain are given. In the last one in particular, a closer look at the energy-consumption aspects of various memory types is taken and beneficial optimizations for these types are suggested.

Improvements in integrated circuit manufacturing technology allow for development of complex systems on a chip. These systems typically expose multiple processing units as well as several on-chip memories. These components are connected via multiple hierarchy levels of buses or even more complex interconnection channels. These complex Multiprocessor Systems on a Chip (MPSoCs) still need efficient mapping of target applications on a particular platform instance. Single core techniques including data placement and loop transformations can be adapted to multicore platforms. Verma and Marwedel [43]

show particular approaches in this area. Even though presence of multiple cores already adds further complexity to the memory-access optimization step, automated distribution of application code to these processing units adds an additional optimization dimension to the application-code mapping problem. Complexity grows by the variation in types of processing units included in a system. Homogeneous platforms have all processing units of the same type, followed by platforms where two types of processing units are included, both expose the same ABI but their internal structure implies operation at different speed and differing energy-consumption level. Kumar et al. [44] provided some considerations on these so-called big.LITTLE architectures. Continuing mapping problem complexity considerations along processing-unit variation, mapping of applications on systems having each processing of different type, can be considered the most generic, but also most complex approach to accomplish such mapping task. Techniques which perform application-code distribution across multiple processing units have been proposed by Cordes et al. [45] and later on accompanied by techniques presented by Jovanovic et al. [46], which actually map such distributed application code on particular processing units including consideration of efficient memory-hierarchy utilization.

Concluding this fraction of approaches targeting optimization of embedded systems software, there are a few recurring prerequisites needed for successful performing of such optimizing code transformations:

- A notion of target-platform structure and available component and interconnection properties.

- An optimization-decision guiding set of performance values. These may be execution times, energy-consumption hints, etc.

- An easy to modify, precise and usable for plain source-code reconstruction application-code representation.

The work proposed in this thesis aims at the provision of a common foundation for optimization techniques in the area described in this section. Therefore, among others, concluded optimization technique prerequisites have been addressed and corresponding models and implementations are provided. In fact, previously referred approaches by Jovanovic et al. [46] and by Cordes et al. [47], including the corresponding PhD theses [48], [49] benefit from this work. They use the MACCv2 framework and corresponding system models as a foundation for their optimization and transformation technique implementations.

# 2.5 Common-Object-Class Services

The framework services and approaches have been implemented in the C++ programming language [50]. The C++ language is commonly used in the area of memory-aware optimization techniques. This is often due to the availability of required libraries and tools (few examples are: lp\_solve API library [51], LLVM pass implementation interface [52] or the ICD-C framework [3]). Further, nowadays the decision to implement an

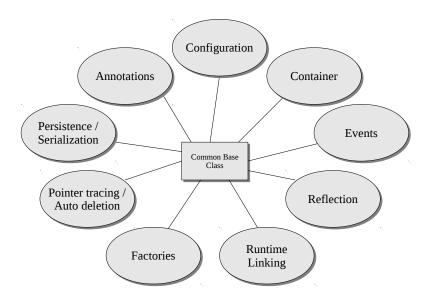

upcoming optimization technique in C++ is historically motivated, since previous work has been implemented this way, such an implementation promises the least effort and a fast result. Therefore, this observation has been the natural motivation to contribute this work as a C++-based framework. Even though C++ is an expressive and powerful language, especially once it comes to support runtime linking and modularity it gets to its limits. In the case the application image is constructed of independent libraries of code at runtime, the code needs to become self-aware. In particular, it needs to have a notion of class names and their relations, have an insight into the class structure at runtime and provide some means of building object graphs of at compile-time-unknown object-classes. In the same context persistent data retention is based on the same object structure. These object structures need to be capable of being persistently stored and restored in some later runtime context. These requirements have been recognized to exist in the context of memory-aware optimization technique development as well. Therefore, the MACCv2 framework presented in this thesis has been designed to implement a set of services which provide reflection, common-object-class representation, object factories and serialization. Initially, a broad scoped presentation of design patterns targeting these aspects was given by Gamma et al. [53]. Especially, there are numerous approaches for object serialization. Maeda [54] gives an overview of these approaches. Besides C++, other languages have native support for common object model and corresponding serialization support. The most prominent is Java [55].

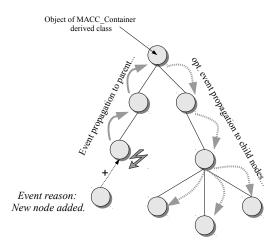

Modularity and runtime linking has another challenging point. Since the complete application context is not known a priori, typically the scope of an implementation is at best limited to library boundaries. Interaction between objects of different libraries needs dedicated support. Basically, there are two aspects to consider. First, objects typically hold references to other objects. Since the referencing set of objects is not known, some reference counting and pointer tracing is needed to ensure a consistent data structure state. Henney [56] provides a survey on approaches found in this area. The second aspect targets object notification. Since object state changes are of interest to other objects, some notification mechanism is needed. Gamma et al. [53] introduced the Observer design pattern, where current days programming languages like Java provide corresponding implementations [57].

### 2.6 ICD-C Framework

The MACCv2 framework presented in this thesis focuses on the provision of a foundation for the development of source-level optimization techniques for MPSoCs. Since a typical application scenario of MPSoC devices targets embedded applications, a typical application code to be optimized is implemented in the C programming language. Therefore, addressing this scenario requires an application-code representation for the C programming language. The most straightforward application-code representation operates on the plain textual representation. Although this is the most universal way to represent code, it offers least syntactic details. Also, performing changes is equivalent to editing the text, which happens without any syntactical correctness guarantees.

Therefore, except for some very basic cases, where text-based source-code modifications could be assumed to be the preferred way, any reasonable optimization or transformation technique needs an intermediate representation (IR) to perform the code modifications in a well-defined, and syntactically-correct way. Performing source-level code transformation via an intermediate representation requires translation of such a textual representation into the IR and, once all optimizations and transformations have been performed, back to a textual representation. To achieve these translations, source-level intermediate representations typically parse the textual representation and try to construct out of this token stream an abstract syntax tree according to expected programming language. Since performing sophisticated source-level optimizations is still an emerging technique, typical application scenarios for abstract-syntax-tree-based (AST-based) code representations target compiler development. There, the reverse step, reconstruction of a textual representation out of an AST, is not required. Therefore, most intermediate representations focus only on a semantically correct representation, but allow or even perform intentionally, simplifications, which prevent reconstruction of the original application code.

The ICD-C [3] intermediate representation used in MACCv2 framework has been designed for both application scenarios: compiler development as well as source-level optimizations. Therefore, it supports such reconstruction of source code out of its intermediate representation. Since the precise application-code representation has been at focus, the complete set of ANSI-C language constructs is covered by this intermediate representation. Some additional features (i.e. some GCC extensions or source-comment representation) are also provided, allowing application even for a specialized domain of code (i.e. automotive code). Besides the intermediate representation several standard and architecture-independent analysis, optimization and transformation techniques are provided within ICD-C.

In the context of this framework, the previously available ICD-C intermediate representation has been slightly extended. Basically, the major goal was to make ICD-C benefit from the advantages of a common-object-class model. Therefore, the ICD-C intermediate representation has been modified to fit the approach presented in Section 4.2.1. Due to this integration, a common foundation exists across the system-modeling implementation, the application-code representation and the processing-step integration approach provided within this framework. Such a cross domain foundation is a subtle, but very beneficial property of MACCv2 framework. Expression of optimization-technique-dependent cross-object relations and annotations is possible with only minimal effort for the optimization technique developer.

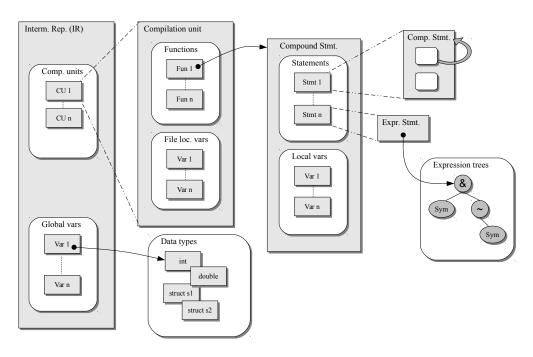

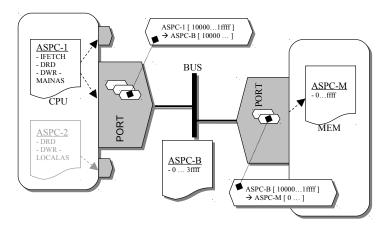

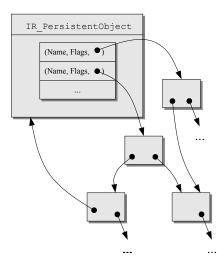

A closer look at the properties of ICD-C application-code representation shows an overall structure as depicted in Figure 2.3. At top level the representation is enclosed by a single object which describes a self-contained IR. Each intermediate representation consists of a set of compilation units and a set of global application symbols (i.e. global variables). A compilation unit basically relates to a single source-code file including all header files. At the next level the structure follows the grammatical structure of the C programming language. Therefore, compilation units consist of function definitions and

Figure 2.3: ICD-C IR structure overview.

file-scoped symbol declarations. Function definitions are basically structured in hierarchical statement lists. All language-relevant statement types are provided. The typical nested hierarchical code structure is represented via compound statements, which themselves contain a statement list. Other types represent loops, conditions or expressions, including the most commonly appearing assignment expressions. Especially, the expression statements are interesting in this structural overview because they provide a link to the expression representation. Expressions are represented as a tree. Except for the representation of symbols or constant values, each expression consists of one or more sub expressions. According to the evaluation order, such expression elements form expression trees.

Besides the abstract syntax tree, also semantical information is provided within this application-code representation. First of all, data type representation is provided for each symbol and each expression. Herein, relations like type modifications, storage class assignments and, if applicable, complex data type membership relations are expressed. Further semantical information is deduced from on-the-fly analyses. This includes among others, function-wide data-flow analysis and control-flow analysis. Based on this intermediate representation a set of sophisticated analyses is provided. This includes loop bound analysis or an alias analysis. For further details on the properties of the ICD-C code representation, please refer to [3].

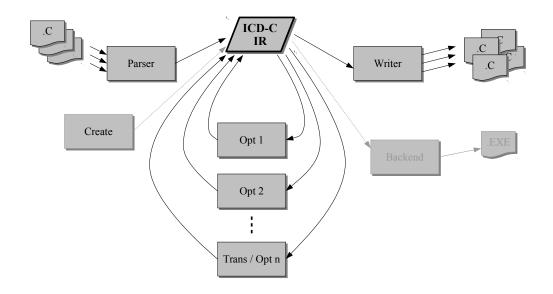

Figure 2.4: ICD-C workflow.

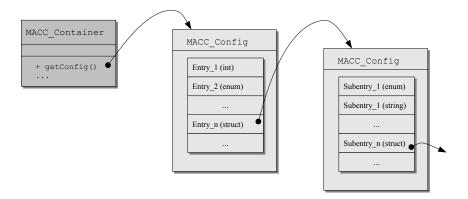

Figure 2.4 shows commonly-occurring ICD-C workflow scenarios. A typical method to construct ICD-C intermediate representations is to parse a textual C program representation. A corresponding parser is provided within ICD-C. Besides the parsing-based method, fully API-driven construction of intermediate representations is supported. Basically, the same API, as used for modifications of an IR, can be used to construct such an intermediate representation from scratch.

The intermediate representation itself and surrounding services are implemented in the C++ language. Therefore, the IR and corresponding API are exposed to the user in an object-oriented manner. Consequently, modifications performed on the application code via ICD-C are performed as modifications on the IR object graph or as modifications to properties of particular objects in this graph. Typical modifications are replacements of expressions or statements. Also more complex transformations such as inlining or exlining of code fragments can be performed in a semantically correct way with limited effort.

Once the application code has been modified accordingly, the optimization technique may decide to write-out the intermediate representation as a plain-text C program. ICD-C provides all the necessary methods to dump each compilation unit into a text file which can be accepted as C program input by a subsequent optimization or compilation step. If applying multiple optimization steps in the context of this framework, such a conversion between textual representation and the intermediate representation can be avoided on intermediate steps. Since the ICD-C framework is based on the common-object model of MACCv2, the serialization and persistent data retention methods can be applied to store and later reconstruct a snapshot of an IR. The advantage of this data retention method is the seamless retention of all analysis and optimization-related annotations.