# DESIGN OF FAULT-TOLERANT VIRTUAL EXECUTION ENVIRONMENTS FOR CYBER-PHYSICAL SYSTEMS

# Dissertation

zur Erlangung des Grades eines

# DOKTORS DER INGENIEURWISSENSCHAFTEN

der Technischen Universität Dortmund an der Fakultät für Informatik

von

BOGUSŁAW JABŁKOWSKI

Dortmund 2019

Ort: TU Dortmund

Fakultät: Informatik

Tag der mündlichen Prüfung: 23.07.2019

Dekan: Prof. Dr.-Ing. Gernot A. Fink

Gutachter: Prof. Dr.-Ing. Olaf Spinczyk

Prof. Dr. Peter Marwedel

The last decade revealed the vast economical and societal potential of Cyber-Physical Systems (CPS) which integrate computation with physical processes. In order to better exploit this potential, designers of CPS are trying to take advantage of novel technological opportunities provided by the unprecedented efficiency of today's hardware. There are, however, considerable challenges to this endeavor.

First, there is a strong trend towards softwarization. Functions that were originally implemented in hardware are now being increasingly realized in software. This fact, together with the ever growing functionality of modern CPS, translates to unrestrained code generation which, in turn, directly influences their safety and security. Second, the spreading adaptation of multi-core and manycore architectures, due to their considerable increase in computation power, additionally generates issues related to timing properties, resource partitioning, task mapping and scalability.

In order to overcome these challenges, this thesis investigates the idea of adopting virtualization technology to the domain of CPS. Several research questions originate from this idea and the following work aims at answering those questions. It addresses both technological and methodological issues. With respect to the technological aspects, it investigates problems and proposes solutions related to timing properties of a virtualized execution platform as well as the thereon based high availability technique. Regarding the methodological aspects, it discusses models and methods for the planing of safe and efficient virtualized CPS compute and control clusters, proposes architectures for the development and verification of virtualized CPS applications as well as for the testing of non-functional characteristics of the underlying software and hardware infrastructure. Further, through a set of experiments, this thesis thoroughly evaluates the proposed solutions.

Finally, based upon the provided results and some new considerations regarding the requirements of future CPS applications, it gives an outlook towards a generic virtualized execution platform architecture for emerging CPS.

The ideas and findings presented in this dissertation have partly been published in the following peer-reviewed journals and proceedings of international conferences and workshops. The list is sorted in chronological ascending order:

- B. Jablkowski, M. Mueller, and O. Spinczyk. High availability in cyber-physical systems by self-determined virtual machine replication. In Proceedings of the 13th IEEE International Symposium on Industrial Embedded Systems (SIES 2018), June 2018. [62]

- B. Jablkowski et al. vGridLab a testbed for virtualized smart grids. Journal of Computer Science - Research and Development, Aug. 2017. Extended abstract. [65]

- 3. B. Jablkowski, U. T. Gabor, and O. Spinczyk. Evolutionary planning of virtualized cyber-physical compute and control clusters. Journal of Systems Architecture, Feb. 2017. [63]

- 4. B. Jablkowski and O. Spinczyk. CPS-Remus: Eine Hochverfügbarkeitslösung für virtualisierte cyber-physische Anwendungen. In W. A. Halang and O. Spinczyk, editors, Tagungsband zum Thema Betriebssysteme und Echtzeit (Echtzeit 2015). Springer, Nov. 2015. [68]

- 5. B. Jablkowski and O. Spinczyk. CPS-Xen: A virtual execution environment for cyber-physical applications. In 28th International Conference on Architecture of Computing Systems (ARCS '15), pages 108–119, Porto, Portugal, Mar. 2015. Springer. [69]

- A. Kubis, L. Robitzky, M. Küch, S.-C. Müller, B. Jablkowski, H. Georg, N. Dorsch, S. Krey, C. Langesberg, D. Surmann, D. Mayorga, C. Rehtanz, U. Häger, O. Spinczyk, C. Wietfeld, C. Weihs, U. Ligges, J. Myrzik, and J. Götze. Validation of ICT-based protection and control applications in electric power systems. In PowerTech Conference (POWERTECH), Eindhoven, Netherlands, June 2015. IEEE Press. [75]

- 7. N. Dorsch, B. Jablkowski, H. Georg, O. Spinczyk, and C. Wietfeld. Analysis of communication networks for smart substations using a virtualized execution platform. In Proceedings of the International Conference on Communications (ICC '14). IEEE Press, 2014. [37]

- 8. B. Jablkowski, M. Küch, O. Spinczyk, and C. Rehtanz. A hardware-in-the-loop co-simulation architecture for power system applications in virtual execution environments. In Proceedings of the Workshop on Modeling and Simulation of Cyber-Physical Energy Systems (MSCPES 2014), pages 1–6. IEEE Press, 2014. [64]

- 9. B. Jablkowski and O. Spinczyk. Continuous performance analysis of fault-tolerant virtual machines. In Proceedings of the 1st GI Workshop on Software-Based Methods for Robust Embedded Systems (SOBRES '12), Lecture Notes in Informatics, pages 494–505. German Society of Informatics, Sept. 2012. [67]

First and foremost I want to thank my advisor Prof. Dr.-Ing. Olaf Spinczyk, who provided me with the opportunity to start working

in research and continuously supported me with advice and funding along the path leading to this thesis. I would also like to thank Prof. Dr. Peter Marwedel for his engagement and time to review this work.

Further, I would like to thank for the help and advise of all those, who I meet and had the pleasure to collaborate with over the years while working as a researcher. This includes people I collaborated with in the context of the DFG research group 1511, among them Nils Dorsch, Andreas Kubis, Markus Küch and Sven-Christian Müller as well as colleagues from my department: Hendrik Borghorst, Christoph Borchert, Daniel Friesel, Ulrich Gabor, Claudia Graute, Andreas Grosche, Alexander Lochmann, Matthias Meier, Michael Müller, Horst Schirmeier and Jochen Streicher

I would like to express special thanks to Markus Buschhoff – with whom I shared the office since the first day at work – and Alexander Munteanu for their support, the countless discussions and their continuous willingness to help.

Last but not least, I wish to thank my family. My parents, who for my entire live provided me with the freedom and support to pursue my interests, my wife, who assisted and supported me along the way as well as my little son, from whose very fact of existence I draw joy and motivation.

# CONTENTS

| 1 | INT | RODUCTION 1                                         |   |

|---|-----|-----------------------------------------------------|---|

|   | 1.1 | Motivation 3                                        |   |

|   |     | 1.1.1 Can It Work? 4                                |   |

|   | 1.2 | Research Questions 6                                |   |

|   | 1.3 | Scientific Contributions 7                          |   |

|   | 1.4 | Contributions Obtained in Cooperation 8             |   |

|   | 1.5 | Thesis Structure 9                                  |   |

| 2 | BAC | KGROUND 11                                          |   |

|   | 2.1 | Virtualization Technology 11                        |   |

|   |     | 2.1.1 A Brief Historical Overview 11                |   |

|   |     | 2.1.2 What Is Virtualization Technology? 12         |   |

|   |     | 2.1.3 Types of Execution Environments 13            |   |

|   |     | 2.1.4 Platform Virtualization 15                    |   |

|   |     | 2.1.5 The Xen-Hypervisor 17                         |   |

|   |     | 2.1.6 Unikernels 22                                 |   |

|   | 2.2 | System Performance Analysis 23                      |   |

|   |     | 2.2.1 Categories of System Performance Analysis 24  |   |

| 3 | VIR | TUALIZED CPS-ARCHITECTURE 27                        |   |

|   | 3.1 | Cyber-physical Energy Systems 27                    |   |

|   | 3.2 | Sources of Indeterminism 29                         |   |

|   | 3.3 | CPS-Xen for Real Time 32                            |   |

|   | 00  | 3.3.1 Real-Time Scheduling in Xen and CPS-Xen 32    |   |

|   |     | 3.3.2 Architecture of CPS-Xen 35                    |   |

|   |     | 3.3.3 Evaluation 39                                 |   |

|   |     | 3.3.4 CPS-Xen and RT-Xen on Embedded Hardware 48    | 8 |

|   | 3.4 | CPS-Remus for Efficient High Availability 50        |   |

|   |     | 3.4.1 High Availability - State of the Art 51       |   |

|   |     | 3.4.2 High Availability Assumptions 54              |   |

|   |     | 3.4.3 Self-determined Replication 56                |   |

|   |     | 3.4.4 Evaluation 59                                 |   |

|   |     | 3.4.5 Real-world Applicability and Service Recovery |   |

|   |     | Latencies 66                                        |   |

|   | 3.5 | Chapter Summary 68                                  |   |

| 4 | PLA | NNING VIRTUALIZED CPS 71                            |   |

|   | 4.1 | Challenges 71                                       |   |

|   | 4.2 | Concept 73                                          |   |

|   | 4.3 | Methodology, Architecture, Models and Techniques 74 |   |

|   |     | 4.3.1 Architecture and Scheduling Model 75          |   |

|   |     | 4.3.2 CPS-Model 76                                  |   |

|   |     | 4.3.3 The Evolutionary Algorithm 78                 |   |

|   |     | 4.3.4 Performance Analysis 80                       |   |

|   |     | 4.3.5 Integer Linear Programming 81                 |   |

|                    | 4.4     | Analy    | zing Virtualized CPS 82                         |

|--------------------|---------|----------|-------------------------------------------------|

|                    |         | 4.4.1    | Scenario Generation 82                          |

|                    |         | 4.4.2    |                                                 |

|                    |         | 4.4.3    | Experiments 84                                  |

|                    |         | 4.4.4    | Time and Scalability 86                         |

|                    |         |          | Convergence 86                                  |

|                    |         | 4.4.6    | Ping-Pong Effect 87                             |

|                    |         | 4.4.7    | Online or Offline Placement 87                  |

|                    | 4.5     | Praction | cal Issues 88                                   |

|                    | 4.6     | Chapt    | er Summary 91                                   |

| 5                  | TES     | TING O   | F VIRTUALIZED CPS 93                            |

|                    | 5.1     | Hardy    | vare-in-the-Loop Co-Simulation Architecture 93  |

|                    |         |          | IEEE1516 HLA Standard 95                        |

|                    |         |          | The HiL co-Simulation Architecture 96           |

|                    |         |          | HiL-Interface 97                                |

|                    |         |          | Proof of Concept 98                             |

|                    |         | 5.1.5    | Simulation Process and Results 99               |

|                    |         | _        | Discussion 101                                  |

|                    | 5.2     | vGrid1   | Lab – a testbed for virtualized Smart Grids 101 |

|                    | 5.3     | Chapt    | er Summary 104                                  |

| 6                  | DISC    | CUSSIO   | N AND OUTLOOK 105                               |

|                    | 6.1     | Safety   | Certification 105                               |

|                    | 6.2     | Gener    | ic Architecture for Emerging CPS 106            |

|                    |         | 6.2.1    | Requirements of Future CPS 107                  |

|                    |         | 6.2.2    | Generic Architecture 109                        |

| 7                  | SUM     | IMARY    | AND CONCLUSION 111                              |

|                    | 7.1     | Contri   | butions 111                                     |

|                    | 7.2     | Final l  | Remarks 113                                     |

| Α                  | APP     | ENDIX    | NUMERICAL EVALUATION RESULTS. 115               |

|                    |         |          |                                                 |

| Lis                | st of l | Figures  | 117                                             |

|                    |         | C        | ·                                               |

| List of Tables 119 |         |          |                                                 |

|                    |         |          | •                                               |

|                    |         |          |                                                 |

BIBLIOGRAPHY 121

### **ACRONYMS**

ABI Application Binary Interface

API Application Programming Interface

CPS Cyber-Physical Systems

CPES Cyber-Physical Energy Systems

CP40/CMS Control Program/Conversational Monitor Systems

CTSS Compatible Time-Sharing System

DM Deadline-Monotonic Scheduling Policy

DMA Direct Memory Accesses

EA Evolutionary Algorithms

ECU Electronic Control Units

ET Execution Time

FOM Federation Object Model

FP Fixed Priority Scheduling Policy

GOOSE Generic Object Oriented Substation Event

HA High Availability

HiL Hardware-in-the-Loop

HLA High Level Architecture

HVM Hardware Virtual Machine

ICT Information and Communication Technologies

IED Intelligent Electronic Devices

ILP Integer Linear Programming

IOMMU Input/Output Memory Management Unit

ISA Instruction Set Architecture

LibOS Library Operating Systems

MAST Modeling and Analysis Suit for Real-Time Applications

MMS Manufacturing Message Specification

MOP Multiobjective Optimization Problems

NAPI New API Packet Reception Mechanism

NSGA-II Non-Dominated Sorting Generic Algorithm II

OLTC On Load Tap Changer

OMT Object Model Template

OPC DA OLE for Process Control Data Access

OS Operating Systems

PMU phasor measurement unit

PV Paravirtualized

RM Rate-Monotonic Scheduling Policy

RTI Runtime Infrastructure

RTT Round-Trip Time

RTC Real-Time Calculus

RTDS Real-Time-Deferrable-Server

QDisc Queuing Discipline

QEMU Quick Emulator

SDN Software-defined networking

SEDF Simple Earliest Deadline First

SLAT Second Level Address Translation

SOME/IP Scalable service-Oriented MiddlewarE over IP

SR-IOV Single Root I/O Virtualization

SRT System Response Time

SV Sampled Values

UDP User Datagram Protocol

VIF virtual interfaces

VM Virtual Machine

VMM Virtual Machine Monitor

WCET Worst-Case Execution Times

INTRODUCTION

At the turn of the century, technological advances in computing and engineering initiated a new phase of the digital revolution. An ubiquitous and profound transition from analog to digital information storage, processing and communication took place. The shift affected all aspects of life as well as all branches of industry. In early 90's, high-end car models had on average less then ten *Electronic Control Units* (ECU) installed, while in 2005 cars from the same price category had about one hundred build-in ECUs [39]. In 1993 approximately only 3% of worlds technologically stored information was in digital format, in 2007 already more than 94% [53]. Mobile cellular subscriptions reached 0.61% of the worlds population in 1993, in 2010 they were amounted to 76.5% [100].

To a great extent, the technical foundation of this paradigm shift was formed by embedded systems, which can be defined as "information processing systems embedded into enclosing products" [95]. It was, however, not solely enabled by optimizing already known solutions. It was rather due to the fact that researchers and developers, driven by the novel technological opportunities, kept opening up new areas of application for embedded systems. As a consequence, the process of conjoining computation and communication with physical processes accelerated. By functionally interconnecting tasks, areas and domains that were previously operationally independent, embedded systems started to expand massively. Once functionally dedicated, single-purposed, closed, simple and manageable solutions now became multi-layered, eclectic, interconnected complex systems with a strong trend towards openness, evidently defying their original definition. As a consequence, established design and analysis approaches for embedded systems were rendered partially inadequate. A new abstraction was needed.

In order to better reflect the complex and heterogeneous character of the newly emerged systems, Helen Gill (National Science Foundation in the U.S.) introduced, in 2006, the term *Cyber-Physical Systems* (CPS) [77], a concept denoting the "integration of computation with physical processes". Of course recognizing this dependability at that time was not a new finding, at least not in the embedded system community. Yet, the incorporation of this view allowed, in contrast to classical embedded system design and analysis approaches, for the modeling and analysis techniques to concentrate less on the computational aspect and, instead, to focus on the interaction between the computational and physical worlds.

The intensification of research in this direction yielded numerous findings. Prominent book examples that summarizes many of these are: Marwedel [95], focusing on the fundamental bases of hardware and software models, Alur [2], describing formal methods for modeling and verification of CPS, and Lee [77], describing the realization of CPS by studying the interplay of the involved models (software, hardware, physical environment) and their temporal dynamics.

On the one hand, rising abstraction levels facilitates interdisciplinary design, analysis and verification of CPS. On the other hand, as fruitful and necessary the approach proves to be, it only solves a specific subset of problems. It is often not sufficient in respect of practical realization of CPS, as many of the problems and challenges – especially in the implementation and as a consequence also in the design of execution environments – are either not being addressed by such an approach or the problems are being hidden behind different abstraction layers. This is one of the reasons why CPS designers and engineers, despite using state-of-the-art modeling and implementation techniques, are still struggling with issues related to system complexity. In fact, the situation is becoming even more complicated as the complexity of CPS is increasing rapidly. In this regard, two factors can be differentiated: the software- and hardware-related sources of complexity.

Concerning the former, a strong trend can be observed of shifting from hardware-driven designs to software-driven designs. Functions that were originally implemented in hardware are increasingly being realized in software. Further, the technologically-driven growing functionality of modern CPS translates to unrestrained code generation. This process is being inevitably reflected in the exploding size of their software stacks. For example, contemporary premium-class automobiles contain about 100 million lines of software code.

Regarding the latter, they mainly stem from the spreading adaptation of multi-core and manycore architectures. These architectures offer a considerable increase in computation power, yet in turn they generate issues and challenges related to efficient parallelization, resource partitioning, task mapping, scalability or communication. The heterogeneous landscape of offered hardware products additionally intensifies the problem.

All of these aspects render modern CPS already today heavily complex as well as software-reliant systems and it is likely that the above described direction of CPS evolution will gather momentum. This will further increase the role of software in these systems and, as a consequence, the complexity of CPS. Getting an answer to the possibly hardest question that CPS developers face today will become even more complicated, namely: How to design and implement a safe and efficient system that fulfills all of the functional and non-functional requirements and – at the same time – remains manageable? The following dissertation aims at providing an answer to this question.

#### 1.1 MOTIVATION

The complexity of a system originates from it's functional and non-functional requirements. In the case of modern CPS, those are numerous and multifaceted. Depending on the application, the functional requirements range from simple sensor readings to complex algorithms conducting image analysis or solving optimization problems. In other words, the functional requirements of CPS cover a large spectrum of computation. Regarding the non-functional requirements, for many CPS, the most important one is meeting the timing-constraints from a given domain of application. Depending on the situation, failing at this task can result in a lower service quality or in a system failure with potential catastrophic outcome. However, there are also other non-functional requirements that CPS have to comply with. Among them are reliability, maintainability, availability, safety, security or efficiency [95]. The amount of constraints adds to the complexity of CPS.

Fortunately, the issue of complex software stacks, efficient utilization of manycore architectures as well as the optimization of multiple orthogonal requirements is not exclusive to the field of modern CPS. There exist other domains where researchers and developers are struggling with a wide range of similar challenges. A good example are large data centers, where comparable issues and challenges have been successfully tackled by the technique of virtualization – or more specific – by platform virtualization. The success of this approach is a consequence of the following features of this technology:

- It allows for the integration and consolidation of systems and system components on homogeneous and scalable hardware. This significantly reduces system complexity while increasing flexibility. Further, it allows for a considerably better resource utilization.

- Its excellent isolation properties provide a high degree of faultcontainment – both in time and space dimension. This significantly impedes the propagation of errors or unwanted withholding of crucial system resources. Additionally, this also makes it difficult for malware to compromise a system.

- It enables efficient high availability solutions which significantly improve dependability by allowing systems to survive hardware failures and guarantee service continuity.

- The techniques of *Virtual Machine* (VM) migration and live migration enable proactive maintenance and ease management. In addition, they facilitate efficient load balancing.

Finally, as a consequence of the above listened features, virtualization allows for a significant reduction of the procurement, operation and maintenance costs.

Considering the characteristics of modern CPS and their development trend, the above listed features of virtualization are of clear relevance for CPS, as they address many of the current and future challenges posed by these systems. In fact, the success stories from data centers and cloud environments have motivated a process of rethinking of the currently used system architectures. Due to the believe that virtualization technology has the potential to notably advance the automation process, many domains have started to explore the possibilities provided by this technology. This is especially true for the embedded system and CPS communities. Today, in the field of energy grids, logistic, automotive or avionic systems designers and engineers are struggling to develop novel, virtualization-based execution platforms. Unfortunately, the integration of CPS by means of virtualization is not a straightforward task as virtualization technology was initially not designed to cope with strict timing constraints. These, however, are omnipresent in CPS. Despite this fact, until recently, research has put the most emphasis on topics of fault-tolerance and hardware utilization. There is little literature on how to improve the real-time capabilities of this technology or how to model and integrate a CPS by means of virtualization. This is a relatively new and open research field.

### 1.1.1 Can It Work?

As discussed above, virtualization technology comes with many attractive benefits of which several are of high interest to the embedded and cyber-physical system communities. However, also reservations regarding the adoption of virtualization technology for embedded systems exist and have been expressed in literature. A prominent example is the article [51] by Gernot Heiser. The main points of criticism are that virtualization can not address the scheduling needs of embedded systems, as it is characterized by a hierarchical scheduling model which is, in fact, inherent to this technology, and that the virtual-machine model does not support an efficient way to share data between the components of a system. Finally, VMs are heavyweight and thus not suitable for embedded hardware and systems.

As far as the first objection is concerned, in Section 3.3.2.1, we describe how the concept of unikernels can help in overcoming the problem of hierarchical scheduling. Unikernels are lightweight enough to encapsulate individual threads into VMs and, as a consequence, allow for imposing global scheduling policies and facilitating timing analysis. Moreover, they also provide an answer to the reproach of resource inefficiency (see Section 2.1.6). In recent literature [93],

unikernels are shown to be as efficient as modern lightweight virtualization or container technologies, such as Docker [34] or LXC [84], yet without their substantial security issues. A trade-off between isolation (VMs) and efficiency (container) does not have to exist with unikernels. When optimally tailored, unikernels can have as small footprints as 480KB and run in as little as 3.6MB of RAM. Further, unikernels can be booted as fast as in a few milliseconds and thus comparable to process startup times – note that Docker containers need about 200ms.

Other techniques that can help to mitigate the discussed scheduling problem are partitioning approaches. For example, while using the Xen hypervisor [10], *cpupools* can be used for this purpose. This approach allows to partition the physical cores on a machine into different pools. Each of these pools can have a separate CPU scheduler, which can be set to meet different scheduling requirements. This is a flexible way to separate scheduling concerns, if needed, VMs can still be moved on-the-fly from pool to pool and the pools itself reconfigured, in order to meet new constraints.

Also with regard to the possibility of efficient data sharing between components of a virtualized system new possibilities emerged. The problem of efficient information exchange between VMs can be tackled by shared memory systems which are based upon granting mechanisms (see Section 2.1.5.2). This way, a VM can explicitly offer parts of its memory (typically at page granularity) to other VMs and set the operation flags to the desired access level.

Yet the main point of criticism addresses I/O operations. Traditionally, virtualized systems maintain isolation properties at the cost of at least one extra copy operation. From the perspective of embedded systems using single address space shared buffers with simple synchronization primitives, this seems inefficient. We want to point out two approaches that help to mitigate the problem for virtualized systems without sacrificing isolation properties.

The first is the hardware extension IOMMU, which provides secure virtual machine guest operating system access to selected I/O devices by safely remapping guest-physical addresses to host-physical addresses. This extension enables the socalled pass-through technology for passing or dedicating devices to VMs.

The second approach is called *Single Root I/O Virtualization* (SR-IOV) [36, 108]. SR-IOV provides additional definitions to the PCI Express specification in order to enable I/O virtualization methods based on PCI Express native hardware. This technology allows a PCIe device to appear as multiple separate physical PCIe devices. The natively virtualized devices are directly accessible to the guests without the involvement of the hypervisor. SR-IOV together with IOMMU can allow for a efficient, secure and scalable device access.

In the end, however, there is no free lunch. At some point, a system designer dealing with these kind of questions will be confronted

with the decision to either partition/dedicate hardware or to adopt some form of multiplexing. Whether classical shared buffers coupled together with simple low level synchronization primitives are better suited than paravirtualization, or the above discussed approaches, has to be decided depending on the given use case and the safety and timing requirements it imposes on the system.

We argue that none of the discussed reservations regarding the adoption of virtualization technology seems to constitute an insurmountable problem. We claim that from the technical point of view, virtualization in embedded and cyber-physical systems is possible and feasible. The next chapters of the following thesis will scientifically substantiate this claim.

#### 1.2 RESEARCH QUESTIONS

Several research questions originate from the idea of integrating CPS by means of virtualization. Those can be roughly divided into two categories: the technological- and methodological issues. Considering the latter, two aspects can be additionally differentiated focusing either on the functional- or on the non-functional properties. Corresponding to these categories, this thesis addresses the following ones:

# • Technological Issues

- Can real-time capabilities of virtual execution environments be improved, so that they meet the strict timing-constrains of CPS?

- Are contemporary high availability solutions via virtual machine replication suitable for improving the dependability of CPS?

### Methodological Issues

- How to adequately model a CPS and include the different non-functional requirements?

- Does a holistic including the execution platform, communication infrastructure and fault-tolerance aspects model exist that allows for the planning of safe and efficient virtual execution environments?

- How to test virtualized CPS applications during development?

- How to consider the complex and interwoven dependencies between the execution platform, communication infrastructure and the physical world in the process of verifying the functional correctness of the CPS application?

#### 1.3 SCIENTIFIC CONTRIBUTIONS

The scientific contributions of this thesis address the research questions stated in the previous section. In detail, this work advances the state-of-the-art by the following contributions:

# • Technological Issues

- In order to enable the execution of time-constrained virtualized CPS applications, we analyze the architecture of Xen [10] a popular, performant and open-source *Virtual Machine Monitor* (VMM) identify its shortcomings with respect to real-time capabilities and extend it with a suite of real-time schedulers [69].

- To solve an issue of priority inversion during network packet processing, we introduce an architecture that synergizes the work of the VMM-scheduler with I/O-scheduling [69].

- To facilitate scheduling [69] and analysis [63] as well as an efficient high availability solution [62], we propose and evaluate the utilization of *unikernels* as guest *Operating Systems* (OS).

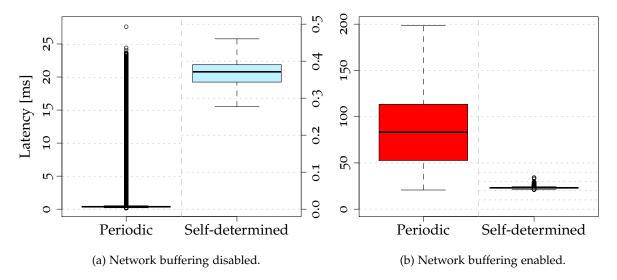

- In order to increase the dependability of virtualized CPS, we propose a novel approach to high availability and present a *self-determined* virtual machine replication model that reduces latency costs by an order of magnitude when compared with state-of-the-art techniques [62, 68].

## Methodological Issues

- We propose a methodology for the planning of safe and efficient virtualized execution environments which aim at hosting time-constrained virtual machines [63]. To this end, we combine evolutionary algorithms with formal system performance analysis in particular algorithms considered in classical scheduling theory. We show that such an approach allows to optimally dimension the execution environment and at the same time provides strict guarantees regarding the timing predictability of an integrated CPS.

- We present a hardware-in-the-loop (HiL) Hardware-in-the-Loop (HiL) co-simulation architecture for the development and testing of virtualized CPS applications [64].

- Based upon application requirements from the smart grid domain, we describe how the complex dependencies between the *Information and Communication Technologies* (ICT) and the electric power system can be taken into account during application development and verification [64, 65].

- Software Contributions: CPS-Xen and CPS-Remus

- We developed CPS-Xen with CPS-Remus. A virtual execution environment for a dependable and efficient hosting of virtualized CPS applications. It is based upon the Xen-Hypervisor and implements the above listed scientific contributions related to the architectural aspects. CPS-Xen was used as the evaluation platform for obtaining the results presented in this thesis. For reasons of openness and reproducibility of the presented results, the entire source code is available for download on our GitHub project page<sup>1</sup> [27]. The software stack also includes all of the extensions made by us to the MiniOS-Unikernel.

#### 1.4 CONTRIBUTIONS OBTAINED IN COOPERATION

In accordance with §10(2) of the PhD regulations of the department of computer science, TU Dortmund, 2011, for all results presented in a thesis, which were obtained in cooperation, an additional list has to be provided that separates the author's own contributions. A separate acknowledgment has to be given to my advisor Prof. Dr.-Ing. Olaf Spinczyk who contributed advice, ideas and technical comments to all publications presented in this thesis.

- Chapter 4: This chapter concerns the methodology of planning safe and optimally dimensioned virtual execution environments for CPS applications. My contribution is the idea and the design of the proposed methodology as well as the concept for evaluation. I am also the principal author of the publication that presents the obtained results [63]. This contribution was achieved in cooperation with Ulrich Gabor and is based upon his master thesis, which I supervised.

- Chapter 5: The fifth chapter describes an architecture for developing and testing of CPS applications. This architecture was developed in cooperation with Markus Küch and is partially based upon his master thesis. We published the results with me as the principal author in [64]. My contribution to these results is the overall concept of the presented architecture which conjoins a co-simulation approach from the master thesis with my virtual execution platform. Furthermore, I contributed the implementation and evaluation parts that are related to virtualization technology.

<sup>1</sup> https://github.com/cpsxen/cps-xen

#### 1.5 THESIS STRUCTURE

This thesis is structured as follows:

- Chapter 2: *Background* (pages 11-26)

The second chapter provides background information that facilitates the understanding of the scientific contributions presented in this thesis. It introduces basic notions from the area of virtualization technology and briefly discusses different approaches to system performance analysis. Further, it also provides related work for the topics presented in this chapter. In-depth literature that is directly related to our contributions is being discussed in corresponding chapters and sections.

- Chapter 3: Virtualized CPS-Architecture (pages 27 70)

This chapter describes the architecture of our virtual execution environment, it discusses the technological aspects related to its infrastructure software and presents our scientific and software contributions in this area.

- Chapter 4: *Planning Virtualized CPS* (pages 71 92)

The fourth chapter presents a methodology for the construction and integration of safe and efficient cyber-physical systems by means of virtualization. It describes the necessary techniques, the corresponding models and discusses how system designers and administrators can benefit from this approach.

- Chapter 5: *Testing of Virtualized CPS* (pages 93 104)

The fifth chapter proposes architectures for the verification and testing of virtualized cyber-physical systems, including the applications as well as the underlying computer hardware and field devices.

- Chapter 6: Discussion and Outlook (pages 105 110)

This chapter discusses the topic of safety certifications as well as analyzes the potential requirements of future CPS applications.

Based on this analysis, it provides an outlook in form of a generic execution platform architecture for emerging CPS applications.

- Chapter 7: *Summary and Conclusion* (pages 111 114)

The last chapter summarizes and concludes this thesis.

- Appendix a: Numerical Evaluation Results (pages 115 116)

The seven chapters are succeeded by an appendix presenting the full results of the experiments comparing the CPS-Xen RM and RT-Xen RDTS schedulers in Section 3.3.4.

This chapter provides background information with respect to virtualization technology and system performance analysis. We refrain from an exhaustive and in-depth description of those fields, as this would go beyond the scope of this thesis. Therefore, in the following sections, the aforementioned research areas are being presented to an extend that is necessary for the understanding of the scientific contributions described in this work.

#### 2.1 VIRTUALIZATION TECHNOLOGY

This section begins with a brief historical perspective and definitions with respect to virtualization. Next, in order to provide a context for our findings, we discuss different types of execution environments. The discussion is being followed by the introduction of the technique of *platform virtualization*. After presentingplatform virtualization, the architecture of the Xen hypervisor – including its high availability solution Remus – are being discussed. The section concludes with information regarding *unikernels*.

# 2.1.1 A Brief Historical Overview

The idea of virtual machines has its origins in the 1960s, in the so-called mainframe era. At that time, mainframe computers were expensive machines. Institutions and companies were searching for means that would allow multiple users to simultaneously share a common hardware platform. A pioneer system that met these requirements, by implementing the concept of a time-sharing operating system, was presented in 1962 [26]. It was developed at Massachusetts Institute of Technology's Computation Center and called the Compatible Time-Sharing System (CTSS) . Few years later, the IBM company took the time-sharing concept to a new level by developing a revolutionary architecture that could simultaneously run multiple instances of an operating system by using virtualization. The Control Program/Conversational Monitor Systems (CP40/CMS) [1, 28] was able to create fourteen virtual IBM System/360 environments - virtual duplicates of real System/360 machines. The CP was responsible for the creation and management of virtual machines, while CMS was a lightweight singleuser operating system that was developed before CP existed and originally aimed at the evaluation of modularization concepts in system evolution [28]. In contrast to conventional time-sharing systems, which divided the computer resources between multiple users, the CP provided each user with an emulated stand-alone computer. Several releases followed and soon the CP/CMS were able to host dozens of OS's and time-sharing users. The CP/CMS architecture was revolutionary as it established a novel technological paradigm. All contemporary virtualization solutions are descendants of this architecture.

Even though virtualization technology started with the idea of abstracting mainframe resources, it became relatively quickly clear that beyond resource partitioning virtualization also provides the means to solve a variety of problems when it comes to compatibility in a broad sense. As a consequence, the concept of virtualization was also adopted by other areas, among them to compilers, operating systems and programming languages.

To date, 50 years after the invention of this technology, plenty of virtualization types emerged. The most important ones are: application, network-, desktop-, operating system-, and platform virtualization. Even if not always fully aware, most of us use one or multiple forms of virtualization every day.

# 2.1.2 What Is Virtualization Technology?

A good way to explain the concept of virtualization is by using another concept, the emulation. Emulation and virtualization are to some degree similar. Virtualization can even be interpreted as an extension of emulation. In fact, for many virtualization techniques emulation is an enabling technology. What they have in common is that both create logical representations of hardware. The main difference lies in the scalability. While with emulation one system can imitate a behavior of another system, virtualization is able to simultaneously support, on a single machine, an arbitrary number of different systems.

Another way to describe virtualization is by means of interfacing [124]. When a component is being virtualized, an additional layer of indirection is being added for the accessing of its resources. In the process, this interface, and the resources visible through this interface, are being mapped onto the interface and resources of the real component. By this, the real component (or an entire system) can appear as one or multiple different ones.

Finally, virtualization can also be defined as an isomorphic relation between a *guest* and a *host*, and the process of virtualization as the construction of such an isomorphism [111]. More formally, it is a mapping which satisfies the condition that for a sequence of operations, which modify the state of a guest, a corresponding sequence of operations exists on the host, which perform an equivalent transformation of its state. Readers interested in a more detailed description of formal definitions with respect to virtualization, are referred to the publication of Popek and Goldberg [111].

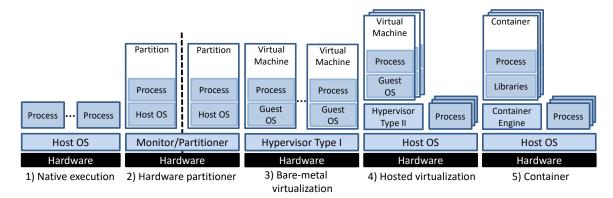

Figure 2.1: Types of execution environments.

In computer science, a common practice for solving complexity issues is to introduce abstraction layers that are separated by interfaces. It helps to ignore implementation details and to concentrate on higher level functionalities. In a way virtualization embeds this approach, yet besides facilitating design and management, it also provides the means for a relaxation of resource constraints and the solving of compatibility issues. This is why there exist virtualization solutions for any level of a system architecture, including both hardware- and software components.

In order to focus the discussion and define a context for the findings presented in this dissertation, before we proceed with the discussion of platform virtualization, the next section provides basic notions with respect to types of execution environments. For an exhaustive description of the virtualization technology as such, please refer to Smith and Nair [124].

#### 2.1.3 Types of Execution Environments

Figure 2.1 depicts architectures for different types of execution platforms, which are being discussed in contemporary literature and press articles in the context of virtualization and efficient service or application development and deployment.

*Native execution* (1) represents platforms that run software – more or less – directly on hardware for which this software was specifically implemented for. In other words, this architecture represents non-virtualized execution environments.

Hardware or system partitioners (2) provide system-wide hardware isolation for software. They are being used to host bare-metal applications or operating systems directly on the hardware without any additional abstraction layer. The possibility of resource or device sharing is limited and mostly only hardware-based. Examples of partitioners are the *ARM Trusted Firmware* (ATF) <sup>1</sup> and *Jailhouse* [115]. The former is

<sup>1</sup> https://github.com/ARM-software/arm-trusted-firmware

a reference implementation of the *ARMs TrustZone* technology <sup>2</sup>. It divides the hardware of the system in two environments, the so-called secure world, aiming at hosting safety and security sensitive workloads, and the normal or less trusted world. The latter – *Jailhouse* – is a lightweight real-time static partitioner for multicore platforms based on Linux.

The software for creating logical abstractions of hardware as well as instantiating and running virtual machines is called *Virtual Machine Monitor* (VMM) or *hypervisor*. Traditionally, hypervisors running directly on the hardware are being referred to as *bare-metal* or *type-1* VMMs (3) [46]. Beside hardware partitioners, hypervisors provide the strongest isolation properties by leveraging dedicated hardware virtualization extensions. They also provide an advanced and rich set of features with respect to resource and device sharing. Most prominent examples of bare-metal hypervisors are *Xen* [10], *VMware ESXi* or *Microsoft Hyper-V*. A special case represents the *L4Re Microkernel*, a microkernel-based operating system framework with support for type-1 virtualization yet with a split functionality between the hypervisor and the user-space based VMM. It is based on the Fiasco.OC microkernel [110] from the L4 microkernel family [52].

VMMs running on top of a host operating system are being referred to as *type-2* or *hosted* VMMs (4), as they coexist with other programs executed under the host operating system. In this architecture, the created virtual machines run as processes on the host operating system. Two popular type-2 hypervisors are *Virtualbox* and *VMware Workstation Player*. A special case constitutes the *Kernel-based Virtual Machine* (KVM) [74] hypervisor. There is a discussion on how to classify KVM. On the one hand, VMs under KVM run as regular Linux processes and thus rely on the host OS. On the other hand, the KVM module turns the Linux kernel into a hypervisor that closely resembles a type-1 VMM.

Finally, an execution environment that is currently gaining enormous traction are *containers* (5). Containers are instances of user-space software packages isolated and run by a single kernel. They hold assets like libraries, files and other dependencies that are necessary for the encapsulated applications or system to run. The *containerization* approach is also being referred to as *operating-system-level virtualization* or *lightweight virtualization*. Containers facilitate the development and deployment of services by abstracting code from infrastructure, simplifying configuration as well as enabling scalability and portability. Popular examples of container engines are LXC [84] – for system containerization, and Docker [34] – for application containerization.

In the following section, we will discuss the concept of platform virtualization – as well as the enabling techniques – in more detail as it forms the basis for the results presented in this dissertation.

<sup>2</sup> https://developer.arm.com/technologies/trustzone

## 2.1.4 Platform Virtualization

The form or type of virtualization can be determined based on where in a system architecture the virtualization software is located. In the case of platform virtualization, the virtualization interface is placed between the *host* and the *guest*. With regard to terminology, the underlying hardware of a machine is usually being referred to as a *host* and the executing software – the operating system including the encapsulated applications – as a *guest*. Both bare-metal as well as hosted virtualization enable platform virtualization. However, as type-1 VMMs reduce one layer of indirection and give the hypervisor an exclusive control over the hardware, they are – in respect of efficiency and security – the preferred technology for implementing platform virtualization.

The major feature of platform virtualization is the ability to support the execution of multiple different OS simultaneously on a single hardware. To this end, the virtualization layer has to provide a complete system environment (CPU, memory, I/O) to all of its guests. In order to facilitate this, the virtualization software has to multiplex the existing physical resources among the running guests. This is done by the VMM. The VMM manages all hardware resources of the underlying host platform and traps privileged accesses in order to verify their correctness. Normally, the guest software is unaware of this indirection. Note that not all of the virtual hardware presented to the guests has to be available on the physical host. The virtualization software can embed emulation in order to provide the desired resource.

In literature, *platform virtualization* is sometimes being referred to as *system virtual machines* [124] – as it aims at providing system replication. Another term is *server virtualization*. This term originates from the great popularity of this virtualization form in the server domain. Connected to this popularity is the computer architecture that is most commonly being virtualized, the x86 architecture. Since decades, this architecture is widespread and very popular. Ironically, it is one of the more difficult architectures to virtualize. The issue resides in the concept of privilege levels, known as rings, of the x86 architecture and a set of seventeen nonvirtualizable instructions [117]. Nonetheless, its popularity made it a very attractive target and a lot of effort has been put into overcoming the limitations of this architecture in respect of virtualization. In the following, a description of the popular solutions enabling platform virtualization on x86 is provided.

# 2.1.4.1 Binary Translation

*Binary translation* [98, 123] or *binary rewriting* is a technique for detecting and patching the set of problematic instructions – the non-trapping sensitive instructions – on the x86 architecture. As those instructions have to be emulated, the VMM dynamically analyzes the instruction

stream, identifies the ones that have to be substituted and rewrites them so that they produce the intended effect. As a consequence, most of the code of the guest can be executed in user space. The obvious downside of this approach is the additional indirection that imposes a performance penalty, especially in the case of intensive I/O operations. Binary translation was popularized by VMware. VMware refers to its platform virtualization solution that combines binary translation and direct execution of instructions as full virtualization. However, this seems disputable as in a traditional sense full virtualization translates to providing the guest with an interface to the full system architecture – the *Instruction Set Architecture* (ISA) . The virtual hardware exposed to the guest is typically functionally identical to the underlying hardware. For example, this was the case with the IBM System/370 which had a total commonality between the ISA of the virtual machine and the real machine [121].

# 2.1.4.2 Paravirtualization

The paravirtualization technique [10, 132] takes a different approach. Instead of dealing with the emulation of the problematic instructions, it bypasses them, respectively, delegates their execution. This is done by exposing a virtual machine interface to the guest that is similar but not identical to the underlying hardware. In the case of the most prominent embodiment of the paravirtualization technique, the Xen hypervisor [10], the guests are being presented with a hypercall Application Programming Interface (API). Hypercalls are conceptually similar to system calls. Through this interface the OS can delegate the execution of privilege instructions to the VMM and thus significantly reduce the virtualization overhead. The downside of this approach is that using the hypercall-API requires a modification of the guest OS kernel. Although no changes to the *Application Binary Interface* (ABI) are necessary and therefore no modifications the guests application code are needed. A significant part of the evaluation results presented in this thesis are linked to this form of platform virtualization.

### 2.1.4.3 Hardware-assisted Virtualization

The notion *hardware-assisted virtualization* denotes a class of hardware enhancements that aim at improving the execution performance of virtual machine environments. The first to implement such extensions was IBM. IBM introduced additional hardware to their System/370 machines, in order to assist the VMM in instruction emulation. In respect of the x86 platform, in 2005 and 2006, Intel and AMD added a set of new instructions that facilitates virtualization on x86. These technologies are called Intel VT-x and AMD-V, respectively. In 2010, also ARM announced architectural support for virtualization and released, in 2011, first CPUs with this feature. Depending on the solution the

implementation details may vary, though conceptually they are similar. All three extensions introduce an additional mode of operation. This allows the hypervisors to be executed in an extra privileged mode, while the guest OS is able to execute with its traditional OS privileges (within ring o on x86 or supervisor mode on ARM). In the context of Xen, this virtualization form is called *Hardware Virtual Machine* (HVM). The advantages of HVM are faster transitions for system calls and – when compared with paravirtualization – the support for unmodified operating systems. Introducing this mode theoretically removes the need for either paravirtualization or binary translation. However, there are also some trade-offs. HVM innately does not provide virtual devices. Those have to be emulated, along with BIOS, timers and interrupts. The cost of this is performance. At least this was the case with the first generation of hardware-assisted virtualization extensions where only features regarding CPU virtualization were provided.

# 2.1.4.4 Hybrid Virtualization

Since 2006, manufacturers extended hardware assistance for virtualization by iteratively adding new features. The introduction of nested paging or Second Level Address Translation (SLAT) allows the hypervisor to take advantage of hardware supported translation from pseudo-physical or real-memory addresses to machine addresses. Prior to that, this mechanism had to be implemented in software – for example using the shadow page tables [124] concept. Beyond memory virtualization, another important extension concerns with I/O virtualization. Through the remapping of *Direct Memory Accesses* (DMA) and interrupts, the Input/Output Memory Management Unit (IOMMU) allows guests to use devices directly – without the intervention of the hypervisor. In order to take advantage of hardware assistance, hypervisors are trying to incorporate guest support for those features. An approach that combines both the software- and hardware solutions is often being called hybrid. Such an approach seems only natural, as it combines the best of both worlds. Eventually, hardware assistance will replace all need for software assistance. However, in respect of Xen, compatibility issues still exist and a comprehensive and stable software support is still being in development.

# 2.1.5 The Xen-Hypervisor

The results presented in this dissertation are linked to the Xen-Hypervisor [10]. There are several reasons why we have originally chosen Xen as the target platform to evaluate our research:

First, Xen is an efficient platform virtualization solution. Due to the technique of paravirtualization, Xen provides low-latency I/O processing, which is of high importance for CPS. Next, even though Xen does not include device drivers itself, it instantiates a privilege guest

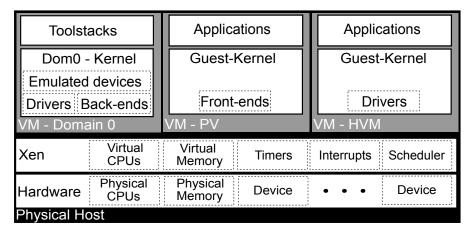

Figure 2.2: The Xen architecture with a simple configuration of one paravirtualized (PV) and one fully virtualized guest (HVM).

(called Domain 0 or Dom0) that facilitates device utilization for guests. Domain 0 typically runs the Linux operating system – although Solaris or NetBSD are also supported. By leveraging Domain 0, Xen indirectly supports all drivers available for the Linux operating system. Moreover, when porting a new operating system to Xen, it is not necessary to implement a myriad of drivers and repeat work that has already been done by others. For this purpose, Xen provides an abstract and simplified interface to devices – the *split device driver model*, which will be described later in this chapter. Besides x86, Xen also supports the ARM architecture, a predominant platform for embedded- and cyber-physical systems – two domains where virtualization technology is gaining significant interest. Furthermore, at the time of decision, Xen was the only VMM to provide a relatively efficient *High Availabil*ity (HA) solution [30]. Finally, the Xen hypervisor is an open-source project. This significantly facilitates research, as all parts of its software architecture are open to adaptation and extension.

#### 2.1.5.1 The Architecture of Xen

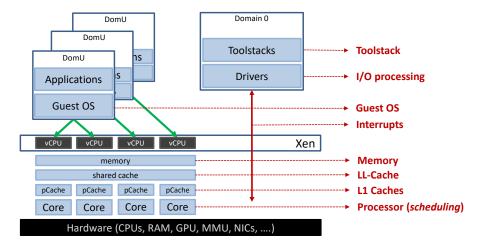

The physical host, illustrated in Figure 2.2, represents a server which deploys the Xen hypervisor. Xen runs directly on the host's hardware and is the first software to execute after the system leaves the bootloader. The hypervisor is responsible for managing hardware resources, including the CPUs, memory and interrupts. Further, it also handles timers as well as the scheduling of VMs.

After setting up all of the required software structures, Xen boots a privileged guest – Domain 0 (*Dom*0). Dom0 is always the first domain to load under Xen, as it holds the drivers for the underlying hardware devices. Beside some xen-specific infrastructural software, this is also were Xen's management API resides. The Xen API (not to be confused with the hypercall-API used by the guest's kernels) is being utilized

by different toolstacks (most popular being the *xl-toolstack*) in order to provide user space VM management functionalities for administrators.

Figure 2.2 also depicts two additional domains: one *Paravirtualized* (PV) guest and one fully virtualized HVM guest. In contrast to Dom0, these domains are restricted (e.g. are not allowed to access hardware directly) and are therefore also called *unprivileged domains* (DomU) in Xen. Both guests encapsulate an operating system and some applications. However, due to the different virtualization form, they differ in way they access hardware devices. The PV guest makes use of the Xen's split device driver – to be more precise it implements the *front-end* part of this model. In contrast, the HVM guests uses conventional drivers provided by its operating system while Xen emulates the corresponding devices. To this end, Xen utilizes the well-known open-source *Quick Emulator* (QEMU).

In the following, we will discuss the split device driver model in more detail as it provides a good illustration of Xen's overall paravirtualization approach.

# 2.1.5.2 The Split Device Driver Model

The motivation for the split device driver model is – besides omitting the x86 virtualization issues – to make use of the already existing drivers in Dom0. However, as not all hardware devices are designed to cope with multiple access, some form of multiplexing has to be provided. In this regard, Xen mimics the approach encountered in operating systems. Operating systems provide different software abstractions, in order to facilitate hardware access for processes. For VMs, an analogous service is being provided by the split device driver.

The split device driver is composed of components which are the backbone of Xen's paravirtualization approach: the *grant tables* – a generic mechanism for sharing memory between domains, *events* – a concept of software signals and interrupts, and the *XenStore* – a hierarchical, tree-like transactional key-value data structure for exchanging configuration information between domains. The keys denote a path in the tree and the values store domain information. The driver itself consists of two parts: the *front-end* and the *back-end*. Both parts are isolated, the back-end typically resides in Dom0, whereas the front-end is located in DomU. Now, how do those elements all fit together?

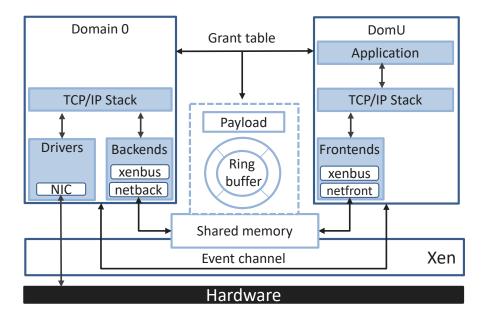

Figure 2.3 exemplifies the architecture of the split device driver for the network driver. Suppose a guest domain wishes to send out a network packet. In order to do that it has to fulfill the following requirements.

First, the guest domain needs a virtual device – in this case one that represents a network card. Analogues to the driver, this device is split into two parts. One resides in DomU and is bound to the front-end driver (*netfront*), the other is typically located in Dom0 and connects to the back-end part (*netback*).

Figure 2.3: The Xen split device driver model exemplified for networking.

Next, using the grant table mechanism, DomU has to dedicate memory for inter-domain communication. On top of the shared memory segments it has to instantiate a ring buffer – a data structure for the realization of the producer-consumer communication model. The ring buffer is being filled with requests and responses that contain instructions, e.g. a *grant reference* to the granted page. Data (*payload*) is transmitted elsewhere, and for this purpose, DomU has to share additional pages which then are to be referenced within the instructions. Finally, in order to deliver the asynchronous request and response notifications, a communication channel has to be established between the two domains. To this end, both domains bind to a dedicated *event channel*. In contrast to interrupts, these channels are bidirectional and connection-oriented. The IDs of the channels are being announced through the XenStore.

After setting up the required infrastructure, DomU can insert data into the granted shared memory pages, enqueue a corresponding request in the ring buffer and notify – through the dedicated event channel – Dom0 that there is a packet pending. Dom0 is then able to read the packet and pass it to the appropriate components of the operating system (e.g iptables), in order to deliver it to the real driver.

Readers interested in more details regarding the architecture of Xen are referred to [20].

# 2.1.5.3 Remus - High Availability in Xen

High availability solutions aim at ensuring a continuous operation of a system. A crucial aspect of their efforts relates to the ability of surviving hardware failures. Classical, hardware-based solutions, which involve physically redundant components, are fast and reliable, yet expensive.

Remus [30] – an extension to the Xen hypervisor – takes a different approach. By capitalizing the techniques of VM replication and live migration [23], Remus provides a high availability solution implemented solely in software. In face of hardware failure, it allows a running system to transparently continue execution on an alternate physical host. This process of switching to a redundant source of computation is known as *failover*.

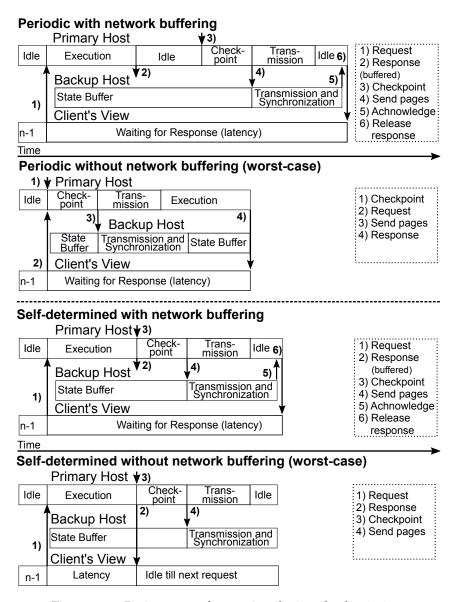

To this end, Remus periodically suspends the execution of the protected guest, captures its state and asynchronously transmits it to a backup host. The captured state is also being referred to as *snapshot* or *checkpoint* while the process of capturing is being called *checkpointing*. Each checkpoint comprises of *dirtied pages*, that is, memory that has been altered since the previous round. Due to the periodic character of the replication process, we refer to this approach as to the periodic checkpointing model. In order to minimize the amount of time in which the protected guest has to remain suspended, Remus allows the guest to resume its execution ahead of synchronization points, that is, without waiting for the backup to acknowledge the receipt of the last checkpoint. This technique is known as speculative execution [104]. The combination of the asynchronous replication and speculative execution allows for an efficient guest protection, especially when compared to the performance penalties induced by the classical approaches to VM replication, e.g. the lock-step [16] technique. However, in contrast to the deterministic lock-stepping approach, Remus cannot guarantee that a restored guest will produce the same output as before a failover.

In order to prevent the impression of inconsistent states between the protected guest and its backup, Remus provides the possibility to buffer output until the state of both VMs has been synchronized. This is, after the backup has acknowledged the receipt of the last checkpoint. Remus refers to this option as *network buffering*. An enabled network buffering option guarantees that an external view on the system will remain coherent – also in the event of a failure. The cost of coherency preservation is latency.

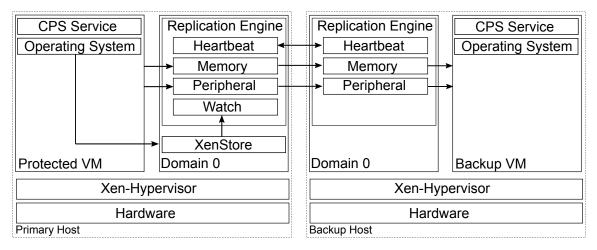

For the purpose of monitoring the availability of a platform, Remus utilizes a heartbeat mechanism. A signal in form of a network packet is being periodically exchanged between the protected guest and the backup guest. In face of failure, the backup identifies the absence of the heartbeat and initiates a failover process. As a result, the service resumes its execution on the alternate host. Note that in the current implementation, there is no mechanism that identifies the failure of a backup host. Only a failure of the master can be detected.

Finally, in contrast to other software-based high availability solutions [35, 116], Remus does not rely on parallel execution. As long as the protected guest is alive, there is only one VM instance of a

service actively running. The backup VM resides in the memory of the backup host, yet its execution is suspended and therefore, it does not consume CPU resources. However, in contrast to solutions adapting redundant execution, Remus is highly demanding in respect of network bandwidth.

Unfortunately, for several reasons Remus is not suitable for protecting CPS applications. In fact, to the best of our knowledge, there exists no virtualization-based approach to high availability that fits the needs of the CPS domain. The current techniques are either inadequate or inefficient. The further elaboration of this assessment is provided in Chapter 3 together with the proposal and discussion of a novel model for high availability that avoids the drawbacks of the established techniques.

#### 2.1.6 Unikernels

In the context of platform virtualization, it is common practice to employ general-purpose operating systems for guests. Those provide a lot of functionality, ease the deployment of common services or legacy software and are accessible not only to experts. However, fully functional operating system are demanding in terms of resources. In fact, in most cases, to perform a task of interest they consume significantly more resources than actually necessary. Nevertheless, in data-center or cloud environment domains, such an approach is being accepted as it does not interfere with the fulfillment of the functional requirements of commonly deployed services. It does, however, translate into cost issues and efforts are being made to reduce the generated overhead.

In contrast, in the domain of CPS, where functional requirements are often as critical as non-functional requirements, such an inefficiency will not only result in a waste of resources but it can also lead to a system failure. This is due to the fact that the generated overhead negatively impacts crucial system properties like timeliness or availability.

Regarding the former, in order to guarantee a wide spectrum of functionalities, general-purpose OS's instantiate a lot of additional processes of which most of them are not related to the service of interest. The instantiated processes – even if properly isolated by means provided for this purpose by the OS – still interfere with the execution of the service in question. This negatively impacts the service timing predictability.

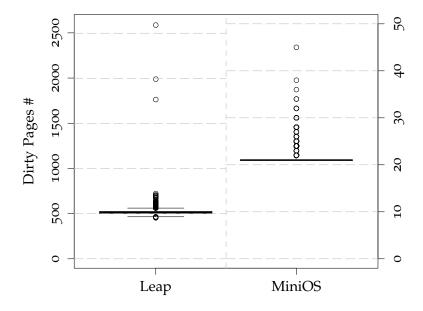

Considering the latter, the memory overhead generated by processes that are not service related also induces an adverse impact on the efficiency of high availability solutions. During VM replication all of the modified pages have to be transferred to the backup host. This also includes the pages that were altered by processes that are not service related. Even in the case of lightweight Linux distributions aiming at

virtual appliances, due to this phenomena, the unnecessary increase in checkpoint size can be in average amounted to 2 MB [68].

Finally, the deployment of dedicated services embedded in generalpurpose operating systems also poses serious security risks – both in the case of CPS as well as cloud environments. For the aforementioned reasons, a rationalization of the deployment process seems in order.

In fact, in recent years successful efforts have been made to increase the resource efficiency of service deployment in virtual environments. These efforts are based upon the concept of Library Operating Systems (LibOS) [40, 42, 86]. LibOS's allow to optimally adapt the required OS code base to the particular needs of an application. For each application only those parts of the OS API are being implemented, and later on compiled into a VM image, on which the application actually depends. This way, sealed against modifications, single-purpose appliances [90, 91, 94, 112] – also called *unikernels* – can be constructed. Such an approach to application deployment has several advantages. Unikernels have a significantly reduced images size, this minimizes the attack surface for malicious code injection. The fact that no unnecessary services are being executed inside the unikernels additionally increases their security properties. Further, the tailored character of unikernels allows for a substantial reduction of the overall system resource usage. This also translates into increased system performance and, as a consequence, facilitates the fulfillment of non-functional requirements. Finally, due to the fact that unikernels allow for the encapsulation of individual threads into VMs, the hierarchical scheduling model that is inherent to virtualization technology can be flattened, facilitating global scheduling and timing analysis (see Section 3.3.2.1).

Considering these aspects of unikernels, as well as the fact that most CPS applications are specialized and functionally dedicated tasks and can therefore be implemented as single-purpose appliances, CPS applications provide an excellent target for unikernels. This is why, in this thesis, we leverage unikernels for the construction and evaluation of fault-tolerance CPS applications. In particular, we employ and extend MiniOS which is a tiny paravirtualized OS kernel – originally distributed with the Xen project – that serves as the basis for most of the currently available unikernels.

#### 2.2 SYSTEM PERFORMANCE ANALYSIS

Designing virtual execution environments for cyber-physical systems is a daunting task. The problems originate from the intrinsically heterogeneous and distributed character of CPS, the strict non-functional constraints imposed on those systems by the physical environment as well as the technological challenges when virtualizing time-critical applications. Therefore, a successful process of designing, planning or testing virtualized CPS has to rely on methods that are able to

| Empirical methods<br>(Simulating, test,<br>measurement) | State-based verification<br>(Model checking) | Analytical methods<br>(Mathematical system<br>abstractions) |

|---------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------|

| + Large modeling scope                                  | + Exhaustive                                 | + Exhaustive                                                |

| - Not exhaustive                                        | + Accurate (exact)                           | + Fast                                                      |

| (-) Slow                                                | -Slow (state-space                           | - Limited modeling scope                                    |

|                                                         | explosion)                                   | - Limited accuracy                                          |

|                                                         |                                              | - Pessimistic results                                       |

Table 2.1: Approaches to system performance analysis.

quantify relevant system characteristics in a holistic manner, this is, by taking all aspects of the system – as well as its environment – into account. Only by this, a robust evaluation of a virtualized execution platform for CPS can be guaranteed.

In general, the task behind the objective of collecting data that reflects the performance of a system is being referred to as *system performance analysis*. There exist different approaches to system performance analysis, all having their advantages and disadvantages. The choice of an appropriate method always has to depend on the given requirements. In the case of CPS, a fundamental property that an analysis technique has to exhibit is exhaustiveness, that is, the ability to include corner cases, in particular the worst-case scenarios. Otherwise, no guarantees regarding critical system characteristics can be provided.

### 2.2.1 Categories of System Performance Analysis

System performance analysis methods can be roughly divided into the three categories: *empirical-, analytical-* and *state-based verification methods*. Table 2.1 summarizes the properties of the three different classes. The classification is derived from [109].

Simulation-based approaches form the first class. These are established evaluation techniques characterized by a mature tool base. The fact that they offer a large modeling scope, provide accurate results and are relatively easy to adopt renders them popular. However, these methods tend to become slow with increasing model complexity and – what is important in respect of analyzing CPS – they exhibit the inability to satisfactorily cover corner cases. Due to the latter, they fail at providing hard guarantees for lower and upper performance bounds of a system. A mature and popular simulation interface for architectural exploration, performance and system-level modeling is SystemC [45, 81] which has been approved by the IEEE Standards Association as IEEE 1666-2011.

The state-based verification approaches form another category of the performance analysis methods. As the name implies, those depend on a state-based system representation, e.g. timed automaton, as well as a model checker which is being employed in order to verify whether a system model meets a given system property. Similar to the simulation-based approaches, the state-based verification methods have rich modeling capabilities and are being able to model – in detail – any state-related behavior of a system-under-study. As their models comprise complete systems behaviors, the provided evaluation results are exhaustive. Moreover, those are also exact, meaning, the computed performance bounds are not only correct but also precisely accurate. Unfortunately, this class of approaches struggles with state-space explosion which renders it impracticable for the verification of larger systems. A prominent example for these techniques is UPPAAL [12].

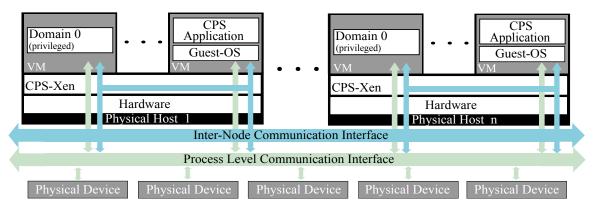

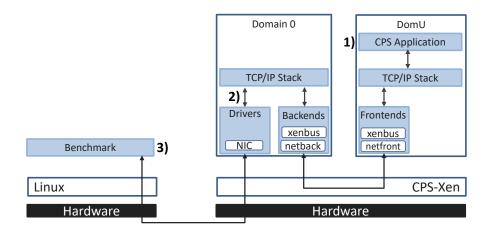

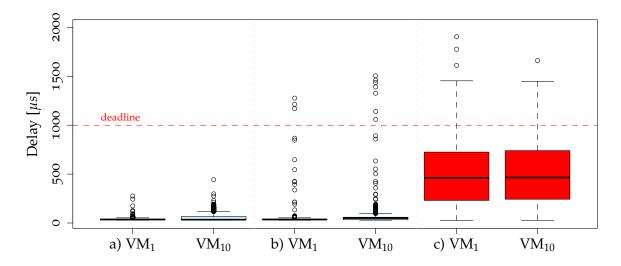

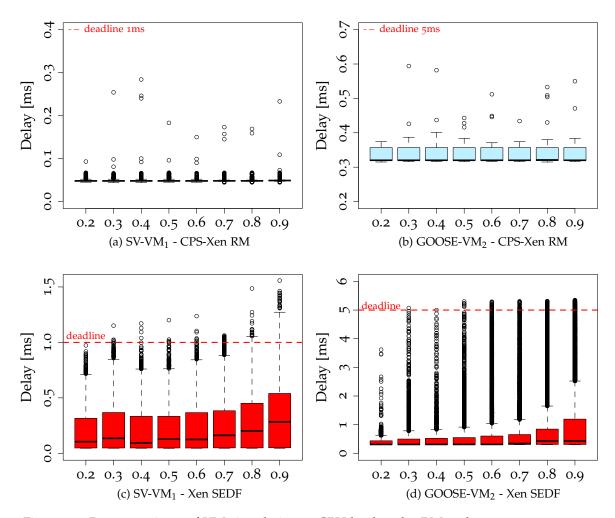

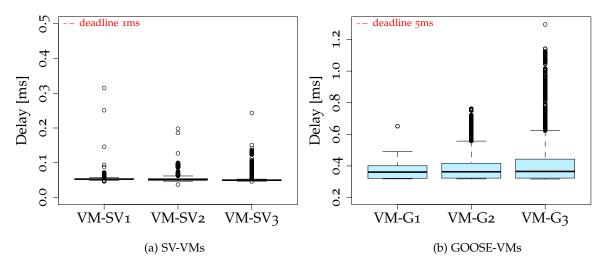

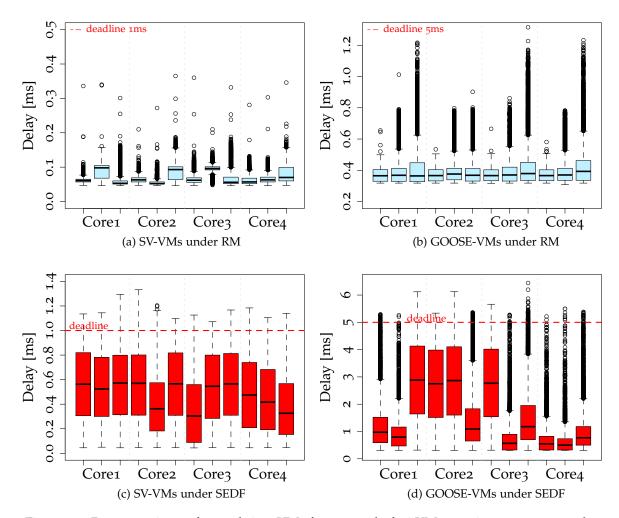

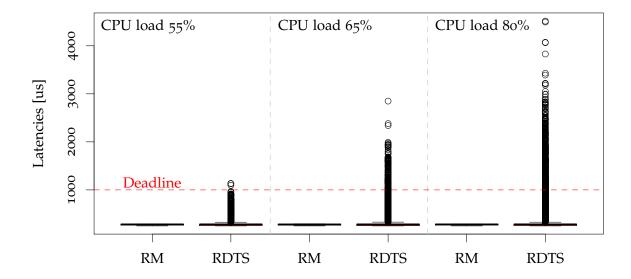

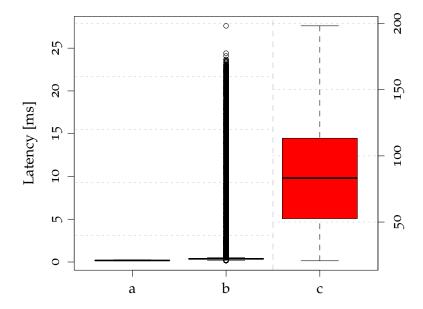

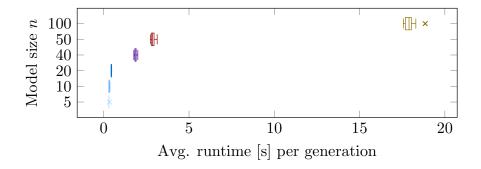

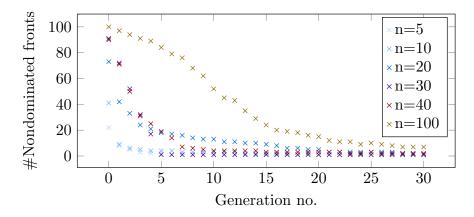

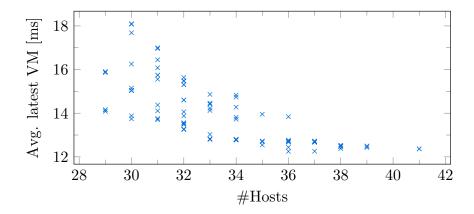

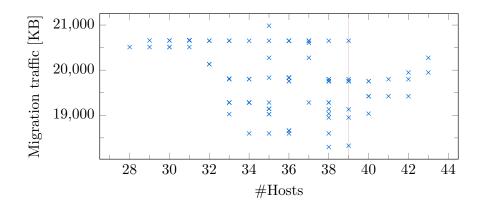

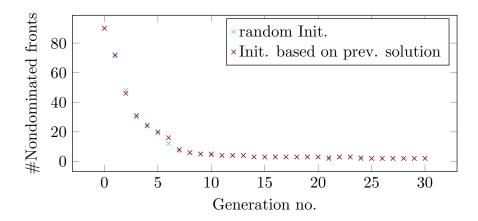

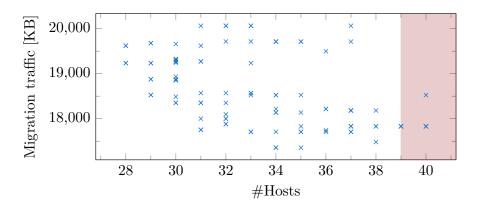

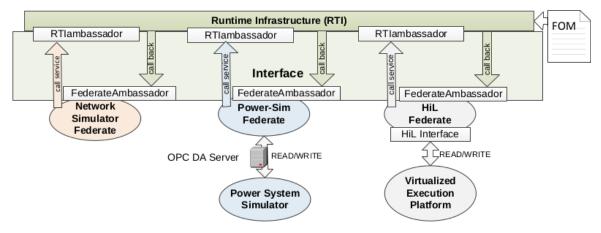

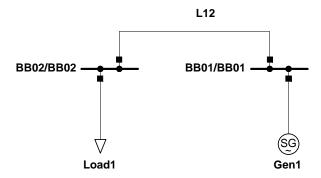

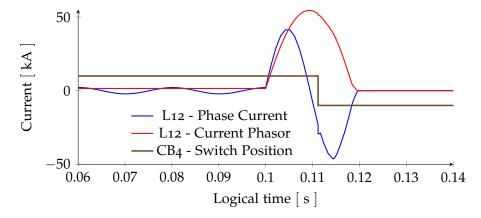

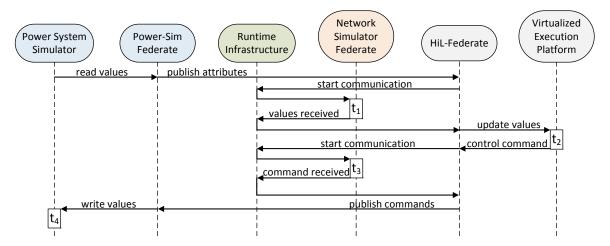

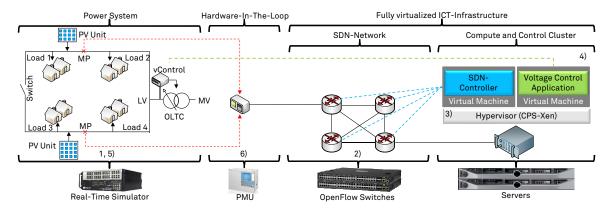

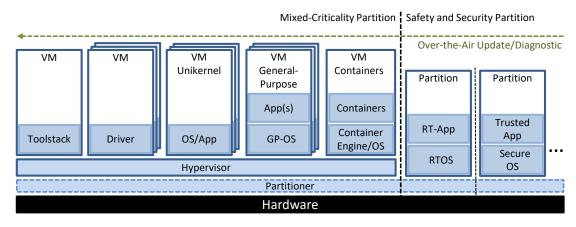

The third category of performance analysis techniques is being represented by the analytical methods. These are based on mathematical formalisms intended to abstract the system in a way that facilitates a quantification of the system's performance characteristics. As a consequence, analytical methods are fast and exhaustive. Moreover, the computed performance bounds can be – in a mathematical sense – proven to be correct. On the downside, analytical methods exhibit a trade-off between the accuracy of the computed results and the modeling scope. In some cases, the analysis of a system is only feasible after the constraints of a mathematical model – the system is supposed to fit in – have been relaxed. Yet, this leads to overly conservative approximations of the performance bounds. Two prominent examples for the analytic approaches are: the *Modeling and Analysis Suit for Real-Time Applications* (MAST) [49, 50] and the *Real-Time Calculus* (RTC) [128].